# SGMCD1030Q Automotive 33-Channel Multiple Switch Detection Interface with Programmable Wetting Current

#### **GENERAL DESCRIPTION**

The SGMCD1030Q provides a low-cost integrated switch detection solution. As a multiple switch detection interface (MSDI) device, it can detect the switch status of up to 33 channels and transfer the switch status information (open or closed) to the microprocessor unit (MCU) through a serial peripheral interface (SPI). In addition, the device features a 35-to-1 analog multiplexer for outputting buffered selected input analog signals to the AMUX pin so that the signal can be read by the MCU.

Several wetting current levels (2mA, 6mA, 8mA, 10mA, 12mA, 16mA and 20mA) are available to be configured, separately. Besides, this device provides the information for battery voltage and IC inner temperature, which can be read by the MCU from the AMUX pin.

The SGMCD1030Q has three modes of operation: normal mode, low-power mode (LPM) and polling mode. When the device is in normal mode, the device can be programmed and can provide the corresponding wetting current to the switch contacts as it monitors the switch status. During low-power mode, the low quiescent current makes the device ideal for applications in automotive or industrial scenarios that require low sleep state current. The polling mode periodically detects the input pins to determine their state and to determine if the state has changed from normal mode.

The device is AEC-Q100 qualified (Automotive Electronics Council (AEC) standard Q100 Grade 1) and it is suitable for automotive applications.

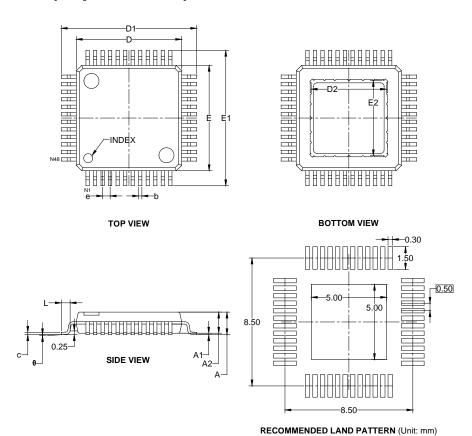

The SGMCD1030Q is available in a Green LQFP-7×7-48AL (Exposed Pad) package.

#### **FEATURES**

- AEC-Q100 Qualified for Automotive Applications

Device Temperature Grade 1

T<sub>A</sub> = -40°C to +125°C

- Fully Functional Guaranteed: 4.5V ≤ V<sub>BATP</sub> ≤ 36V

- Full Parameters Guaranteed: 6.0V ≤ V<sub>BATP</sub> ≤ 28V

- Input Voltage Range of Switch: -1.0V to 36V

- 33 Switch Detection Channels

- 12 Programmable Inputs (Switches to Battery or Ground)

- 21 Switch-to-Ground Inputs with Configurable Pull-Up Current Sources

- 7 Selectable Wetting Current Levels: 2mA, 6mA, 8mA, 10mA, 12mA, 16mA and 20mA

- Programmable Pulse/Continuous Wetting Operation

- Use 3.3V/5.0V SPI Protocol to Communicate Directly with MCU

- Selectable Wake-up during Change-of-Switch State

- Typical Standby Current:

- I<sub>BATP</sub> = 115μA (TYP)

- I<sub>VDDQ</sub> = 4μA (TYP)

- Active Interrupt (INT\_B) on Switch State Changing

- 35-to-1 Analog Multiplexer

- Buffered Output from 33 SGx/SPx Channels

- 1/6 V<sub>SG5</sub> for Battery Voltage Monitoring

- Integrated Die Temperature Monitoring

- Programmable Hardwire AMUX Selection (2 or 3 Bits)

- Available in a Green LQFP-7×7-48AL (Exposed Pad) Package

#### **APPLICATIONS**

Automotive Applications

Zoom Control Unit (ZCU)

Advanced Driver Assistance System (ADAS)

Central Gateway/In-Vehicle Networking

Lighting

Heating Ventilation and Air Conditioning (HVAC)

Gasoline Engine Management

#### PACKAGE/ORDERING INFORMATION

| MODEL      | PACKAGE<br>DESCRIPTION         | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER  | PACKAGE<br>MARKING           | PACKING<br>OPTION   |

|------------|--------------------------------|-----------------------------------|---------------------|------------------------------|---------------------|

| SGMCD1030Q | LQFP-7×7-48AL<br>(Exposed Pad) | -40°C to +125°C                   | SGMCD1030QLFN48G/TR | 1XVLFN48<br>XXXXXYY<br>XX#XX | Tape and Reel, 2000 |

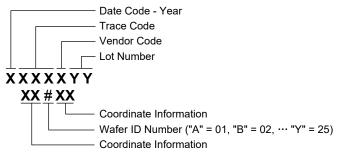

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code. XX#XX = Coordinate Information and Wafer ID Number.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

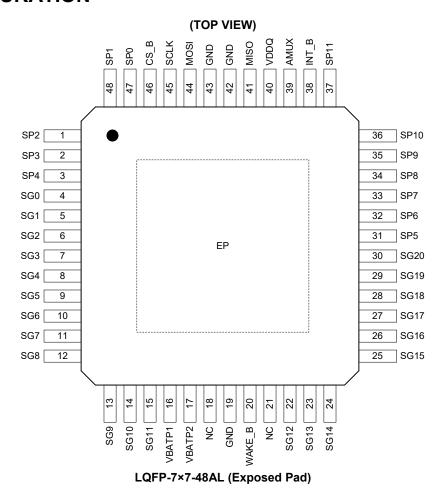

#### PIN CONFIGURATION

# **Automotive 33-Channel Multiple Switch Detection Interface with Programmable Wetting Current**

#### **ABSOLUTE MAXIMUM RATINGS**

| Battery Voltage, VBATP                               | 0.3V to 40V       |

|------------------------------------------------------|-------------------|

| Supply Voltage, V <sub>DDQ</sub>                     | 0.3V to 7V        |

| SPI Inputs/Outputs, CS_B, MOSI, MISO, So             | CLK               |

|                                                      | 0.3V to 7V        |

| SGx, SPx Switch Input Voltage Range                  |                   |

| AMUX, INT_B Voltage                                  | 0.3V to 7V        |

| WAKE_B Voltage                                       | 0.3V to 40V       |

| Package Thermal Resistance                           |                   |

| LQFP-7×7-48AL (Exposed Pad), $\theta_{JA}$           | 22.6°C/W          |

| LQFP-7×7-48AL (Exposed Pad), θ <sub>JB</sub>         | 7.1°C/W           |

| LQFP-7×7-48AL (Exposed Pad), θ <sub>JC (TOP)</sub> . | 18.7°C/W          |

| LQFP-7×7-48AL (Exposed Pad), $\theta_{JC (BOT)}$ .   | 1°C/W             |

| Junction Temperature                                 | +150°C            |

| Storage Temperature Range                            | 65°C to +150°C    |

| Lead Temperature (Soldering, 10s)                    | +260°C            |

| Contact Discharge <sup>(1)</sup>                     |                   |

| VBATP (2)                                            | ±8000V            |

| WAKE_B (Series Resistor 10kΩ)                        | ±8000V            |

| SGx/SPx Pins with 100nF Capacitor (Seri              | es Resistor 100Ω) |

|                                                      | ±8000V            |

| ESD Susceptibility (3) (4)                           |                   |

| HBM                                                  | ±4000V            |

| CDM                                                  | ±1000V            |

| NOTES:                                               |                   |

#### NOTES:

- 1.  $C_{ZAP}$  = 150pF,  $R_{ZAP}$  = 330 $\Omega$  (Powered and Unpowered).

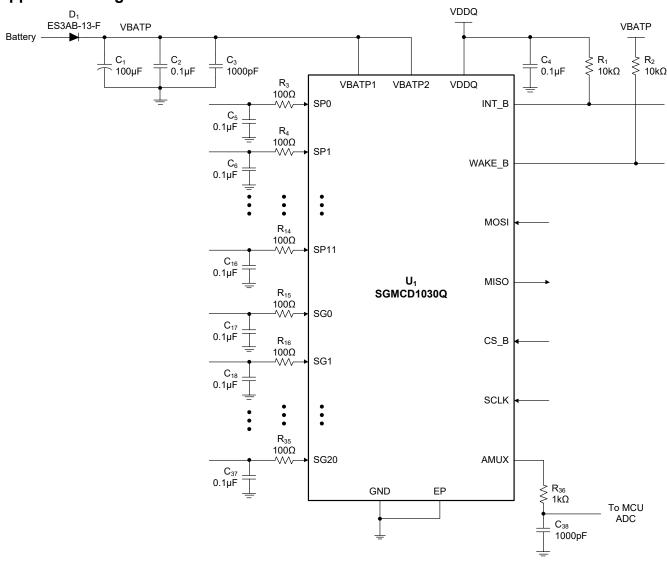

- 2. External component requirements at system level: reverse blocking diode from battery to VBATP (0.6V <  $V_F$  < 1V). See Figure 20.

- 3. For human body model (HBM), all pins comply with AEC-Q100-002 specification.

- 4. For charged device model (CDM), all pins comply with AEC-Q100-011 specification.

#### RECOMMENDED OPERATING CONDITIONS

| Battery Voltage, V <sub>BATP</sub>    | 4.5V to 36V    |

|---------------------------------------|----------------|

| Supply Voltage, V <sub>DDQ</sub>      | 3.0V to 5.25V  |

| SPI Inputs/Outputs, CS_B, MOSI, MISO, | SCLK           |

|                                       | 3V to 5.25V    |

| SGx, SPx Switch Input Voltage Range   | 1V to 36V      |

| AMUX, INT_B Voltage                   | 0V to 5.25V    |

| WAKE_B Voltage                        | 0V to 36V      |

| Operating Ambient Temperature Range   | 40°C to +125°C |

| Operating Junction Temperature Range  | 40°C to +150°C |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

# SGMCD1030Q

# Automotive 33-Channel Multiple Switch Detection Interface with Programmable Wetting Current

# **PIN DESCRIPTION**

| PIN                       | NAME                                  | TYPE  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------|---------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 ~ 3, 31 ~ 37,<br>47, 48 | SP2 ~ SP4,<br>SP5 ~ SP11,<br>SP0, SP1 | I     | Programmable Switch Inputs Pins. All of the 12 inputs can be programmed to either SB or SG.                                                                                                                                                                                                                                                                                                                   |

| 4 ~ 15,<br>22 ~ 30        | SG0 ~ SG11,<br>SG12 ~ SG20            | I     | Switch-to-Ground Input Pins.                                                                                                                                                                                                                                                                                                                                                                                  |

| 16, 17                    | VBATP1,<br>VBATP2                     | Р     | Battery Supply Input Pin. This pin requires an external reverse protection circuit.                                                                                                                                                                                                                                                                                                                           |

| 18, 21                    | NC                                    | _     | No Connection.                                                                                                                                                                                                                                                                                                                                                                                                |

| 19, 42, 43                | GND                                   | G     | Ground for Logic, Analog.                                                                                                                                                                                                                                                                                                                                                                                     |

| 20                        | WAKE_B                                | I/O   | Open-Drain Wake-up Output Pin. It can be used as an enable pin to control external power supply. As an input, it can be used to wake device up from LPM due to external events. When WAKE_B is pulled up to VBATP with a resistor, the recommended resistance value is $10k\Omega$ ; it should not be less than $1k\Omega$ . If WAKE_B outputs low, shorting it to VBATP for a long time may damage the chip. |

| 38                        | INT_B                                 | I/O   | Open-Drain Output to MCU. Used as an indication when the change of switch status occurs. As an input, it can be used to wake device up from LPM due to external INT_B falling events.                                                                                                                                                                                                                         |

| 39                        | AMUX                                  | 0     | Analog Multiplex Output Pin.                                                                                                                                                                                                                                                                                                                                                                                  |

| 40                        | VDDQ                                  | Р     | 3.3V/5.0V Supply Input Pin. Set SPI communication level.                                                                                                                                                                                                                                                                                                                                                      |

| 41                        | MISO                                  | O/SPI | Slave Output and Master Input Pin. Digital data of SGMCD1030Q out pin to MCU.                                                                                                                                                                                                                                                                                                                                 |

| 44                        | MOSI                                  | I/SPI | Master Output and Slave Input Pin. Control Data of MCU input pin to SGMCD1030Q.                                                                                                                                                                                                                                                                                                                               |

| 45                        | SCLK                                  | I/SPI | Clock Input Pin.                                                                                                                                                                                                                                                                                                                                                                                              |

| 46                        | CS_B                                  | I/SPI | Chip Select Input Pin.                                                                                                                                                                                                                                                                                                                                                                                        |

| Exposed Pad               | EP                                    | _     | It is recommended to connect the EP to GND and system ground.                                                                                                                                                                                                                                                                                                                                                 |

NOTE: I = input, O = output, I/O = input/output, P = power, G = ground.

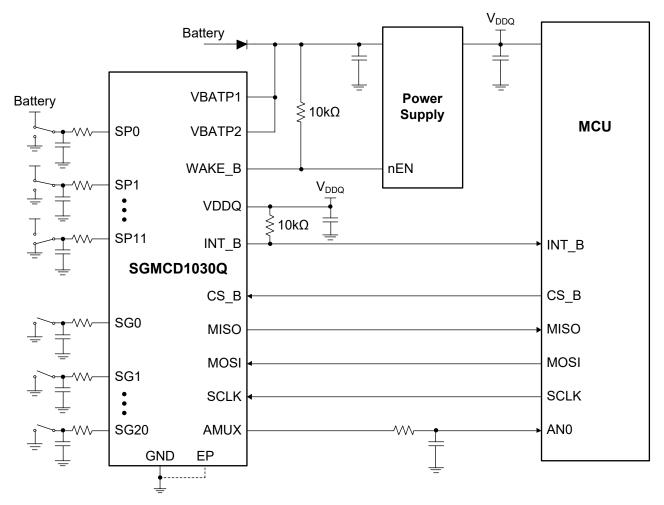

# **TYPICAL APPLICATION**

Figure 1. Typical Application Circuit

# **ELECTRICAL CHARACTERISTICS**

$(V_{DDQ} = 3.1V \text{ to } 5.25V, V_{BATP} = 6V \text{ to } 28V, T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ typical values are measured at } T_A = +25^{\circ}\text{C}, \text{ unless otherwise noted.})$

| PARAMETER                                                  | SYMBOL                     | CONDITIONS                                                                                             | MIN                      | TYP | MAX  | UNITS            |

|------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------|--------------------------|-----|------|------------------|

| Power Input                                                |                            |                                                                                                        |                          |     |      |                  |

| VBATP Supply Power-on Reset<br>Voltage                     | V <sub>BATP_POR</sub>      |                                                                                                        | 2.7                      | 3.3 | 3.8  | V                |

| VBATP Under-Voltage Rising<br>Threshold                    | $V_{BATP\_UV}$             |                                                                                                        |                          | 4.3 | 4.5  | V                |

| VBATP Under-Voltage Hysteresis                             | V <sub>BATP_UV_HYS</sub>   |                                                                                                        | 250                      |     | 500  | mV               |

| VBATP Over-Voltage Rising<br>Threshold                     | $V_{BATP_{OV}}$            |                                                                                                        | 32                       |     | 37   | V                |

| VBATP Over-Voltage Hysteresis                              | V <sub>BATP_OV_HYS</sub>   |                                                                                                        | 1.5                      |     | 3.5  | V                |

| VBATP Supply Current                                       | I <sub>BATP_ON</sub>       | All switches open, normal mode, tri-state disabled (all channels)                                      |                          | 10  | 12   | mA               |

| VBATP Low-Power Mode Supply                                | I <sub>BATP_IQ_LPM_P</sub> | Parametric V <sub>BATP</sub> , V <sub>BATP</sub> = 6V to 28V                                           |                          | 115 | 150  |                  |

| Current (Polling Disabled) (1)                             | I <sub>BATP_IQ_LPM_F</sub> | Functional low V <sub>BATP</sub> , V <sub>BATP</sub> = 4.5V to 6V                                      |                          | 106 | 140  | μA               |

| VBATP Polling Quiescent Current (No Load) (2)(3)           | I <sub>POLLING_IQ</sub>    | Polling rate = 3ms, wake-up enable all channels, All switches open                                     |                          | 62  |      | μΑ               |

| Normal Mode VDDQ Current                                   | I <sub>VDDQ_NOR</sub>      | SCLK, MOSI, WAKE_B = 0V, CS_B, INT_B = V <sub>DDQ</sub> , no SPI communication, AMUX selected no input |                          |     | 165  | μA               |

| Logic Low-Power Mode Supply Current                        | I <sub>VDDQ_LPM</sub>      | SCLK, MOSI = 0V, CS_B, INT_B, WAKE_B = V <sub>DDQ</sub> , no SPI communication                         |                          | 4   | 10   | μA               |

| VDDQ Under-Voltage Falling<br>Threshold                    | $V_{DDQ\_UV}$              |                                                                                                        | 2.2                      |     | 2.9  | V                |

| VDDQ Under-Voltage Hysteresis                              | $V_{\text{DDQ\_UV\_HYS}}$  |                                                                                                        | 140                      |     | 350  | mV               |

| Switch Detection Interface (SG an                          | d SP)                      |                                                                                                        |                          |     |      |                  |

| Switch Detection Threshold (4)                             | V <sub>IC_THR</sub>        |                                                                                                        | 3.7                      | 4   | 4.3  | V                |

| Switch Detection Threshold Low Battery                     | V <sub>IC_THR_LV</sub>     | V <sub>BATP</sub> = 4.5V to 6V                                                                         | 0.55 × V <sub>BATP</sub> |     | 4.3  | V                |

| Switch Detection Threshold<br>Low-Power Mode (SG only) (5) | V <sub>IC_THR_LPM</sub>    |                                                                                                        | 100                      |     | 400  | mV               |

| Switch Detection Threshold<br>Hysteresis (4V Threshold)    | $V_{\text{IC\_THR\_H}}$    |                                                                                                        | 50                       |     | 400  | mV               |

| Input Threshold 2.5V                                       | V <sub>IC_TH2P5</sub>      | Used for Comp Only                                                                                     | 2                        | 2.5 | 3    | V                |

| Switch-to-Ground Input (SG Pins)                           |                            |                                                                                                        |                          |     |      |                  |

| Leakage to GND                                             | I <sub>LEAK_SG_GND</sub>   | Inputs tri-stated, voltage at SGx = 36V, $V_{BATP} = 0V$                                               |                          |     | 2    | μΑ               |

| Leakage to Battery                                         | I <sub>LEAK_SG_BAT</sub>   | Inputs tri-stated, voltage at SGx = GND                                                                |                          |     | 2    | μΑ               |

| SG Sustain Current                                         | I <sub>sus_sg</sub>        | $V_{BATP} = 6V \text{ to } 28V$                                                                        | 1.8                      | 2   | 2.2  | mA               |

| SG Sustain Current LV <sup>(6)</sup>                       | I <sub>SUS_SG_LV</sub>     | V <sub>BATP</sub> = 4.5V to 6V                                                                         | 1.7                      |     | 2.2  | mA               |

|                                                            |                            | Mode 0 = 2mA                                                                                           | 1.8                      | 2   | 2.2  |                  |

|                                                            |                            | Mode 1 = 6mA                                                                                           | 5.4                      | 6   | 6.6  |                  |

|                                                            |                            | Mode 2 = 8mA                                                                                           | 7.2                      | 8   | 8.8  |                  |

| Wetting Current Level                                      |                            | Mode 3 = 10mA                                                                                          | 9                        | 10  | 11   | ] <sub>m</sub> ^ |

| vvetting Current Level                                     | I <sub>WET_SG</sub>        | Mode 4 = 12mA                                                                                          | 10.8                     | 12  | 13.2 | mA               |

|                                                            |                            | Mode 5 = 14mA                                                                                          | 12.6                     | 14  | 15.4 |                  |

|                                                            |                            | Mode 6 = 16mA                                                                                          | 14.4                     | 16  | 17.6 |                  |

|                                                            |                            | Mode 7 = 20mA                                                                                          | 18                       | 20  | 22   | 1                |

| SG Wetting Current Tolerance                               |                            | Mode 0                                                                                                 | -10                      |     | 10   | - %              |

| O Wetting Current Tolerance                                | WET_SG_TOL                 | Mode 1 to 7                                                                                            | -10                      |     | 10   | /0               |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DDQ} = 3.1 \text{V to } 5.25 \text{V}, V_{BATP} = 6 \text{V to } 28 \text{V}, T_A = -40 ^{\circ}\text{C}$  to +125  $^{\circ}\text{C}$ , typical values are measured at  $T_A = +25 ^{\circ}\text{C}$ , unless otherwise noted.)

| PARAMETER                                                                                       | SYMBOL                      | COND                              | ITIONS                        | MIN  | TYP | MAX  | UNITS            |

|-------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------------|-------------------------------|------|-----|------|------------------|

|                                                                                                 |                             | Mode 0 = 2mA                      |                               | 1.7  |     | 2.2  |                  |

|                                                                                                 |                             | Mode 1 = 6mA                      |                               | 5.1  |     | 6.6  | 1                |

|                                                                                                 |                             | Mode 2 = 8mA                      |                               | 6.8  |     | 8.8  | 1                |

| SG Wetting Current Tolerance LV                                                                 |                             | Mode 3 = 10mA                     |                               | 8.5  |     | 11   |                  |

| (V <sub>BATP</sub> 4.5V to 6V) <sup>(6)</sup>                                                   | I <sub>WET_SG_LV</sub>      | Mode 4 = 12mA                     |                               | 10   |     | 13.2 | mA               |

|                                                                                                 |                             | Mode 5 = 14mA                     |                               | 11.4 |     | 15.4 | 1                |

|                                                                                                 |                             | Mode 6 = 16mA                     |                               | 12.8 |     | 17.6 | 1                |

|                                                                                                 |                             | Mode 7 = 20mA                     |                               | 15.5 |     | 22   | 1                |

| Sustain Current Matching between SG Channels (7)(8)                                             | I <sub>MATCH_SUS</sub>      |                                   |                               |      |     | 10   | %                |

| Wetting Current Matching between SG Channels <sup>(9)(10)</sup>                                 | I <sub>MATCH_WET</sub>      |                                   |                               |      |     | 6    | %                |

| Low-Power Mode Polling Current SG                                                               | I <sub>ACTIVE_POLL_SG</sub> | $V_{BATP} = 4.5V \text{ to } 28V$ |                               | 0.65 | 1   | 1.44 | mA               |

| Programmable Input (SP Pins)                                                                    |                             |                                   |                               |      |     |      |                  |

| Leakage to GND                                                                                  | I <sub>LEAKSP_GND</sub>     | Inputs tri-stated, voltage a      | at SPx = 36V, $V_{BATP} = 0V$ |      |     | 2    | μA               |

| Leakage to Battery                                                                              | I <sub>LEAKSP_BAT</sub>     | Inputs tri-stated, voltage a      | at SPx = GND                  |      |     | 2    | μA               |

| SP Sustain Current                                                                              | -                           | \/ = 6\/ to 29\/                  | SP programmed as SG           | 1.7  | 2   | 2.2  | mΛ               |

| SF Sustain Current                                                                              | I <sub>SUS_SP</sub>         | $V_{BATP} = 6V \text{ to } 28V$   | SP programmed as SB           | 1.8  | 2   | 2.2  | mA               |

| SP Sustain Current - LV <sup>(6)</sup>                                                          | I <sub>SUS_SP_LV</sub>      | $V_{BATP}$ = 4.5V to 6V, SP pro   | ogrammed as SG                | 1.7  |     | 2.2  | mA               |

| Wetting Current Level Mode 0                                                                    | 1                           | SP programmed as SG               |                               | 1.7  | 2   | 2.2  | mA               |

| Wetting Current Level Wode 0                                                                    | I <sub>WET0_SP</sub>        | SP programmed as SB               |                               | 1.8  | 2   | 2.2  | IIIA             |

|                                                                                                 |                             | Mode 1 = 6mA                      |                               | 5.4  | 6   | 6.6  |                  |

|                                                                                                 |                             | Mode 2 = 8mA                      |                               | 7.2  | 8   | 8.8  | mA               |

|                                                                                                 |                             | Mode 3 = 10mA                     |                               | 9    | 10  | 11   |                  |

| Wetting Current Level (SG & SB)                                                                 | $I_{WET\_SP}$               | Mode 4 = 12mA                     |                               | 10.8 | 12  | 13.2 |                  |

|                                                                                                 |                             | Mode 5 = 14mA                     |                               | 12.6 | 14  | 15.4 |                  |

|                                                                                                 |                             | Mode 6 = 16mA                     |                               | 14.4 | 16  | 17.6 |                  |

|                                                                                                 |                             | Mode 7 = 20mA                     |                               | 18   | 20  | 22   | ]                |

|                                                                                                 |                             | SG Mode 0                         |                               | -15  |     | 10   |                  |

| Wetting Current Tolerance                                                                       | I <sub>WET_SP_TOL</sub>     | SB Mode 0                         |                               | -10  |     | 10   | %                |

|                                                                                                 |                             | SB/SG Mode 1 to 7                 |                               | -10  |     | 10   | ]                |

|                                                                                                 |                             | Mode 0 = 2mA                      |                               | 1.7  |     | 2.2  |                  |

|                                                                                                 |                             | Mode 1 = 6mA                      |                               | 5.1  |     | 6.6  | ]                |

| Wetting Current Tolerance - LV (V <sub>BATP</sub> 4.5V to 6V) (SG Configuration) <sup>(6)</sup> |                             | Mode 2 = 8mA                      |                               | 6.8  |     | 8.8  |                  |

|                                                                                                 |                             | Mode 3 = 10mA                     |                               | 8.5  |     | 11   | ] <sub>m ^</sub> |

|                                                                                                 | I <sub>WET_SP_LV</sub>      | Mode 4 = 12mA                     |                               | 10   |     | 13.2 | mA mA            |

|                                                                                                 |                             | Mode 5 = 14mA                     |                               | 11.4 |     | 15.4 |                  |

|                                                                                                 |                             | Mode 6 = 16mA                     |                               | 12.8 |     | 17.6 |                  |

|                                                                                                 |                             | Mode 7 = 20mA                     |                               | 15.5 |     | 22   |                  |

| Wetting Current Tolerance - LV (V <sub>BATP</sub> 4.5V to 6V) (SB Configuration) (6)            |                             | Mode 0 to 7 = 20mA                |                               | -10  |     | 10   | %                |

# **Automotive 33-Channel Multiple Switch Detection Interface with Programmable Wetting Current**

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DDQ} = 3.1 \text{V to } 5.25 \text{V}, V_{BATP} = 6 \text{V to } 28 \text{V}, T_A = -40 ^{\circ}\text{C}$  to +125  $^{\circ}\text{C}$ , typical values are measured at  $T_A = +25 ^{\circ}\text{C}$ , unless otherwise noted.)

| PARAMETER                                                | SYMBOL                                | CONDITIONS                                                                     | MIN                     | TYP | MAX                  | UNITS |

|----------------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------|-------------------------|-----|----------------------|-------|

| Sustain Current Matching Between SP Channels (7)(8)      | I <sub>MATCH_SUS_SP</sub>             |                                                                                |                         |     | 10                   | %     |

| Wetting Current Matching Between SP Channels (9)(10)     | I <sub>MATCH_WET_SP</sub>             |                                                                                |                         |     | 6                    | %     |

| Low Dower Made Polling Current                           | 1                                     | SP programmed as SG                                                            | 0.65                    | 1   | 1.44                 | m 1   |

| Low-Power Mode Polling Current                           | ACTIVE_POLL_SP                        | SP programmed as SB                                                            | 1.85                    | 2.2 | 2.5                  | mA    |

| Digital Interface                                        |                                       |                                                                                |                         |     |                      |       |

| Tri-State Leakage Current (MISO)                         | I <sub>HZ</sub>                       | $V_{DDQ} = 0V \text{ to } V_{DDQ}$                                             | -2                      |     | 2                    | μA    |

| Input Logic Voltage Thresholds                           | $V_{IN\_LOGIC}$                       | SI, SCLK, CS_B, INT_B                                                          | 0.25 × V <sub>DDQ</sub> |     | $0.7 \times V_{DDQ}$ | V     |

| Input Logic Hysteresis                                   | V <sub>IN_LOGIC_HYS</sub>             | SI, SCLK, CS_B, INT_B                                                          | 80                      |     |                      | mV    |

| Input Logic Voltage Threshold<br>WAKE_B                  | V <sub>IN_LOGIC_WAKE</sub>            |                                                                                | 1.2                     | 1.6 | 2                    | V     |

| Input Logic Voltage Hysteresis WAKE_B                    | $V_{IN\_WAKE\_B\_HYS}$                |                                                                                | 100                     |     | 780                  | mV    |

| SCLK / MOSI Input Current                                | $I_{SCLK}$ , $I_{MOSI}$               | SCLK/MOSI = 0V                                                                 | -2                      |     | 2                    | μΑ    |

| SCLK / MOSI Pull-Down Current                            | I <sub>SCLK</sub> , I <sub>MOSI</sub> | SCLK/MOSI = V <sub>DDQ</sub>                                                   | 14                      |     | 35                   | μΑ    |

| CS_B Input Current                                       | I <sub>CS_BH</sub>                    | CS_B = V <sub>DDQ</sub>                                                        | -2                      |     | 2                    | μΑ    |

| CS_B Pull-Up Resistor to VDDQ                            | R <sub>CS_BL</sub>                    | CS_B = 0V                                                                      | 40                      | 120 | 270                  | kΩ    |

| MISO High-side Output Voltage                            | $V_{\text{OH\_MISO}}$                 | I <sub>OHMISO</sub> = -1mA                                                     | V <sub>DDQ</sub> - 0.8  |     | $V_{DDQ}$            | V     |

| MISO Low-side Output Voltage                             | $V_{\text{OL\_MISO}}$                 | I <sub>OLMISO</sub> = 1mA                                                      |                         |     | 0.4                  | V     |

| Input Capacitance on SCLK, MOSI,<br>Tri-State MISO (GBD) | $C_{IN}$                              |                                                                                |                         | 4   |                      | pF    |

| Analog MUX Output                                        |                                       |                                                                                |                         |     |                      |       |

| Input Offset Voltage When Selected as Analog             | $V_{OFFSET}$                          |                                                                                | -15                     |     | 15                   | mV    |

| Analog Operational Amplifier Low<br>Output Voltage       | $V_{OL\_AMUX}$                        | Sink 1mA                                                                       |                         |     | 50                   | mV    |

| Analog Operational Amplifier High<br>Output Voltage      | $V_{OH\_AMUX}$                        | Source 1mA                                                                     | V <sub>DDQ</sub> - 0.1  |     |                      | V     |

| AMUX Selectable Outputs                                  |                                       |                                                                                |                         |     |                      |       |

| Chip Temperature Sensor Coefficient                      | Temp-Coeff                            |                                                                                |                         | 8   |                      | mV/°C |

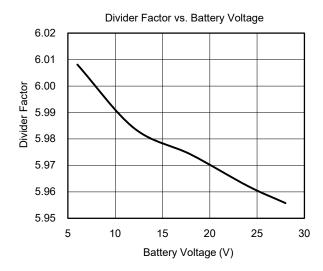

| Battery Sense (SG5 Config)<br>Accuracy                   | V <sub>BAT_SNS_ACC</sub>              | Battery voltage (SG5 input) divided by 6, accuracy over full temperature range | -5                      |     | 5                    | %     |

| INT_B                                                    |                                       |                                                                                |                         |     |                      |       |

| INT_B Output Low Voltage                                 | $V_{\text{OL\_INT}}$                  | I <sub>OUT</sub> = 1mA                                                         |                         | 0.2 | 0.5                  | V     |

| INT_B Output High Voltage                                | $V_{OH\_INT}$                         | INT_B = Open-circuit                                                           | V <sub>DDQ</sub> - 0.5  |     | $V_{DDQ}$            | V     |

| Pull-up Resistor to VDDQ                                 | $R_{PU}$                              |                                                                                | 40                      | 120 | 270                  | kΩ    |

| Leakage Current INT_B                                    | I <sub>LEAK_INT_B</sub>               | INT_B pulled up to VDDQ                                                        |                         |     | 2                    | μΑ    |

| Temperature Limit                                        |                                       |                                                                                |                         |     |                      |       |

| Temperature Warning                                      | $T_{FLAG}$                            | First flag to trip                                                             | 105                     | 115 | 135                  | °C    |

| Temperature Monitor (11)                                 | $T_{LIM}$                             |                                                                                | 156                     | 165 | 174                  | °C    |

| Temperature Monitor Hysteresis (11)                      | T <sub>LIM_HYS</sub>                  |                                                                                | 6                       | 11  | 16                   | °C    |

#### SGMCD1030Q

# **Automotive 33-Channel Multiple Switch Detection Interface with Programmable Wetting Current**

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DDQ} = 3.1V \text{ to } 5.25V, V_{BATP} = 6V \text{ to } 28V, T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ typical values are measured at } T_A = +25^{\circ}\text{C}, \text{ unless otherwise noted.})$

| PARAMETER                                | SYMBOL                    | CONDITIONS                                   | MIN                    | TYP | MAX       | UNITS |

|------------------------------------------|---------------------------|----------------------------------------------|------------------------|-----|-----------|-------|

| WAKE_B                                   |                           |                                              |                        |     |           |       |

| WAKE_B Internal Pull-Up Resistor to VDDQ | R <sub>WAKE_B_RPU</sub>   |                                              | 90                     | 150 | 200       | kΩ    |

| WAKE_B Voltage High                      | $V_{\text{WAKE\_B\_VOH}}$ | WAKE_B = Open-circuit                        | V <sub>DDQ</sub> - 1.0 |     | $V_{DDQ}$ | V     |

| WAKE_B Voltage Low                       | V <sub>WAKE_B_VOL</sub>   | WAKE_B = 1mA ( $R_{PU}$ to $V_{BATP}$ = 16V) |                        |     | 0.4       | V     |

| WAKE_B Leakage                           | I <sub>WAKE_B_LEAK</sub>  | WAKE_B = 36V                                 |                        |     | 2         | μΑ    |

#### NOTES:

- 1. ILPM\_IQ\_MAX = IBATP\_LPM\_IQ + IPOLLING\_IQ.

- 2. Guaranteed by design.

- 3.  $I_{POLLING\_IQ}$  increases as the polling action is more frequently. The highest  $I_{POLLING\_IQ}$  occurs at polling rate = 3.0ms, with all channels set to wake-up enable.

- 4. Switch detection threshold decreases when  $V_{\text{BATP}}$  is lower than 6V.

- 5. SP (as SB) only uses the 4.0V V<sub>ICTHR</sub> for LPM wake-up detection.

- 6. When VBATP is low, the SG wetting current may be limited due to the small headroom between VBATP and SG pin voltage.

- 7. (I<sub>SUS\_MAX</sub> I<sub>SUS\_MIN</sub>) × 100/I<sub>SUS\_MIN</sub>.

- 8. Sustain current source (SGs only).

- 9. (IWET MAX IWET MIN) × 100/IWET MIN.

- 10. Wetting current source (SGs only).

- 11. Guaranteed by characterization during the design period, not verified via final testing.

# **Automotive 33-Channel Multiple Switch Detection Interface with Programmable Wetting Current**

# **DYNAMIC CHARACTERISTICS**

$(V_{DDQ} = 3.1V \text{ to } 5.25V, V_{BATP} = 4.5V \text{ to } 28V, T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, SPI \text{ timing is performed with a } 100pF \text{ load on MISO, unless otherwise noted.})$

| PARAMETER                                        | SYMBOL                      | CONDITIONS                                              | MIN | TYP | MAX | UNITS |

|--------------------------------------------------|-----------------------------|---------------------------------------------------------|-----|-----|-----|-------|

| General                                          |                             |                                                         |     |     |     | _     |

| POR to Active Time                               | t <sub>ACTIVE</sub>         | Under-voltage to Normal mode                            | 260 | 370 | 490 | μs    |

| Oscillator                                       |                             |                                                         |     |     |     | •     |

| Oscillator Tolerance Normal Mode at 4.0MHz       | OSC <sub>TOLNOR</sub>       |                                                         | -15 |     | 15  | %     |

| Oscillator Tolerance at 192kHz in Low-Power Mode | OSC <sub>TOLLPM</sub>       |                                                         | -15 |     | 15  | %     |

| Switch Input                                     |                             |                                                         |     |     |     |       |

| Pulse Wetting Current Timer                      | t <sub>PULSE_ON</sub>       | Normal mode                                             | 17  | 20  | 23  | ms    |

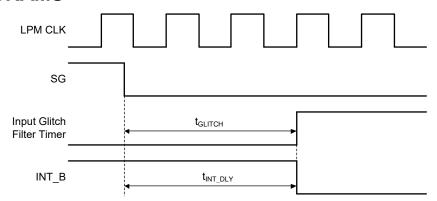

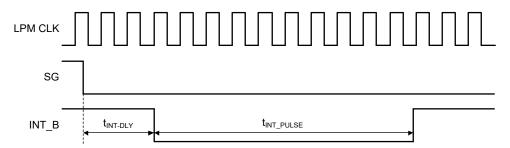

| Interrupt Delay Time                             | t <sub>INT_DLY</sub>        | Normal mode                                             | 5   |     | 25  | μs    |

| Polling Timer Accuracy                           | t <sub>POLL_TIMER</sub>     | Low-power mode                                          |     |     | 15  | %     |

| Interrupt Timer Accuracy                         | t <sub>INT_TIMER</sub>      | Low-power mode                                          |     |     | 15  | %     |

| t <sub>ACTIVE</sub> Polling Timer SG             | t <sub>ACTIVE_POLL_SG</sub> |                                                         | 38  | 56  | 70  | μs    |

| t Dolling Timer CD                               |                             | SBPOLLTIME = 0                                          | 1   | 1.2 | 1.4 | ms    |

| t <sub>ACTIVE</sub> Polling Timer SB             | t <sub>ACTIVE_POLL_SB</sub> | SBPOLLTIME = 1                                          | 38  | 56  | 70  | μs    |

| Input Glitch Filter Timer                        | t <sub>GLITCH</sub>         | Normal mode                                             | 5   |     | 25  | μs    |

| LPM Debounce Additional Time                     | t <sub>DEBOUNCE</sub>       | Low-power mode                                          | 1   | 1.2 | 1.4 | ms    |

| AMUX Output                                      |                             |                                                         |     |     | •   | •     |

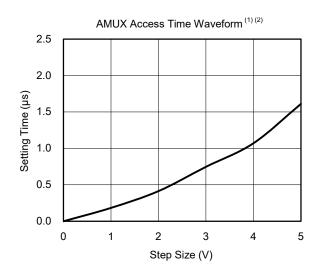

| AMUX Access Time (Tri-State to ON)               | t <sub>AMUX_VALID_TS</sub>  | C <sub>MUX</sub> = 1nF, Rising edge of CS_B to selected |     |     | 20  | μs    |

| Interrupt                                        |                             |                                                         |     |     |     |       |

| Interrupt Pulse Duration                         | t <sub>INT_PULSE</sub>      | Interrupt occurs or INT_B request                       | 80  | 110 | 135 | μs    |

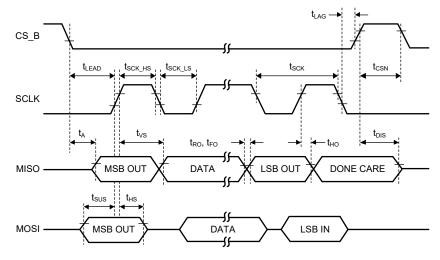

| SPI Interface                                    |                             |                                                         |     |     |     |       |

| Transfer Frequency                               | f <sub>OP</sub>             |                                                         |     |     | 8   | MHz   |

| SCLK Period                                      | t <sub>sck</sub>            |                                                         | 160 |     |     | ns    |

| Enable Lead Time                                 | t <sub>LEAD</sub>           |                                                         | 140 |     |     | ns    |

| Enable Lag Time                                  | t <sub>LAG</sub>            |                                                         | 50  |     |     | ns    |

| SCLK High Time                                   | t <sub>sck_Hs</sub>         |                                                         | 56  |     |     | ns    |

| SCLK Low Time                                    | t <sub>SCK_LS</sub>         |                                                         | 56  |     |     | ns    |

| MOSI Input Setup Time                            | t <sub>sus</sub>            |                                                         | 16  |     |     | ns    |

| MOSI Input Hold Time                             | t <sub>HS</sub>             |                                                         | 20  |     |     | ns    |

| MISO Access Time                                 | t <sub>A</sub>              |                                                         |     |     | 116 | ns    |

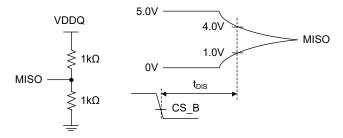

| MISO Disable Time (1)                            | t <sub>DIS</sub>            |                                                         |     |     | 100 | ns    |

| MISO Output Valid Time                           | t <sub>VS</sub>             |                                                         |     |     | 116 | ns    |

| MISO Output Hold Time (No Cap on MISO)           | t <sub>HO</sub>             |                                                         | 10  |     |     | ns    |

| Rise Time (1)                                    | t <sub>RO</sub>             |                                                         |     |     | 70  | ns    |

| Fall Time (1)                                    | t <sub>FO</sub>             |                                                         |     |     | 70  | ns    |

| CS_B Negated Time                                | t <sub>CSN</sub>            |                                                         | 500 |     |     | ns    |

#### NOTE:

1. Guaranteed by characterization.

#### **TIMING DIAGRAMS**

Figure 2. Glitch Filter and Interrupt Delay Times

Figure 3. Interrupt Pulse Timer

Figure 4. SPI Timing Diagram

Figure 5. MISO Loading for Disable Time Measurement

#### TYPICAL PERFORMANCE CHARACTERISTICS

$V_{BATP} = 12V$ ,  $V_{DDQ} = 5V$ .

#### NOTES:

- 1. R =  $1k\Omega$ , C = 1nF, See Figure 20 for more details.

- 2. The AMUX access time is measured from 10% to 90%.

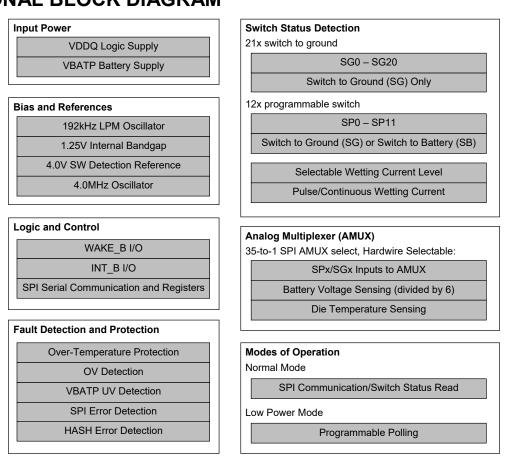

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 6. Functional Block Diagram

# **FUNCTIONAL BLOCK DIAGRAM (continued)**

Figure 7. Internal Block Diagram

#### **DETAILED DESCRIPTION**

#### **General IC Functional Description**

The SGMCD1030Q is a multiple switch detection interface (MSDI) which can detect the switch status change of 21 switch-to-ground (SG) inputs and 12 switch-to-power (SP) inputs. The SP input can be configured as switch-to-battery (SB) input or SG input through the internal registers. The device uses the serial peripheral interface (SPI) to communicate with the microcontroller unit (MCU) and transfers the switch status of either open or closed. The SGMCD1030Q also has an analog multiplexer, called AMUX, to obtain the SP/SG channel voltages information and buffers it for the possible reading requirement from the MCU.

The SGMCD1030Q needs an RC network at each SP/SG input in order to mitigate the pulse impingement. Besides, an anti-reverse diode in the forward path from the supply source to the VBATP pin is needed as well. As for the SP/SG channels, no external anti-reverse diode is needed due to the existence of internal one provided by the SGMCD1030Q.

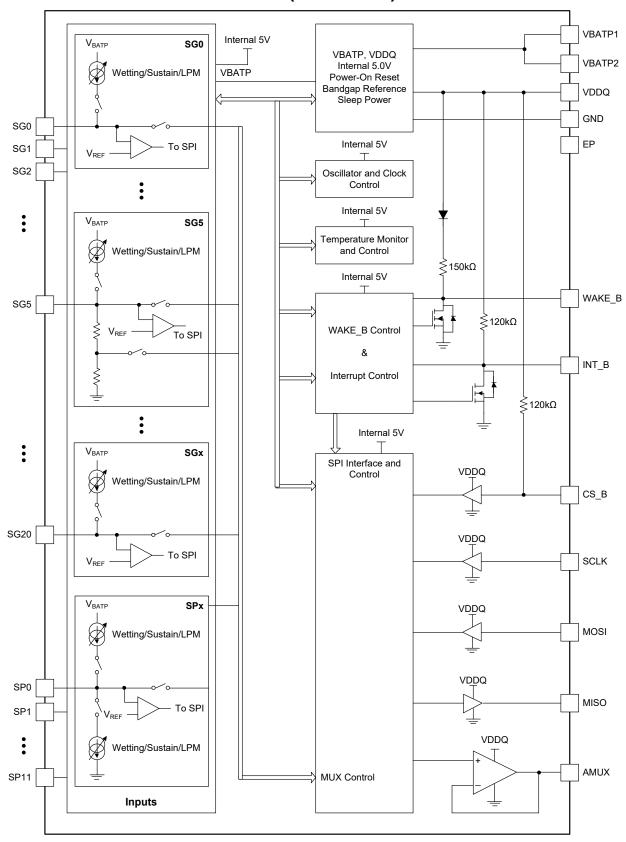

#### **Battery Voltage Ranges**

The VBATP pin operating voltage ranges from 4.5V to 36V. The maximum voltage is 40V and external supply source voltage higher than 40V should be limited to 40V, or the device might be permanently damaged. Besides, an anti-reverse diode in the forward path from the supply source (such as a battery) to the VBATP pin is needed.

#### **Load Dump (Over-Voltage)**

If a load dump event occurs, the VBATP pin voltage will increase and may exceed the device over-voltage threshold of 32V. Once an over-voltage event occurs, the wetting current is reduced to 2mA and registers are locked. In this condition, no switch status change is detected and no fault is reported unless the device comes back to normal mode.

#### **Jump Start (Double Battery)**

During a jump start (double battery) condition, the SGMCD1030Q functions normally with all parameters listed in Electrical Characteristics section. No internal faults are set and no abnormal operation noted as a result of operating in this range.

#### **Normal Battery Range**

The SGMCD1030Q functions normally with all parameters listed in Electrical Characteristics section.

#### **Under-Voltage**

In the under-voltage range, the SPI can communicate with the MCU, but errors may occur.

#### **Under-Voltage Lockout**

In the under-voltage lockout range, the SPI communication is prohibited. That is, MISO pin will not transmit any data to the MCU, and CS\_B pin will not receive any pulse from the MCU. When an under-voltage lockout event occurs at any point of communication process, the device responds immediately and enters the under-voltage lockout mode at once. An SPI bit is reserved to indicate whether the device has just left the under-voltage lockout mode.

#### Power-on Reset (POR) Activated

During the POR ranges of 2.7V to 3.8V, the SPI communication is prohibited and all register bits are reset to the default ones. When the VBATP pin voltage rises above the POR region, the SGMCD1030Q begins to enable the SPI communication and refresh all the register values to the default ones (see SPI Control register). Once a POR event occurs and after that the VBATP pin voltage falls into the normal mode range, an SPI bit in Device Configuration register will indicate the POR event.

#### No Operation

The device does not function and no switch detection is possible.

Figure 8. Battery Voltage Range

#### **Power Sequencing Conditions**

The SGMCD1030Q contains two power supply pins: VBATP and VDDQ. VBATP pin provides power for the internal sources and SG related power supplies, while VDDQ pin provides power for the SPI communication related pins (CS\_B, SCLK, MISO, MOSI and AMUX), and indicated pins (INT\_B and WAKE\_B). The following describes the SGMCD1030Q performance under different timing sequence for VBATP and VDDQ.

#### V<sub>BATP</sub> before V<sub>DDQ</sub>

Usually, the user should power VBATP first and power VDDQ in the next. Once the VBATP pin is powered ready, the internal sources are in normal operation and logic states are all in the default settings. The SPI communication function and indicated pins will be active as soon as the VDDQ pin is powered ready.

#### V<sub>DDQ</sub> before V<sub>BATP</sub>

Sometimes VDDQ may be applied before or without VBATP power. Thanks for the isolation between the VABTP powered circuits and the VDDQ powered circuits, no current can flow from the VDDQ pin to the VBATP pin so that the device may turns on. However, if the VBATP is powered after VDDQ, the SGMCD1030Q outputs definite logic state after  $t_{\text{ACTIVE}}$  (POR to active time).

#### **V<sub>BATP</sub> Ready, V<sub>DDQ</sub> Lost**

In this scenario, the current logic state is maintained, while SPI communication is unavailable.

#### **V<sub>DDQ</sub> Ready, V<sub>BATP</sub> Lost**

In this scenario, SPI communication is functional, while the actual logic state is undefined.

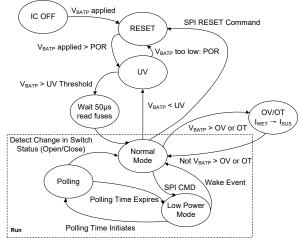

#### State Diagram

Figure 9. SGMCD1030Q State Diagram

#### **State Machine**

Figure 9 shows the state machine operation logic. When VBATP voltage is lower than POR, all registers are in the default settings and no SPI communication is permitted.

#### **UV: Under-Voltage Lockout**

Once the POR circuit has reset the device, the SGMCD1030Q enters the UV state. In this particular state, the IC retains all register settings; however, it is in a lockout mode, which means that no SPI communication is permitted. The analog multiplexer (AMUX) is inactive, and the current sources are deactivated. Since the MISO is disabled in this state, the user will not obtain a valid response from it. The chip oscillators, which operate at 4.0MHz for most normal mode and 192kHz for low-power mode (LPM), are activated during the UV state. When the VBATP voltage ascends above the UV threshold (approximately rising threshold of 4.3V), the SGMCD1030Q begins to read fuses state after 50µs.

#### **Normal Mode**

Under normal mode, the device enables SPI communication with the MCU, AMUX reading, switch status detection and related configurations including settings of wetting current, detection threshold and interrupt generated from switch state change. Note that not all registers in LPM are activated in normal mode and that any LPM-related registers is not permitted setting under LPM. In other words, LPM registers must be set under normal mode. Besides, all fault events, including OV, OT, temp flag warning, SPI error, can be reported in this mode.

#### **Low-Power Mode**

The SGMCD1030Q provides the low-power mode (LPM) in order to greatly reduce the supply current. The user has only one way to enter the LPM: writing to the Enter Low-Power Mode register. WAKE\_B is used to indicate whether the device is in LPM. Once in LPM, most power rails, 4.0MHz oscillator and all fault detection function are closed. That means no fault report is recorded in LPM.

#### **Polling Mode**

The SGMCD1030Q operates in a polling mode. It periodically (with the period being selectable in LPM Configuration register) checks the input pins to figure out their states and ascertains if there has been a switch state change since the chip was in normal mode. There are multiple configurations available for this mode, providing the user with enhanced operational flexibility. In this mode, the current sources are utilized to either pull-up (for SG) or pull-down (for SB) in order to determine whether a switch is open or closed. More details can be found in the Low-Power Mode Operation section.

When the VBATP voltage is low, the polling process is halted and it waits until the VBATP rises above the under-voltage (UV) level or a POR event takes place. The polling pause guarantees that all internal power rails, currents, and thresholds reach the necessary levels for precisely detecting open or closed switches. In this situation, the chip does not wake up; it merely waits for the VBATP voltage to increase or for a POR to occur.

Once the polling concludes, the device can be reverted to LPM or enter the normal mode if detecting a wake event. And the CS\_B, INT\_B and WAKE\_B (configurable) events can also wake it. In the LPM or polling mode, the comparator only mode switch detection is constantly active. Changing the state of those inputs will effectively wake up the IC in polling mode.

If wake-up enable bits are disabled on all SG and SP channels, the device will not respond to state changes on any input pins. In this case, the polling timer is turned off to achieve the lowest current consumption in low-power mode. The device will then disable the polling timer to allow for minimum current consumption in low-power mode.

#### **Low-Power Mode Operation**

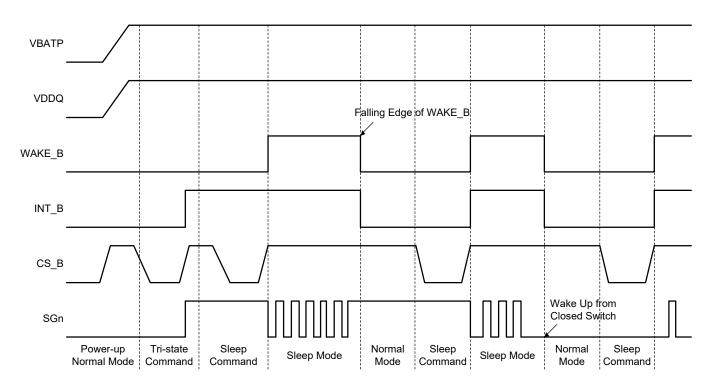

The current consumption in LPM is the lowest for SGMCD1030Q. The user has only one way to enter the LPM: writing to the Enter Low-Power Mode register. The register settings are the same with those under normal mode.

The user has several ways to exit LPM and enter normal mode:

- Change of input switch state (when enabled)

- Falling edge of WAKE\_B (as set by Device Configuration register of the device)

- Falling edge of INT\_B (V<sub>DDQ</sub> = 5.0V)

- Falling edge of CS\_B (V<sub>DDQ</sub> = 5.0V)

- Power-on Reset (POR)

In LPM, it is possible to remove the  $V_{DDQ}$  supply from the device. When  $V_{DDQ}$  is removed, a wake-up triggered by the falling edge of INT\_B and CS\_B will be disabled. After a falling edge occurs on WAKE\_B (as selected in the Device Configuration register) INT\_B, or CS\_B, the device examines  $V_{DDQ}$  status. If  $V_{DDQ}$  is low, the IC goes back to LPM without reporting a wake-up event. If  $V_{DDQ}$  is high, the IC wakes up and reports the event. Additionally, when the device is awakened using CS\_B, the first MISO data message is invalid.

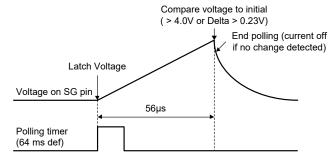

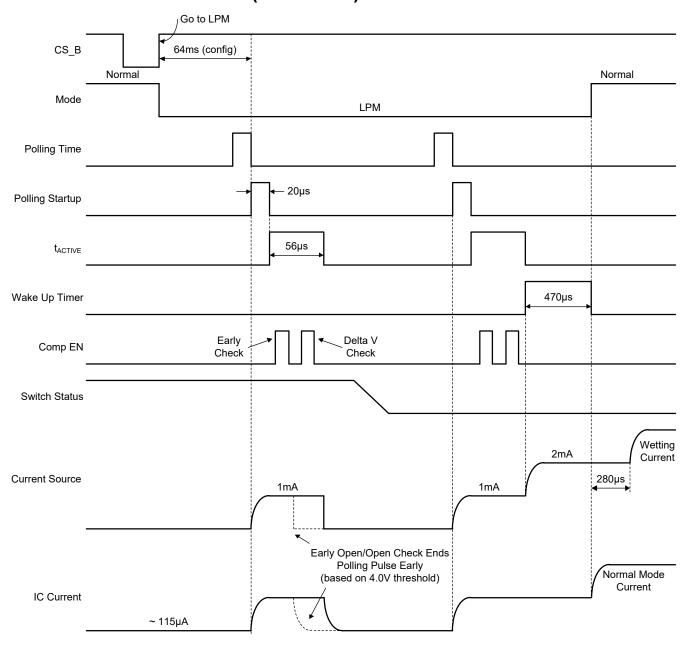

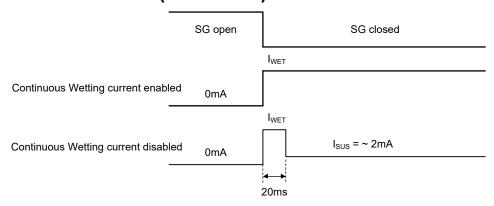

The LPM command includes the polling timer setting, which periodically monitors the inputs in low-power mode to detect any state changes. The t<sub>ACTIVE\_POLL</sub> duration indicates the time that the device remains active within each polling cycle to check for state changes. The LPM voltage threshold enables the user to decide based on the balance between noise immunity and the lower current levels that polling allows. Figure 11 illustrates the polling process.

If an input is determined to be open when entering LPM, and remains open during a polling event, the chip will stop the polling event for that particular input (or those inputs) in order to reduce the current consumption. Figure 11 shows that SG and SB are logically the same in this regard.

Figure 10. Low-Power Mode Polling Check

Figure 11. Low-Power Mode Typical Timing

Figure 12. Low-Power Mode to Normal Mode Operation

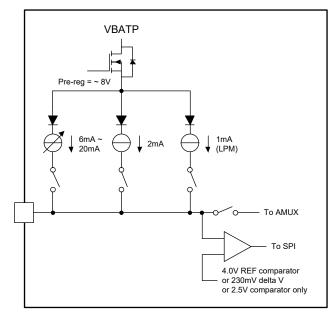

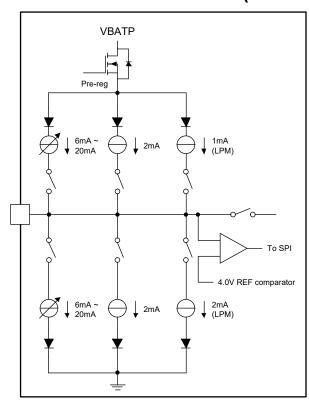

#### Input Functional Block

The SG pins function only as switch-to-ground inputs and are equipped with pull-up current sources. The SP pins, on the other hand, can be configured either as switch-to-ground (SG) or switch-to-battery (SB) with both pull-up and pull-down current sources.

The input is contrasted against a 4.0V reference (the input comparator threshold is configurable). For SG pins, voltages exceeding the input comparator threshold value are regarded as open, while for SB configuration, they are considered as closed. Conversely, voltages lower than the input comparator threshold values are deemed closed for SG pins and open for SB configurations. Programming characteristics are detailed in the SPI Control Register section.

The input comparator owns hysteresis for the thresholds and those are determined by the closing action of the switch (falling for SG, rising for SB). Employing numerous inputs with continuous wetting

current levels will lead to overheating of the IC and might trigger an over-temperature (OT) event.

Figure 13. SG Block Diagram

Figure 14. SP Block Diagram

# Oscillator and Timer Control Functional Block

The SGMCD1030Q has two basic oscillators: a 4.0MHz oscillator and a 192kHz oscillator. These two oscillators create all other clocks. Note that the 4.0MHz oscillator works under normal mode while both the 4.0MHz oscillator and the 192kHz oscillator work under LPM. The accuracy value of 4.0MHz oscillator is  $\pm 15\%$ , while the 192kHz oscillator is  $\pm 15\%$ .

#### **Temperature Monitor and Control Functional Block**

The SGMCD1030Q possesses several thermal detection cells to monitor the temperature outside. These cell outputs are OR-ed and then sent to the MCU. The device gives a temperature warning flag bit (rising threshold of +115°C) and OT monitoring bit (rising threshold of +165°C with hysteresis of 11°C). Once an OT event occurs, the wetting current is forced to be 2mA unless the temperature drops below  $T_{\text{LIM}}$  -  $T_{\text{LIM}}$ -HYS typically.

#### WAKE B Control Functional Block

The WAKE\_B pin can be considered as an open-drain output or a wake-up input. WAKE\_B keeps low in the normal mode, and will be pulled high in LPM. The WAKE\_B features an internal pull-up to VDDQ and an internal series diode, enabling an external pull-up to VBATP if needed.

When WAKE\_B is used as an input, and is pulled high in LPM. A low command from the MCU triggers the falling edge of WAKE\_B, pushing the device in normal mode. If VDDQ goes low in LPM, the WAKE\_B pin can still activate the device based on the setting of the WAKE\_B bit in the Device Configuration register. This enables the user to pull the WAKE\_B pin up to VBATP, allowing its use in a VDDQ-lost configuration.

When WAKE\_B is used as an output, it can drive either an MCU input or the Enable\_B of a regulator (potentially for VDDQ). In the normal mode, the WAKE\_B is driven low regardless of the state of VDDQ. In LPM, the WAKE\_B is released and is expected to be pulled up either internally to VDDQ or externally to VBATP. Once a valid wake-up event is detected, the device wakes up from LPM, WAKE\_B signal is set low, irrespective of the VDDQ condition.

#### **INT B Functional Block**

The INT B pin serves as both an input and an output. It indicates that an interrupt event has taken place and can also receive interrupts from other devices when multiple INT B pins are connected in a wired-OR configuration. The INT B pin is an open-drain output with an internal pull-up to VDDQ. In the normal mode, a change in the switch state triggers the INT B pin (provided that it is enabled). The INT B pin and the INT B bit in the SPI register are latched when the CS B pin has a falling edge. This enables the MCU to identify the source of the interrupt. When two SGMCD1030Q devices are utilized, only the device that initiates the interrupt will have its INT\_B bit set. The INT B pin and the INTflg bits are cleared 1µs after the falling edge of CS B. If a switch contact change occurs while CS\_B is low, the INT\_B pin will not clear when CS B has a rising edge.

In a system with multiple SGMCD1030Q devices, where WAKE\_B is high and VDDQ is on in LPM, the falling edge of INT\_B causes the device to enter the normal mode. The INT\_B pin can be configured to have either a pulsed output (where it is pulsed low for a specific INT\_B pulse duration) or a latched-low output. The default setting is the latched-low operation, and the pulsed option can be selected via the SPI.

The MCU can request an INT\_B operation by sending a SPI word, which will result in a low pulse of 110µs duration on the INT\_B pin. The chip causes an INT\_B assertion for the following cases:

- · Switch state change

- Any Wake-up event

- Fault events like OV, OT, etc.

- POR

#### **AMUX Functional Block**

The MCU can read the analog voltage of a switch by SPI commands. Inside the IC, there is a 35-to-1 analog multiplexer, called AMUX. The AMUX pin can output the voltage potential on SG/SP pins which is selected by the chip. No matter how high the voltage of input pin is, the output voltage on AMUX pin will be limited to the given value of VDDQ. The value of the matching bit in the next MISO data stream will be logic '0' after choosing an input as the analog. The current level of the AMUX output can be set by users when they need to select a channel to be read as analog input. It is supported to set current level to the programmed wetting current or high-impedance for the selected channel. When an input is selected to be sent to AMUX pin, there is no polling current on the input pin and the chip cannot wake up from state change in low-power mode. Before entering low-power mode, it is recommended to set the AMUX to 'no input selected' state. The buffer function is not available in the low-power mode.

Aside from the default SPI configuration, the AMUX pin can also be programmed as hardware 3-bit or hardware 2-bit by setting ACONFIG[1:0] from the Device Configuration register, which can be seen in Table 1 to Table 3. The hardware 3-bit takes SG1, SG2 and SG3 to choose the inputs out of SG0, SG5  $\sim$  SG9, temperature diode and battery sense. Note that the battery sense function is realized by acquiring the 1/6 SG5 pin voltage where SG5 is connected to VBATP pin

externally. The hardware 2-bit takes SG1 and SG2 to choose the inputs out of SG0, SG5-SG7. The logic 0 or 1 for SG1, SG2 and SG3 is determined by a threshold of 2.5V.

**Table 1. AMUX Selection Method**

| ACONFIG[1] | ACONFIG[0] | AMUX Selection Method |

|------------|------------|-----------------------|

| 0          | 0          | SPI (def)             |

| 0          | 1          | SPI                   |

| 1          | 0          | HW 2-bit              |

| 1          | 1          | HW 3-bit              |

Table 2. AMUX Hardware 3-bit

| Pins [SG3, SG2, SG1] | Output of AMUX    |

|----------------------|-------------------|

| 000                  | SG0               |

| 001                  | SG5               |

| 010                  | SG6               |

| 011                  | SG7               |

| 100                  | SG8               |

| 101                  | SG9               |

| 110                  | Temperature Diode |

| 111                  | Battery Sense     |

Table 3. AMUX Hardware 2-bit

| Pins [SG2, SG1] | Output of AMUX |

|-----------------|----------------|

| 00              | SG0            |

| 01              | SG5            |

| 10              | SG6            |

| 11              | SG7            |

#### **Serial Peripheral Interface (SPI)**

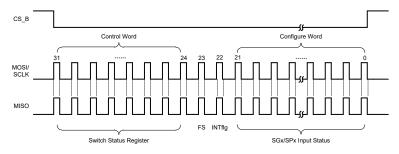

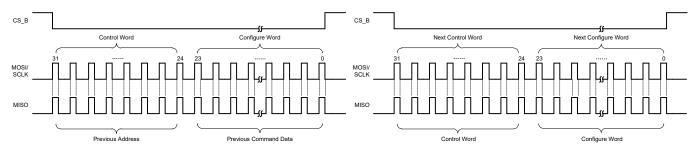

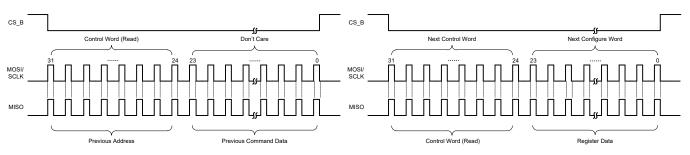

The SGMCD1030Q uses the SPI to communicate with the MCU. The SPI has four pins: SPI clock (SCLK), master-in slave-out (MISO), master-out slave-in (MOSI) and chip-selection bar (CS\_B). The SGMCD1030Q is viewed as a slave unit for the SPI.

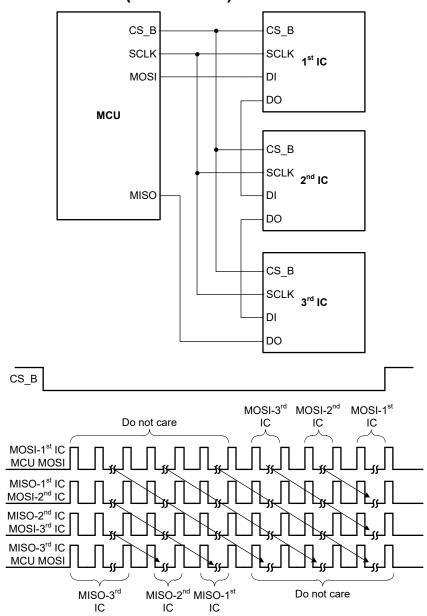

The SGMCD1030Q takes 32-bit data transmission rule to communicate with the MCU without recognizing modulo 0. Data that to be input without modulo 32-bit will be prohibited from sending into the chip. It adopts hash method to check whether the register value is true with the preset one. If not, an interrupt is issued out from the SPI and will be read by the MCU. The SPI support a daisy chain structure for multi-device communication function as well. Details can be seen from Figure 18.

#### Chip Select Low (CS\_B)

The CS\_B pin is used to choose which device is to be selected for communication. When the CS\_B pin goes low, the MISO pin exits the tri-state mode, and all status information gets latched within the SPI Shift register. While the CS\_B input is in the asserted state, register data is shifted into the MOSI pin and then shifted out from the MISO pin with each subsequent SCLK pulse. When the CS\_B pin has a rising edge, the MISO pin returns to the tri-state mode, and the fault register is reloaded (latched) with the current filtered status data. In order to provide enough time for the fault registers to be reloaded properly, the CS\_B pin must stay low for at least  $t_{\text{CSN}}$  before it goes high again.

The CS\_B input is equipped with a pull-up current source connected to VDDQ. This is designed so that in case of an open-circuit condition, it can command the de-asserted state. Moreover, this pin has voltages with compatible thresholds, which enables it to operate properly with microprocessors that use a supply voltage ranging from 3.3V to 5.0V.

#### Serial Clock (SCLK)

The SCLK input serves as the clock signal, which is crucial for synchronizing the serial data transfer. This pin features threshold-compatible voltages, enabling it

to operate correctly with microprocessors that utilize a supply voltage ranging from 3.3V to 5.0V.

When the CS\_B input is in the asserted state (active low), both the Master MCU and this device latch input data when the SCLK has a rising edge. Typically, the SPI master shifts data out during the falling edge of SCLK, whereas this device shifts data out on the rising edge of SCLK. This is done to allow more time for driving the MISO pin to the appropriate level.

This SCLK input is also employed as the input for validating the module 32-bit counter. In the event that any SPI transmissions are not exact multiples of 32 bits (in other words, not exact multiples of clock edges), such transmissions are regarded as illegal. In such cases, the entire frame is aborted and no changes are made to the information in the configuration or control registers.

#### **Serial Data Output (MISO)**

The MISO pin goes into the tri-state mode when CS\_B is asserted low. As soon as CS\_B step into the low impedance, the MISO state is identical to that of the MSB and sends out the data from the MSB to the LSB. The MISO high level voltage is nearly the same as that of VDDQ pin.

#### **SPI CONTROL REGISTER**

#### **Serial Data Input (MOSI)**

The MOSI pin receives data from the master MCU when CS\_B is asserted low. It is compatible with voltages ranging from 3.3V to 5.0V for the VDDQ pin. The user can use the SPI to configure the settings and read the current status of each input for the SGMCD1030Q. Besides, the SPI provides the Fault Status and INTflg bits for the MCU reading. Table 4 gives the detailed descriptions about the SPI MOSI registers.

**Table 4. MOSI Input Register Bit Definition**

| 0 SPI Check 02/03 Device Configuration Register 04/05 Tri-State SP Register 06/07 Tri-State SG Register 08/09 Wetting Current Level SP Register 0 10/11 Wetting Current Level SP Register 1 0A/0B Wetting Current Level SG Register 0 0C/0D Wetting Current Level SG Register 1 0E/0F Wetting Current Level SG Register 2 16/17 Continuous Wetting Current SP Register 18/19 Continuous Wetting Current SP Register 1A/1B Interrupt Enable SP Register 1C/1D Interrupt Enable SG Register 1E/1F Low-Power Mode Configuration 20/21 Wake-up Enable Register SP | 0000 000 | 1   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|