# SGM51613R4A/SGM51613R8A 16-Bit, 1MSPS, 4-Channel/8-Channel Low Power, Serial Interface ADC

#### **GENERAL DESCRIPTION**

The SGM51613R4A and SGM51613R8A are 16-bit, 4-channel/8-channel, successive approximation (SAR) analog-to-digital converters (ADCs).

The device is powered by a single source VDD (generally is 5V).

The device can communicate with 1.8V to 5V digital device in which condition the VIO needs to be powered by appropriate voltage accordingly.

The digital interface is compatible to the traditional SPI protocol.

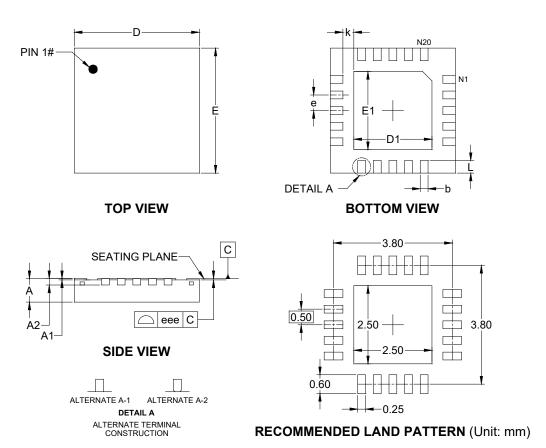

The SGM51613R4A and SGM51613R8A are available in Green TQFN-  $4\times4$ -20AL and WLCSP-2.39×2.39-20B packages. It operates over an ambient temperature range of -40°C to +125°C.

#### **APPLICATIONS**

Process Control

Power Line Monitoring

Battery-Powered Equipment

Instrumentation

#### **FEATURES**

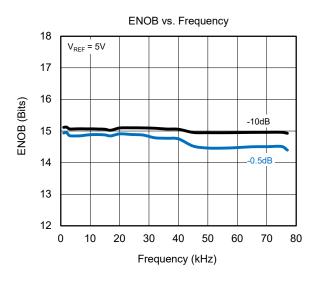

- 16 Bits, 1MSPS SAR ADC

- No Missing Codes

- 4-Channel (SGM51613R4A)/8-Channel (SGM51613R8A)

Multiplexer

- Supported Input Types:

- Single-Ended

- Pseudo Differential (Reference to 1/2V<sub>REF</sub>)

- Pseudo Differential (Reference to GND)

- Analog Input Range:

0V to  $V_{REF}$  with  $V_{REF}$  up to  $V_{DD}$

- Supply Voltage Ranges:

- Analog Supply: 4.5V to 5.5V

- I/O Supply: 1.8V to 5.5V

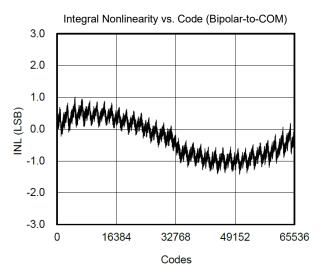

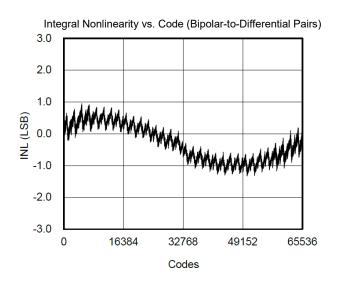

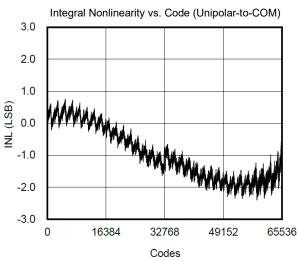

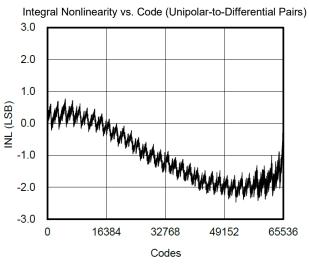

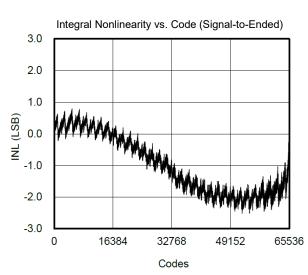

- Integral Nonlinearity (INL): ±2.5LSB (TYP)

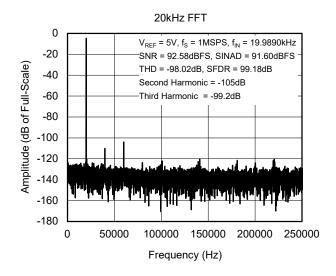

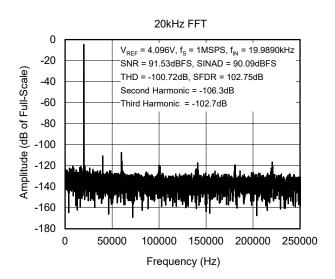

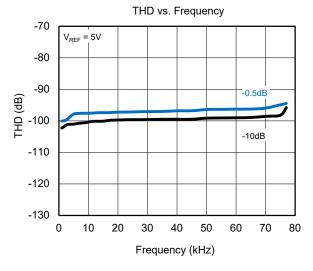

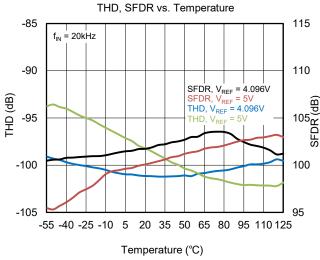

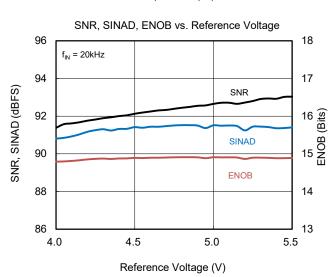

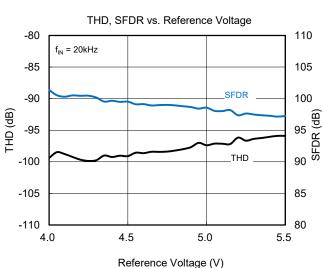

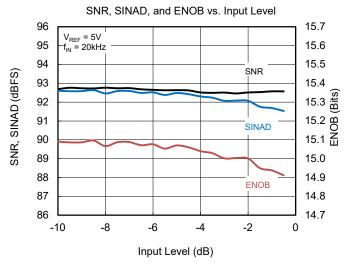

- Total Harmonic Distortion (THD):

- -98dB (TYP) at 20kHz for TQFN Package

- + -97dB (TYP) at 20kHz for WLCSP Package

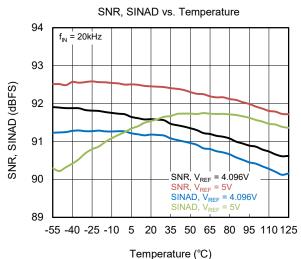

- Signal-to-Noise + Distortion (SINAD):

91.5dBFS (TYP) at 20kHz

- Power Dissipation

- 55mW (TYP) at 1MSPS

- 5.4mW (TYP) at 100kSPS

- Standby Current: 1µA (TYP)

- Multiple Reference Types

- Internal Reference: 4.096V

- External Buffered Reference: Up to V<sub>DD</sub> 0.3V

- External Reference: Up to V<sub>DD</sub>

- Support Channel Sequencer

- Support Selectable 1-Pole Filter and Busy Indicator

- Internal Temperature Sensor

- SPI-Compatible Serial Interface

- Available in Green TQFN-4×4-20AL and WLCSP-2.39×2.39-20B Packages

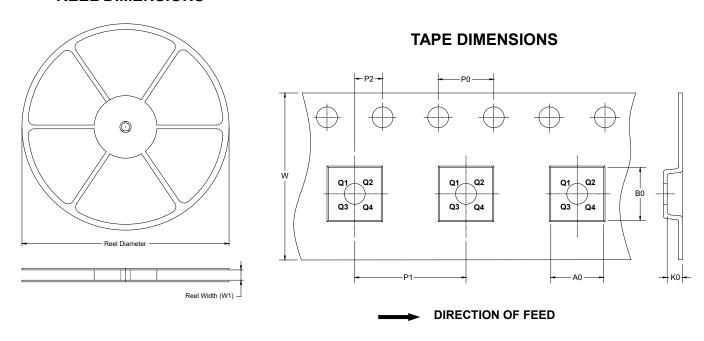

#### PACKAGE/ORDERING INFORMATION

| MODEL         | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER        | PACKAGE<br>MARKING          | PACKING<br>OPTION   |  |

|---------------|------------------------|-----------------------------------|---------------------------|-----------------------------|---------------------|--|

|               | TOFN 4×4 20A1          | 40°C 4- 1405°C                    | SGM51613R4AXTUH20G/TR     | 51613R4A<br>XTUH20<br>XXXXX | Tape and Reel, 3000 |  |

| SGM51613R4A   | TQFN-4×4-20AL          | -40°C to +125°C                   | SGM51613R4AXTUH20SG/TR    | 51613R4A<br>XTUH20<br>XXXXX | Tape and Reel, 500  |  |

| 3GW31013R4A   | WLCSP-2.39×2.39-20B    | -40°C to +125°C                   | SGM25I XXXXX Tape and Rec |                             |                     |  |

|               | WLCGF-2.38^2.38-20D    | -40 C to +125 C                   | 25°C XX#XX SGM25I         | Tape and Reel, 500          |                     |  |

|               | TQFN-4×4-20AL          | -40°C to +125°C                   | SGM51613R8AXTUH20G/TR     | Tape and Reel, 3000         |                     |  |

| SGM51613R8A   | 1 QFN-4^4-20AL         | -40 C to +125 C                   | SGM51613R8AXTUH20SG/TR    | 51613R8A<br>XTUH20<br>XXXXX | Tape and Reel, 500  |  |

| SGIVISTOTSROA | WLCSP-2.39×2.39-20B    | -40°C to +125°C                   | SGM51613R8AXG/TR          | SGM1WY<br>XXXXX<br>XX#XX    | Tape and Reel, 3000 |  |

|               | WLC3F-2.38^2.38-20B    | -40 C 10 + 125 C                  | SGM51613R8AXSG/TR         | SGM1WY<br>XXXXX<br>XX#XX    | Tape and Reel, 500  |  |

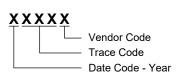

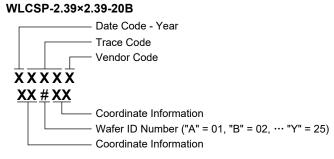

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code. XX#XX = Coordinate Information and Wafer ID Number.

TQFN-4×4-20AL

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

# SGM51613R4A SGM51613R8A

# 16-Bit, 1MSPS, 4-Channel/8-Channel Low Power, Serial Interface ADC

#### **ABSOLUTE MAXIMUM RATINGS**

| Analog Inputs                              |                            |

|--------------------------------------------|----------------------------|

| INx, COMGND -                              | $0.3V$ to $V_{DD} + 0.3V$  |

| REF, REFINGND -                            | $0.3V$ to $V_{DD} + 0.3V$  |

| Supply Voltages                            |                            |

| V <sub>DD</sub> , V <sub>IO</sub> to GND   | 0.3V to 6V                 |

| V <sub>DD</sub> to V <sub>IO</sub>         | ±6V                        |

| DIN, CNV, SCLK to GND                      | $-0.3V$ to $V_{IO} + 0.3V$ |

| SDO to GND                                 | $-0.3V$ to $V_{IO} + 0.3V$ |

| Input Current to Any Pin except Supplies . | ±10mA                      |

| Package Thermal Resistance (SGM51613       | BR4A)                      |

| TQFN-4×4-20AL, θ <sub>JA</sub>             | 35.6°C/W                   |

| TQFN-4×4-20AL, θ <sub>JB</sub>             | 11.6°C/W                   |

| TQFN-4×4-20AL, θ <sub>JC (TOP)</sub>       | 26.1°C/W                   |

| TQFN-4×4-20AL, θ <sub>JC (BOT)</sub>       | 1.7°C/W                    |

| WLCSP-2.39×2.39-20B, θ <sub>JA</sub>       | 72°C/W                     |

| WLCSP-2.39×2.39-20B, θ <sub>JB</sub>       | 21.4°C/W                   |

| WLCSP-2.39×2.39-20B, θ <sub>JC</sub>       | 12°C/W                     |

| Package Thermal Resistance (SGM51613       | BR8A)                      |

| TQFN-4×4-20AL, θ <sub>JA</sub>             | 35.9°C/W                   |

| TQFN-4×4-20AL, θ <sub>JB</sub>             | 13.1°C/W                   |

| TQFN-4×4-20AL, θ <sub>JC (TOP)</sub>       | 26.6°C/W                   |

| TQFN-4×4-20AL, θ <sub>JC (BOT)</sub>       | 1.7°C/W                    |

| WLCSP-2.39×2.39-20B, θ <sub>JA</sub>       | 72°C/W                     |

| WLCSP-2.39×2.39-20B, θ <sub>JB</sub>       | 21.4°C/W                   |

| WLCSP-2.39×2.39-20B, θ <sub>JC</sub>       | 12°C/W                     |

| Junction Temperature                       | +150°C                     |

| Storage Temperature Range                  | 65°C to +150°C             |

| Lead Temperature (Soldering, 10s)          | +260°C                     |

| ESD Susceptibility (1) (2)                 |                            |

| HBM                                        | ±4000V                     |

| CDM                                        | ±1000V                     |

|                                            |                            |

#### NOTES:

- 1. For human body model (HBM), all pins comply with ANSI/ESDA/JEDEC JS-001 specifications.

- 2. For charged device model (CDM), all pins comply with ANSI/ESDA/JEDEC JS-002 specifications.

#### RECOMMENDED OPERATING CONDITIONS

Operating Temperature Range.....-40°C to +125°C

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

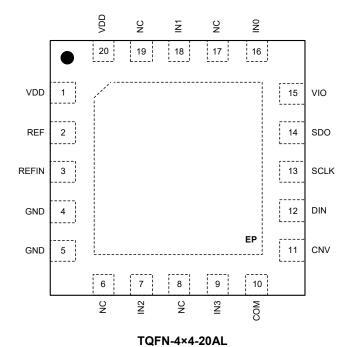

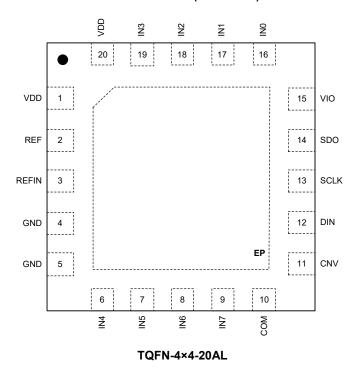

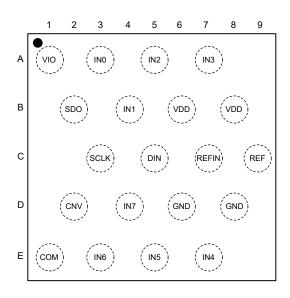

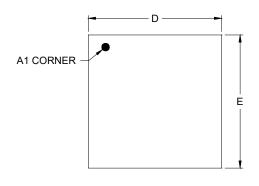

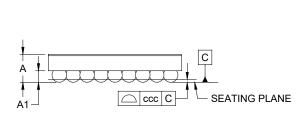

#### PIN CONFIGURATIONS

#### SGM51613R4A (TOP VIEW)

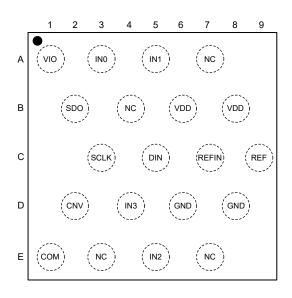

#### SGM51613R4A (TOP VIEW)

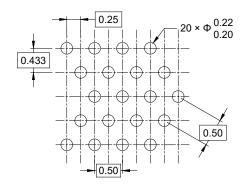

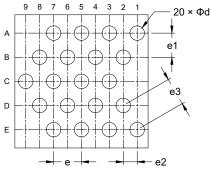

WLCSP-2.39×2.39-20B

#### SGM51613R8A (TOP VIEW)

#### SGM51613R8A (TOP VIEW)

WLCSP-2.39×2.39-20B

# 16-Bit, 1MSPS, 4-Channel/8-Channel Low Power, Serial Interface ADC

# **PIN DESCRIPTION**

| F                 | PIN                     |       |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------|-------------------------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TQFN-<br>4×4-20AL | WLCSP-<br>2.39×2.39-20B | NAME  | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1, 20             | B6, B8                  | VDD   | Р    | Power Supply Pin. The power supply of this pin must be higher than the voltage potential of reference (internal or external). 10µF and 100nF decoupling capacitors should be connected here. The range of VDD is from 4.5V to 5.5V.                                                                                                                                                                                                                                                                                                                                       |

| 2                 | C9                      | REF   | AI/O | Reference Input/Output Pin. This pin needs to be decoupled by 10µF capacitors to GND and the capacitor should be installed as close to REF as possible. There are three working modes for REF pin. Firstly, when working in the internal reference mode, this pin produces 4.096V and no external reference is needed. Secondly, when the internal reference is disabled and the internal buffer is enabled, REF pin can buffer out the voltage presenting on the REFIN pin. Thirdly, a precise reference can be directly connected to REF pin for the best drift effect. |

| 3                 | <b>C</b> 7              | REFIN | AI/O | Internal Reference Output/Reference Buffer Input. It is a multi-function pin. If the internal reference function is selected, a $1\mu F$ decoupling capacitor needs to be connected. If the reference buffer input function is selected, an external reference voltage source needs to be connected. The voltage reference available range is from 1V to $V_{DD}$ - $0.3V.$                                                                                                                                                                                               |

| 4, 5              | D6, D8                  | GND   | Р    | Power Supply Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6                 | E7                      | IN4   | Al   | Analog Input Pin for Channel 4. (Only for SGM51613R8A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                   |                         | NC    | _    | No Connection. (Only for SGM51613R4A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7                 | E5                      | IN5   | Al   | Analog Input Pin for Channel 5. (Only for SGM51613R8A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ,                 | 20                      | IN2   |      | Analog Input Pin for Channel 2. (Only for SGM51613R4A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 8                 | E3                      | IN6   | Al   | Analog Input Pin for Channel 6. (Only for SGM51613R8A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                   |                         | NC    | _    | No Connection. (Only for SGM51613R4A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 9                 | D4                      | IN7   | Al   | Analog Input Pin for Channel 7. (Only for SGM51613R8A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                   | J .                     | IN3   |      | Analog Input Pin for Channel 3. (Only for SGM51613R4A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10                | E1                      | СОМ   | Al   | Common Input Pin. Common voltage reference of analog input channels. All input channels can be referenced to a common mode point of 0V or $V_{\text{REF}}/2V$ .                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11                | D2                      | CNV   | DI   | Conversion Input Pin. It is a digital control pin. The rising edge of CNV signal starts the conversion. During conversion, if CNV is held high long enough, the busy indicator is disabled.                                                                                                                                                                                                                                                                                                                                                                               |

| 12                | C5                      | DIN   | DI   | Data Input Pin. It is the digital input pin of SPI serial interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 13                | C3                      | SCLK  | DI   | Serial Data Clock Input Pin. It is the digital clock input pin of serial interface. The SPI data is locked out is in MSB first format.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 14                | B2                      | SDO   | DO   | Serial Data Output Pin. It is the digital data output pin of serial interface. The SDO will synchronize with the above SCLK and output conversion result. When IN- is connected with GND, the conversion results are straight binary. When IN- is connected with 1/2V <sub>REF</sub> , the conversion results are two's complement.                                                                                                                                                                                                                                       |

| 15                | A1                      | VIO   | Р    | Input/Output Interface Digital Power Supply Pin. Generally, this pin is powered with the same power source of digital controller.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# **PIN DESCRIPTION (continued)**

| F                 | PIN                     |      |      |                                                                   |  |  |

|-------------------|-------------------------|------|------|-------------------------------------------------------------------|--|--|

| TQFN-<br>4×4-20AL | WLCSP-<br>2.39×2.39-20B | NAME | TYPE | FUNCTION                                                          |  |  |

| 16                | A3                      | IN0  | Al   | Analog Input Pin for Channel 0.                                   |  |  |

| 17                | 17 B4                   |      | Al   | Analog Input Pin for Channel 1. (Only for SGM51613R8A)            |  |  |

| 17                | D <del>4</del>          | NC   | _    | No Connection. (Only for SGM51613R4A)                             |  |  |

| 18                | A5                      | IN2  | Al   | Analog Input Pin for Channel 2. (Only for SGM51613R8A)            |  |  |

| 10                | Ab                      | IN1  | Al   | Analog Input Pin for Channel 1. (Only for SGM51613R4A)            |  |  |

| 19                | A7                      | IN3  | Al   | Analog Input Pin for Channel 3. (Only for SGM51613R8A)            |  |  |

| 19                | A/                      | NC   | _    | No Connection. (Only for SGM51613R4A)                             |  |  |

| Exposed Pad       | _                       | EP   | _    | Exposed pad should be soldered to PCB board and connected to GND. |  |  |

NOTE: AI = analog input, AI/O = analog input/output, DI = digital input, DO = digital output, P = power.

# **ELECTRICAL CHARACTERISTICS**

$(T_A = -40^{\circ}C \text{ to } +125^{\circ}C, V_{DD} = 5V, V_{REF} = 4.096V \text{ to } V_{DD}, V_{IO} = 3V, \text{ all typical values are measured } T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETER                                    | SYMBOL         | CON                                            | MIN                  | TYP                  | MAX                 | UNITS                  |      |

|----------------------------------------------|----------------|------------------------------------------------|----------------------|----------------------|---------------------|------------------------|------|

| Resolution                                   |                |                                                |                      | 16                   |                     |                        | Bits |

| Analog Input                                 | 1              |                                                | -                    |                      | •                   | •                      |      |

| Voltage Range                                | VIN+ - VIN-    | Single-ended mode, (INx- = GND), or diffe      | 0                    |                      | +V <sub>REF</sub>   | V                      |      |

| voltage ivalige                              | VIIV+ - VIIV-  | Differential with COM differential pairs (INx- |                      | -V <sub>REF</sub> /2 |                     | +V <sub>REF</sub> /2   | V    |

|                                              |                | Positive input, unipola                        | ar and bipolar modes | -0.1                 |                     | V <sub>REF</sub> + 0.1 |      |

| Absolute Input Voltage                       |                | Negative or COM inp                            | ut, unipolar mode    | -0.1                 |                     | +0.1                   | V    |

|                                              |                | Negative or COM inp                            | ut, bipolar mode     |                      | V <sub>REF</sub> /2 |                        | ]    |

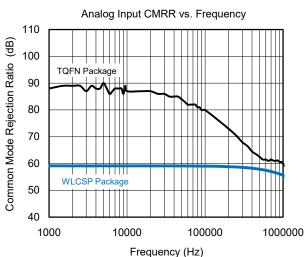

| Analog Innut CMDD                            |                | £ _ 050kl  -                                   | TQFN package         |                      | 72                  |                        | 40   |

| Analog Input CMRR                            |                | f <sub>IN</sub> = 250kHz                       | WLCSP package        |                      | 59                  |                        | dB   |

| Leakage Current at +25°C Input Impedance (1) |                | Acquisition phase                              |                      |                      | 18                  |                        | nA   |

| Throughput                                   |                |                                                |                      |                      |                     |                        |      |

| Conversion Rate                              |                | Full bandwidth (2)                             |                      |                      |                     | 1000                   | kSPS |

| Conversion Nate                              |                | 1/4 bandwidth (2)                              |                      |                      |                     | 250                    | KOFO |

| Transient Deenense                           |                | Full-scale step, full ba                       | andwidth             |                      |                     | 200                    | 20   |

| Transient Response                           |                | Full-scale step, ¼ ba                          | ndwidth              |                      |                     | 800                    | ns   |

| Accuracy                                     |                |                                                |                      |                      |                     |                        |      |

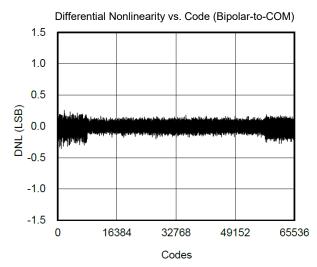

| No Missing Codes                             |                |                                                |                      |                      | 16                  |                        | Bits |

| Integral Linearity                           | INL            | TQFN package                                   | -6.5                 | ±2.5                 | 4.5                 | LSB (3)                |      |

| integral Lineanty                            | IINL           | WLCSP package                                  | WLCSP package        |                      | ±2.5                | 12                     | LOD  |

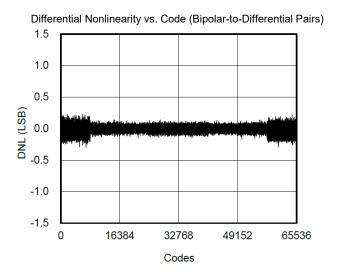

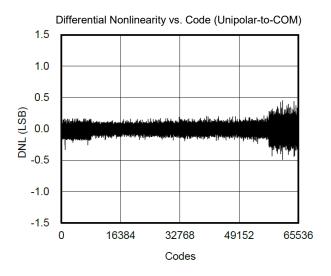

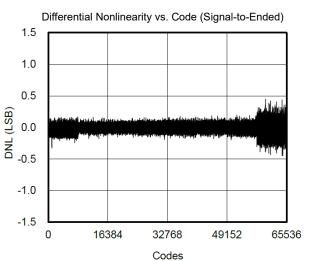

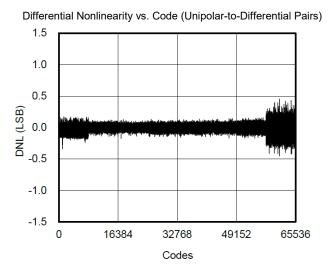

| Differential Linearity                       | DNL            |                                                |                      | -0.999               | ±0.6                | 4                      | LSB  |

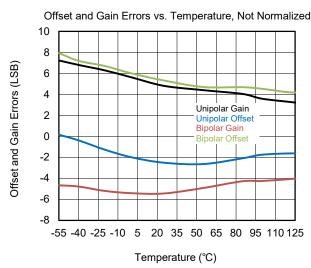

| Gain Error (4)                               | E <sub>G</sub> |                                                |                      | -18                  | ±2                  | 18                     | LSB  |

| Gain Error Match                             |                |                                                |                      | -8.5                 | ±1                  | 8.5                    | LSB  |

|                                              |                | INCC[2:0] = 00X                                | TQFN package         | -23                  | ±5                  | 14                     |      |

|                                              |                |                                                | WLCSP package        | -20.5                | ±2                  | 18.5                   |      |

|                                              |                | INCC[2:0] = 010                                | TQFN package         | -33                  | ±6                  | 14                     |      |

|                                              |                | 1100[2.0] = 010                                | WLCSP package        | -14                  | ±2                  | 29                     |      |

| Offset Error (4)                             |                | INCC[2:0] = 10V                                | TQFN package         | -15                  | ±2                  | 13                     | LSB  |

| Offset Effor **                              | Eo             | INCC[2:0] = 10X                                | WLCSP package        | -15.5                | ±2                  | 15.5                   | LOD  |

|                                              |                | INCC[2:0] = 440                                | TQFN package         | -21                  | ±4                  | 11                     |      |

|                                              |                | INCC[2:0] = 110                                | WLCSP package        | -16                  | ±2                  | 12                     |      |

|                                              |                | INICC(2)-01 = 444                              | TQFN package         | -17                  | ±2.5                | 13                     |      |

|                                              |                | INCC[2:0] = 111                                | WLCSP package        | -13.5                | ±2                  | 13.5                   |      |

| Offeet Error Matal                           |                | TQFN package                                   |                      | -13                  | ±2                  | 13                     | 1.00 |

| Offset Error Match                           |                | WLCSP package                                  |                      | -9.5                 | ±2                  | 9.5                    | LSB  |

| Power Supply Sensitivity                     |                | $V_{DD} = 5V \pm 5\%$                          |                      |                      | ±1.5                |                        | LSB  |

# 16-Bit, 1MSPS, 4-Channel/8-Channel **Low Power, Serial Interface ADC**

**ELECTRICAL CHARACTERISTICS (continued)**  $(T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \ V_{DD} = 5\text{V}, \ V_{REF} = 4.096\text{V to } V_{DD}, \ V_{IO} = 3\text{V}, \ \text{all typical values are measured } T_A = +25^{\circ}\text{C}, \ \text{unless otherwise}$ noted.)

| PARAMETER                    | SYMBOL | CONDITIONS                                    |               | MIN  | TYP  | MAX | UNITS    |  |

|------------------------------|--------|-----------------------------------------------|---------------|------|------|-----|----------|--|

| AC Accuracy                  |        |                                               |               |      |      |     |          |  |

|                              |        | f <sub>IN</sub> = 20kHz,                      | TQFN package  | 88.5 | 92.7 |     |          |  |

|                              |        | V <sub>REF</sub> = 5V,<br>INCC[2:0] = 00X     | WLCSP package | 86.5 | 92.3 |     | _        |  |

|                              |        | $f_{IN} = 20kHz$ ,                            | TQFN package  | 88.5 | 92.7 |     |          |  |

|                              |        | V <sub>REF</sub> = 5V,<br>INCC[2:0] = 010     | WLCSP package | 86.5 | 92.3 |     |          |  |

|                              |        | f <sub>IN</sub> = 20kHz,                      | TQFN package  | 88.5 | 92.7 |     |          |  |

|                              |        | V <sub>REF</sub> = 5V,<br>INCC[2:0] = 10X     | WLCSP package | 86   | 92.3 |     |          |  |

|                              |        | $f_{IN} = 20kHz,$                             | TQFN package  | 88.5 | 92.7 |     |          |  |

|                              |        | V <sub>REF</sub> = 5V,<br>INCC[2:0] = 110     | WLCSP package | 86   | 92.3 |     |          |  |

|                              |        | f <sub>IN</sub> = 20kHz,                      | TQFN package  | 88.5 | 92.7 |     |          |  |

|                              |        | V <sub>REF</sub> = 5V,<br>INCC[2:0] = 111     | WLCSP package | 85.5 | 92.3 |     |          |  |

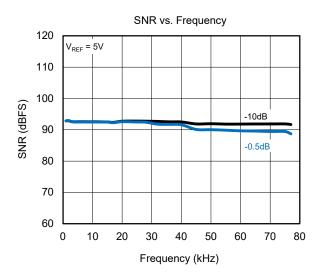

| Signal-to-Noise Ratio        | SNR    | f <sub>IN</sub> = 20kHz,                      | TQFN package  | 85.5 | 91.5 |     | dBFS (5) |  |

|                              |        | V <sub>REF</sub> = 4.096V,<br>INCC[2:0] = 00X | WLCSP package | 84.5 | 91.5 |     |          |  |

|                              |        | f <sub>IN</sub> = 20kHz,                      | TQFN package  | 85.5 | 91.5 |     |          |  |

|                              |        | V <sub>REF</sub> = 4.096V,<br>INCC[2:0] = 010 | WLCSP package | 84.5 | 91.5 |     |          |  |

|                              |        | f <sub>IN</sub> = 20kHz,                      | TQFN package  | 86.5 | 91.5 |     |          |  |

|                              |        | $V_{REF} = 4.096V,$<br>INCC[2:0] = 10X        | WLCSP package | 85   | 91.5 |     |          |  |

|                              |        | f <sub>IN</sub> = 20kHz,                      | TQFN package  | 86.5 | 91.5 |     |          |  |

|                              |        | V <sub>REF</sub> = 4.096V,<br>INCC[2:0] = 110 | WLCSP package | 85   | 91.5 |     |          |  |

|                              |        | f <sub>IN</sub> = 20kHz,                      | TQFN package  | 86   | 91.5 |     |          |  |

|                              |        | $V_{REF} = 4.096V,$<br>INCC[2:0] = 111        | WLCSP package | 84.5 | 91.5 |     |          |  |

|                              |        | $f_{IN} = 20kHz,$                             | TQFN package  | 88   | 91.5 |     |          |  |

|                              |        | V <sub>REF</sub> = 5V,<br>INCC[2:0] = 00X     | WLCSP package | 85.5 | 91.0 |     |          |  |

|                              |        | f <sub>IN</sub> = 20kHz,                      | TQFN package  | 88   | 91.5 |     |          |  |

|                              |        | V <sub>REF</sub> = 5V,<br>INCC[2:0] = 010     | WLCSP package | 85.5 | 91.0 |     |          |  |

|                              |        | f <sub>IN</sub> = 20kHz,                      | TQFN package  | 88   | 91.5 |     |          |  |

|                              |        | V <sub>REF</sub> = 5V,<br>INCC[2:0] = 10X     | WLCSP package | 85.5 | 91.0 |     |          |  |

|                              |        | f <sub>IN</sub> = 20kHz,                      | TQFN package  | 88   | 91.5 |     |          |  |

|                              |        | V <sub>REF</sub> = 5V,<br>INCC[2:0] = 110     | WLCSP package | 85.5 | 91.0 |     |          |  |

|                              |        | f <sub>IN</sub> = 20kHz,                      | TQFN package  | 88   | 91.5 |     |          |  |

|                              |        | V <sub>REF</sub> = 5V,<br>INCC[2:0] = 111     | WLCSP package | 84.5 | 91.0 |     | (5)      |  |

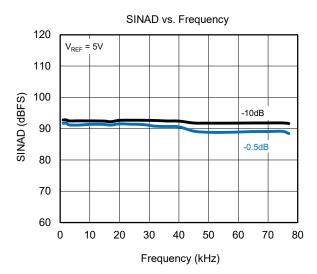

| Signal-to-Noise + Distortion | SINAD  | f <sub>IN</sub> = 20kHz,                      | TQFN package  | 85   | 91.0 |     | dBFS (5) |  |

|                              |        | V <sub>REF</sub> = 4.096V,<br>INCC[2:0] = 00X | WLCSP package | 84   | 91.0 |     |          |  |

|                              |        | f <sub>IN</sub> = 20kHz,                      | TQFN package  | 85   | 91.0 |     |          |  |

|                              |        | $V_{REF} = 4.096V,$<br>INCC[2:0] = 010        | WLCSP package | 84   | 91.0 |     | 1        |  |

|                              |        | f <sub>IN</sub> = 20kHz,                      | TQFN package  | 86   | 91.0 |     | 1        |  |

|                              |        | V <sub>REF</sub> = 4.096V,<br>INCC[2:0] = 10X | WLCSP package | 84   | 91.0 |     | 1        |  |

|                              |        | f <sub>IN</sub> = 20kHz,                      | TQFN package  | 86   | 91.0 |     | 1        |  |

|                              |        | V <sub>REF</sub> = 4.096V,<br>INCC[2:0] = 110 | WLCSP package | 84.5 | 91.0 |     | 1        |  |

|                              |        | f <sub>IN</sub> = 20kHz,                      | TQFN package  | 85.5 | 91.0 |     | 1        |  |

|                              |        | V <sub>REF</sub> = 4.096V,<br>INCC[2:0] = 111 | WLCSP package | 84   | 91.0 |     | 1        |  |

**ELECTRICAL CHARACTERISTICS (continued)**  $(T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \ V_{DD} = 5\text{V}, \ V_{REF} = 4.096\text{V to } V_{DD}, \ V_{IO} = 3\text{V}, \ \text{all typical values are measured } T_A = +25^{\circ}\text{C}, \ \text{unless otherwise}$ noted.)

| PARAMETER                    | SYMBOL | CONDITIO                                                                                                          | ONS           | MIN   | TYP   | MAX   | UNITS        |

|------------------------------|--------|-------------------------------------------------------------------------------------------------------------------|---------------|-------|-------|-------|--------------|

| AC Accuracy                  |        |                                                                                                                   |               |       |       |       |              |

|                              |        | $ f_{\text{IN}} = 20 \text{kHz}, \\ V_{\text{REF}} = 5 \text{V}, \\ \text{INCC}[2:0] = 00 \text{X}, $             | TQFN package  |       | -98   | -91   |              |

|                              |        | bipolar differential pairs<br>mode                                                                                | WLCSP package |       | -97   | -85   |              |

|                              |        | $f_{IN} = 20kHz,$<br>$V_{REF} = 5V,$                                                                              | TQFN package  |       | -98   | -89   |              |

|                              |        | INCC[2:0] = 010,<br>bipolar mode                                                                                  | WLCSP package |       | -97   | -84   | 1            |

|                              |        | f <sub>IN</sub> = 20kHz,<br>V <sub>REF</sub> = 5V,                                                                | TQFN package  |       | -98   | -91   |              |

|                              |        | INCC[2:0] = 10X,<br>unipolar differential<br>pairs mode                                                           | WLCSP package |       | -97   | -85   |              |

|                              |        | $f_{IN} = 20kHz,$<br>$V_{REF} = 5V,$                                                                              | TQFN package  |       | -98   | -89   |              |

|                              | THD    | INCC[2:0] = 110,<br>unipolar to COM mode                                                                          | WLCSP package |       | -97   | -84   |              |

|                              |        | $f_{IN} = 20kHz,$<br>$V_{REF} = 5V,$                                                                              | TQFN package  |       | -98   | -89   | ]            |

|                              |        | INCC[2:0] = 111,<br>unipolar mode                                                                                 | WLCSP package |       | -97   | -85   | Ī . <u>.</u> |

| Total Harmonic Distortion    |        | f <sub>IN</sub> = 20kHz,<br>V <sub>REF</sub> = 4.096V,<br>INCC[2:0] = 00X,                                        | TQFN package  |       | -100  | -91   | - dB         |

|                              |        | bipolar differential pairs mode                                                                                   | WLCSP package |       | -100  | -85   |              |

|                              |        | $f_{IN} = 20kHz,$<br>$V_{REF} = 4.096V,$                                                                          | TQFN package  |       | -100  | -91   |              |

|                              |        | INCC[2:0] = 010,<br>bipolar mode                                                                                  | WLCSP package |       | -100  | -85   |              |

|                              |        | f <sub>IN</sub> = 20kHz,<br>V <sub>REF</sub> = 4.096V,<br>INCC[2:0] = 10X,<br>unipolar differential<br>pairs mode | TQFN package  |       | -100  | -89   |              |

|                              |        |                                                                                                                   | WLCSP package |       | -100  | -84   |              |

|                              |        | $f_{IN}$ = 20kHz,<br>$V_{REF}$ = 4.096V,                                                                          | TQFN package  |       | -100  | -89   |              |

|                              |        | INCC[2:0] = 110,<br>unipolar to COM mode                                                                          | WLCSP package |       | -100  | -84   | 7            |

|                              |        | $f_{IN} = 20kHz,$<br>$V_{REF} = 4.096V,$                                                                          | TQFN package  |       | -100  | -89   |              |

|                              |        | INCC[2:0] = 111,<br>unipolar mode                                                                                 | WLCSP package |       | -100  | -85   |              |

| Spurious Free Dynamic Range  | SFDR   | f <sub>IN</sub> = 20kHz                                                                                           |               |       | 101   |       | dB           |

|                              |        | f <sub>IN</sub> = 100kHz on adjacent                                                                              | TQFN package  |       | -109  |       |              |

| Channel-to-Channel Crosstalk |        | channel(s)                                                                                                        | WLCSP package |       | -85   |       | dB           |

| Sampling Dynamics            | I      | <u> </u>                                                                                                          | <u> </u>      |       |       |       | 1            |

|                              |        | Full bandwidth                                                                                                    |               |       | 21    |       | T            |

| -3dB Input Bandwidth         |        | 1/4 bandwidth                                                                                                     |               |       | 5.5   |       | MHz          |

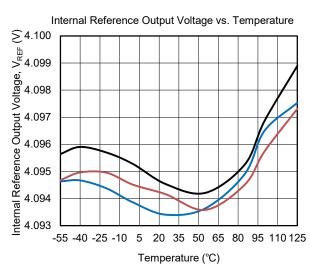

| Internal Reference           |        |                                                                                                                   |               |       |       |       |              |

| REF Output Voltage           |        | At -40°C to +125°C                                                                                                |               | 4.081 | 4.096 | 4.111 | V            |

| REFIN Output Voltage (6)     |        | At +25°C                                                                                                          |               |       | 4.096 |       | V            |

| REF Output Current           |        |                                                                                                                   |               |       | ±300  |       | μA           |

| Temperature Drift            |        |                                                                                                                   |               |       | ±10   |       | ppm/°C       |

| Line Regulation              |        | $V_{DD} = 5V \pm 5\%$                                                                                             |               |       | ±15   |       | ppm/V        |

|                              |        | •                                                                                                                 |               |       | •     |       | -            |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, V_{DD} = 5\text{V}, V_{REF} = 4.096\text{V to } V_{DD}, V_{IO} = 3\text{V}, \text{ all typical values are measured } T_A = +25^{\circ}\text{C}, \text{ unless otherwise noted.})$

| PARAMETER                  | SYMBOL          |                                     | CONDITIONS                               | MIN                   | TYP   | MAX                    | UNITS |

|----------------------------|-----------------|-------------------------------------|------------------------------------------|-----------------------|-------|------------------------|-------|

| Internal Reference         |                 |                                     |                                          | _                     |       |                        |       |

| Long Term Drift            |                 | 1000 hours                          | 3                                        |                       | 160   |                        | ppm   |

| Turn-On Settling Time      |                 | C <sub>REF</sub> = 10µ              | F                                        |                       | 5     |                        | ms    |

| External Reference         |                 |                                     |                                          | •                     |       |                        |       |

| Valta va Davina            |                 | REF input                           |                                          | 0.5                   |       | V <sub>DD</sub>        | V     |

| Voltage Range              |                 | REFIN inp                           | ut (buffered)                            | 1                     | 4.096 | V <sub>DD</sub> - 0.3  | V     |

| Current Drain              |                 | 1MSPS, V                            | <sub>REF</sub> = 5V                      |                       | 300   |                        | μA    |

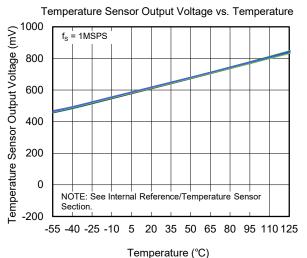

| Temperature Sensor         |                 |                                     |                                          | •                     |       |                        |       |

| Output Voltage (7)         |                 | At +25°C                            |                                          |                       | 620   |                        | mV    |

| Temperature Sensitivity    |                 |                                     |                                          |                       | 2     |                        | mV/°C |

| Digital Inputs             | •               | •                                   |                                          | •                     | •     | 1                      |       |

| Low Input Voltage          | V <sub>IL</sub> |                                     |                                          |                       |       | 0.23 × V <sub>IO</sub> | V     |

| High Input Voltage         | V <sub>IH</sub> |                                     |                                          | 0.7 × V <sub>IO</sub> |       |                        | V     |

| Low Input Current          | I <sub>IL</sub> |                                     |                                          | -1                    |       | 1                      | μΑ    |

| High Input Current         | I <sub>IH</sub> |                                     |                                          | -1                    |       | 1                      | μΑ    |

| Digital Outputs            | •               | •                                   |                                          | •                     | •     | 1                      |       |

| Data Format (8)            |                 |                                     |                                          |                       |       |                        |       |

| Pipeline Delay (9)         |                 |                                     |                                          |                       |       |                        |       |

| Low Output Voltage         | V <sub>OL</sub> | I <sub>SINK</sub> = +50             | 0μΑ                                      |                       |       | 0.4                    | V     |

| High Output Voltage        | V <sub>OH</sub> | I <sub>SOURCE</sub> = -             | 500μA                                    | V <sub>IO</sub> - 0.3 |       |                        | V     |

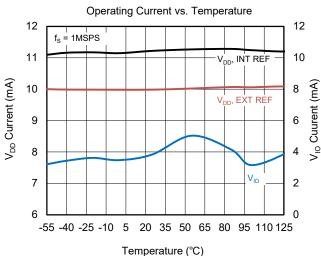

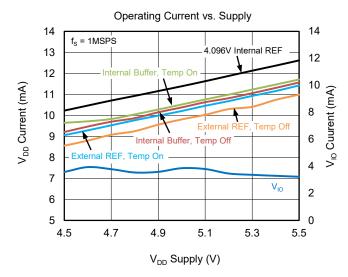

| Power Requirements         |                 |                                     |                                          |                       |       |                        |       |

| Analog Supply Voltage      | $V_{DD}$        | Specified p                         | performance                              | 4.5                   | 5     | 5.5                    | V     |

| Digital I/O Supply Voltage | V <sub>IO</sub> | Specified p                         | performance                              | 1.8                   | 3     | $V_{DD}$               | V     |

| Standby Current (10) (11)  |                 | $V_{DD}$ and $V_{I}$                | o = 5V, at +25°C                         |                       | 1     |                        | μA    |

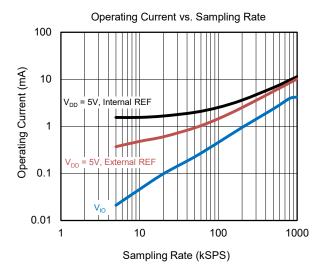

|                            |                 |                                     | 100kSPS throughput                       |                       | 5.4   |                        |       |

| Power Dissipation          |                 | V <sub>DD</sub> = 5V                | 1MSPS throughput                         |                       | 55    | 95                     | mW    |

| ·                          |                 | VDD C1                              | 1MSPS throughput with internal reference |                       | 65    | 100                    |       |

| Temperature Range          |                 |                                     |                                          |                       |       |                        |       |

| Specified Performance      |                 | T <sub>MIN</sub> to T <sub>MA</sub> | ×                                        | -40                   |       | 125                    | °C    |

#### NOTES:

- 1. Refer to the Input Structure section for more details.

- 2. The bandwidth depends on the configuration register settings.

- 3. LSB = Least Significant Bit. 1LSB = 76.3µV in the 5V input range.

- 4. These include the full temperature range variation, but exclude the error contribution from the reference.

- 5. All those parameters are tested with an input signal at -0.5dB for full-scale, unless otherwise specified. The specifications expressed in dBFS are tested with a -0.5dB signal and are recalculated to a full-scale input signal.

- 6. It is the output from the internal band gap.

- 7. The output voltage is internal and present on a dedicated multiplexer input.

- 8. Serial 16-bit straight binary in unipolar mode. Serial 16-bit two's complement in bipolar mode.

- 9. After the conversion is completed, the conversion results are provided immediately.

- 10. All digital inputs are forced to V<sub>IO</sub> or GND as required.

- 11. In the acquisition phase.

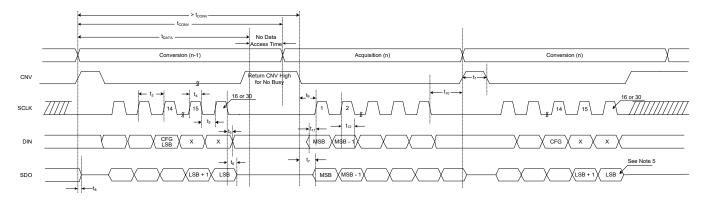

# **TIMING CHARACTERISTICS**

$(V_{DD}$  = 4.5V to 5.5V,  $V_{REF}$  = 4.096V to  $V_{DD}$ ,  $V_{IO}$  = 1.8V to  $V_{DD}$ ,  $T_A$  = -40°C to +125°C, unless otherwise noted.)  $^{(1)}$

| PARAMETER                                                   | SYMBOL            | CONDITIONS                 | MIN                | TYP       | MAX                                          | UNITS |  |  |

|-------------------------------------------------------------|-------------------|----------------------------|--------------------|-----------|----------------------------------------------|-------|--|--|

| Conversion Time: CNV Rising Edge to Data Available          | t <sub>CONV</sub> |                            |                    |           | 830                                          | ns    |  |  |

| Acquisition Time                                            | t <sub>ACQ</sub>  |                            | 170                |           |                                              | ns    |  |  |

| Time between Conversions                                    | t <sub>CYC</sub>  |                            | 1                  |           |                                              | μs    |  |  |

| CNV Pulse Width                                             | t <sub>1</sub>    |                            | 10                 |           |                                              | ns    |  |  |

| Data Write/Read during Conversion                           | t <sub>DATA</sub> |                            |                    |           | 500                                          | ns    |  |  |

| SCLK Period (2)                                             | t <sub>2</sub>    |                            | t <sub>6</sub> + 2 |           |                                              | ns    |  |  |

| SCLK Low Time                                               | 4                 | V <sub>IO</sub> above 3V   | 7                  |           |                                              | no    |  |  |

| SOLK LOW TIME                                               | t <sub>3</sub>    | V <sub>IO</sub> above 1.8V | 8                  |           |                                              | 115   |  |  |

| SCI K High Time                                             | 4                 | V <sub>IO</sub> above 3V   | 7                  |           |                                              | no    |  |  |

| SCLK High Time                                              | $t_4$             | V <sub>IO</sub> above 1.8V | 8                  | ns 500 ns | 115                                          |       |  |  |

| SCLK Falling Edge to Data Remains Valid                     | t <sub>5</sub>    |                            | 4                  |           |                                              | ns    |  |  |

|                                                             |                   | V <sub>IO</sub> above 4.5V |                    |           | 11                                           |       |  |  |

|                                                             |                   | V <sub>IO</sub> above 3V   |                    |           | 12                                           | ns    |  |  |

| SCLK Falling Edge to Data Valid Delay                       | $t_6$             | V <sub>IO</sub> above 2.7V |                    |           | 13                                           |       |  |  |

|                                                             |                   | V <sub>IO</sub> above 2.3V |                    |           | 14                                           |       |  |  |

|                                                             |                   | V <sub>IO</sub> above 1.8V |                    |           | 11<br>12<br>13<br>14<br>15<br>11<br>12<br>13 |       |  |  |

|                                                             |                   | V <sub>IO</sub> above 4.5V |                    |           | 11                                           |       |  |  |

|                                                             |                   | V <sub>IO</sub> above 3V   |                    |           | 12                                           |       |  |  |

| CNV Low to SDO D15 MSB Valid                                | t <sub>7</sub>    | V <sub>IO</sub> above 2.7V |                    |           | 13                                           | ns    |  |  |

|                                                             |                   | V <sub>IO</sub> above 2.3V |                    |           | 14                                           |       |  |  |

|                                                             |                   | V <sub>IO</sub> above 1.8V |                    |           | 16                                           |       |  |  |

| CNV High or Last SCLK Falling Edge to SDO<br>High Impedance | t <sub>8</sub>    |                            |                    |           | 20                                           | ns    |  |  |

| CNV Low to SCLK Rising Edge                                 | t <sub>9</sub>    |                            | 10                 |           |                                              | ns    |  |  |

| Last SCLK Falling Edge to CNV Rising Edge Delay             | t <sub>10</sub>   |                            | 55                 |           |                                              | ns    |  |  |

| DIN Valid Setup Time from SCLK Rising Edge                  | t <sub>11</sub>   |                            | 5                  |           |                                              | ns    |  |  |

| DIN Valid Hold Time from SCLK Rising Edge                   | t <sub>12</sub>   |                            | 5                  |           |                                              | ns    |  |  |

#### NOTES:

- 1. See Figure 2 and Figure 3.

- 2.  $t_2$  must be greater than  $t_3 + t_4$ .

- 3. The  $C_{\text{LOAD}}$  of measuring digital timing is 50pF.

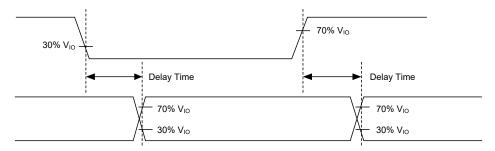

Figure 1. Voltage Levels of Timing Measurement

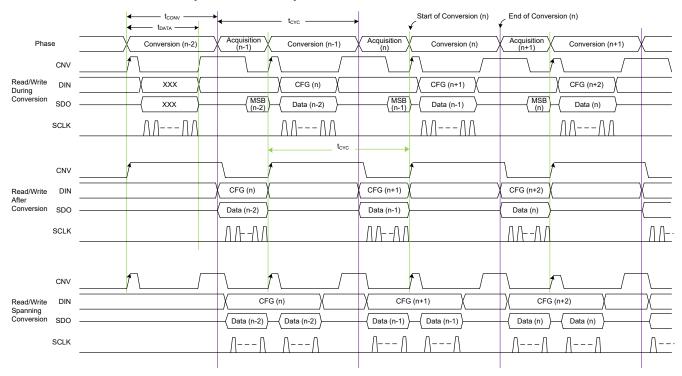

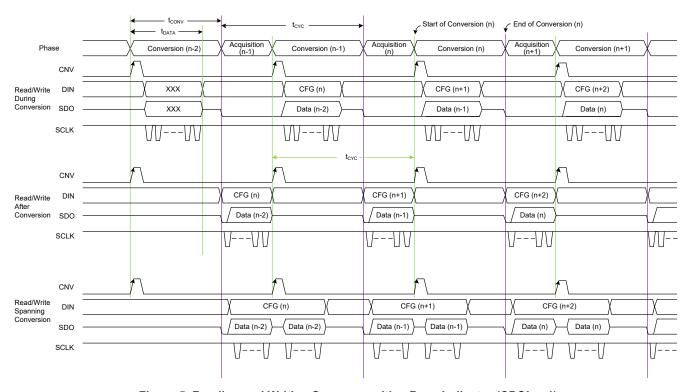

#### **TIMING DIAGRAMS**

#### NOTES:

- 1. No data access time is a transition time between  $t_{CONV}$  and  $t_{DATA}$ . During this time, there should not be any read or write operation.

- 2. The CPOL (clock polarity) bit controls the steady state value of the clock when no data is being transferred.

- 3. Register Write Operation: The first 14-SCLK rising edges update the configuration of register (CFG). It is in MSB first format. It means that the MSB of the register (Bit[13]) is written at the first SCLK rising edge.

- 4. Conversion Result Read Operation: The MSB of ADC conversion result is locked out by the falling edge of CNV, and the following ADC data bit is locked out by the subsequent 15-SCLK falling edges. The 16-SCLK falling edge sets the SDO to high impedance status.

- 5. If CFG readback is disabled, at least 16 SCLKs are needed for the conversion code reading. If CFG readback is enabled, at least 30 SCLKs are needed for both conversion result code and configuration register reading.

Conversion (n-1)

Conversion (n-1)

Acquisition (n)

Conversion (n)

Conversio

Figure 2. Serial Interface Timing without a Busy Indicator (CPOL = 0)

#### NOTES:

- 1. No data access time is a transition time between  $t_{CONV}$  and  $t_{DATA}$ . During this time, there should not be any read or write operation.

- 2. The CPOL (clock polarity) bit controls the steady state value of the clock when no data is being transferred.

- 3. Register Write Operation: The first 14-SCLK rising edges update the configuration of register (CFG). It is in MSB first format. It means that the MSB of the register (Bit[13]) is written at the first SCLK rising edge.

- 4. Conversion Result Read Operation: The BUSY indicate bit '0' on SDO pin is shifted out automatically after the conversion is completed. The subsequent data bit is MSB of ADC conversion result which is locked out by the falling edge of SCLK. To shift out all 16-bit ADC codes, it will take total 16 falling edges of SCLK. And the 17-SCLK falling edge sets the SDO to high impedance status. If CFG readback is disabled, at least 17 SCLK falling edges are needed for the conversion code reading. If CFG readback is enabled, at least 31 SCLK falling edges are needed for both conversion result code and configuration register reading.

Figure 3. Serial Interface Timing with a Busy Indicator (CPOL = 1)

# **TIMING DIAGRAMS (continued)**

Figure 4. Reading and Writing Sequence without a Busy Indicator (CPOL = 0)

Figure 5. Reading and Writing Sequence with a Busy Indicator (CPOL = 1)

### **OPERATING TIMING SEQUENCE**

The SGM51613R4A and SGM51613R8A can be operated in 3 kinds of timing sequence modes. These modes are not configured by software or hardware. The only difference is that reading/writing time slot is put at different operation timing window.

### Reading/Writing during Conversion

As shown in Figure 4 and Figure 5, if the SGM51613R4A and SGM51613R8A are operated in reading (writing) during conversion (cycle #N) mode, the current reading ADC code is the conversion of previous cycle (cycle #N-1). If writing the CFG during conversion (for example, cycle #N+1), the configuration will be effective in next cycle (cycle #N+2).

The transition time is the time between the  $t_{\text{CONV}}$  and  $t_{\text{DATA}}$ . It is not recommended to do any operation during this time, because the device does update conversion result during this time. Any operation may cause data corrupted.

The time  $t_{\text{DATA}}$  is the maximum time which is available for last round conversion result reading.

It is recommended that the host controller should finish reading operation within time of  $t_{DATA}$ , in other words, the host controller should read the ADC code as soon as possible, whatever the sampling speed is adopted by the system.

At least a 50MHz SPI SCLK speed is recommended in this mode

If CNV keeps high at the moment of conversion finishing, the device will not output BUSY indicator signal. Otherwise, the device will output BUSY indicator signal as the first output bit on SDO pin.

#### Reading/Writing after Conversion

As shown in Figure 4 and Figure 5, if the SGM51613R4A and SGM51613R8A are operated in reading (writing) after conversion mode (cycle #N), the reading ADC code is the conversion of last cycle (cycle #N-1). If writing the CFG after conversion (for example, cycle #N+1), the configuration will be effective in next cycle (cycle #N+2).

In this operating mode, all reading (writing) process is issued during acquisition time. As in high speed sampling mode, the minimum acquisition time  $t_{ACQ(MIN)}$  is a short time slot, reading (writing) process is compressed to a short time. It is recommended that reading (writing) after conversion mode is used for low speed sampling application.

If CNV keeps high at the moment of conversion finishing, the device will not output BUSY indicator signal. Otherwise, the device will output BUSY indicator signal as the first output bit on SDO pin.

#### **Reading/Writing Spanning Conversion**

As shown in Figure 4 and Figure 5, if the SGM51613R4A and SGM51613R8A are operated in reading (writing) spanning conversion mode (cycle #N), the current reading ADC code is the conversion of previous cycle (cycle #N-1). If writing the CFG in the current acquisition and conversion cycle (for example, cycle#N+1), the configuration will be effective in next acquisition and conversion cycle (cycle #N+2).

In this mode, the host controller can perform data accessing two times of operation sections to complete one ADC code reading. For these two times of operation sections, it is not necessarily to have to be combined by '8 SCLKs + 8 SCLKs', and it can be any combination, such as '4 SCLKs + 12 SCLKs' or '5 SCLKs + 11 SCLKs'.

There are restrictions for these two times of operation sections. The first operation section must be finished within the acquisition time. The second operation section must be finished within  $t_{\text{DATA}}$  to prevent data corruption, which is similar to reading/writing during conversion. Data accessing is not allowed when CNV is high. For the maximum throughput, the allocation of SCLKs needs to be carefully considered. Because  $t_{\text{ACQ}(\text{MIN})}$  is a restricted parameter, it is a better choice to send out less SCLKs in first round and more in second round to achieve maximum sampling rate.

#### TYPICAL PERFORMANCE CHARACTERISTICS

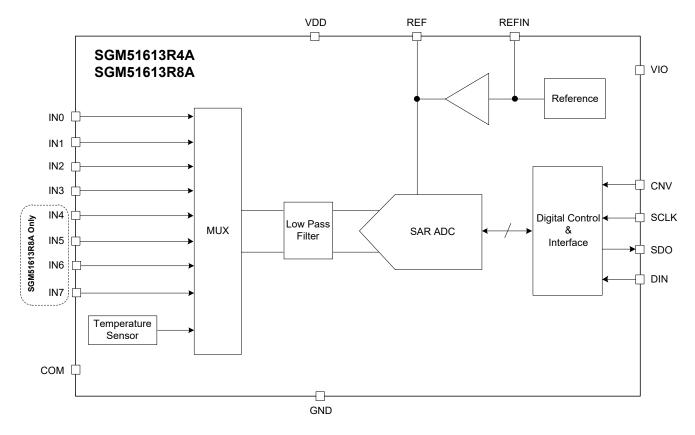

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 6. Block Diagram

#### **DETAILED DESCRIPTION**

The SGM51613R4A and SGM51613R8A are 4-channel/8-channel 16-bit successive approximation ADCs, which are based on the switched capacitor array architecture.

The SGM51613R4A and SGM51613R8A have an on-chip internal oscillator which is used to the clock source of internal conversion. The SCLK is not required for the conversion process.

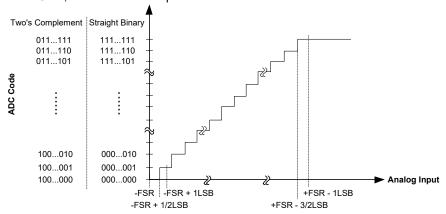

#### **Transfer Functions**

The SGM51613R4A and SGM51613R8A support 5 kinds of input modes, which include single-ended, pseudo differential to COM (referenced to GND or  $1/2V_{REF}$ ) and pseudo differential pairs (referenced to GND or  $1/2V_{REF}$ ). For the first mode, the inputs are configured as single-ended, all eight channels are referenced to GND, and the data output is a

straight binary. For the second and third modes, the inputs are configured as pseudo differential to a common reference (COM). If the COM is connected to GND, then the data output is a straight binary, and if the COM is connected to  $V_{\text{REF}}/2$ , then the data output is two's complement. For the fourth and fifth modes, the inputs are configured as pseudo differential pairs of two adjacent channels. If the INx- is connected to GND, then the data output is a straight binary, if the INx- is connected to  $V_{\text{REF}}/2$ , then the data output is two's complement.

Figure 7 shows the ideal transfer characteristic. Table 1 and Table 2 show the correspondence between the input voltage range and the output code.

Figure 7. ADC Ideal Transfer Function

Table 1. Theoretical Input Voltages and Output Codes of Unipolar Mode

| Description      | Digital Output Code<br>(Straight Binary Hex) | Analog Input of Unipolar Mode<br>V <sub>REF</sub> = 4.096V <sup>(1)</sup> | Analog Input of Unipolar Mode<br>V <sub>REF</sub> = 5.0V <sup>(1)</sup> |

|------------------|----------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------|

| FSR - 1LSB       | 0xFFFF                                       | 4.095938V                                                                 | 4.999923V                                                               |

| Mid-scale + 1LSB | 0x8001                                       | 2.048063V                                                                 | 2.500076V                                                               |

| Mid-scale        | 0x8000                                       | 2.048V                                                                    | 2.5V                                                                    |

| Mid-scale - 1LSB | 0x7FFF                                       | 2.047938V                                                                 | 2.499923V                                                               |

| -FSR + 1LSB      | 0x0001                                       | 62.5µV                                                                    | 76.29µV                                                                 |

| -FSR             | 0x0000                                       | 0V                                                                        | 0V                                                                      |

NOTE: 1. Unipolar Mode: With COM or INx- = 0V or all INx referenced to GND.

Table 2. Theoretical Input Voltages and Output Codes of Bipolar Mode

| Description      | Digital Output Code<br>(Two's Complement Hex) | Analog Input of Bipolar Mode V <sub>REF</sub> = 4.096V <sup>(1)</sup> | Analog Input of Bipolar Mode V <sub>REF</sub> = 5.0V <sup>(1)</sup> |

|------------------|-----------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------|

| FSR - 1LSB       | 0x7FFF                                        | 2.047938V                                                             | 2.499923V                                                           |

| Mid-scale + 1LSB | 0x0001                                        | 62.5µV                                                                | 76.29µV                                                             |

| Mid-scale        | 0x0000                                        | 0V                                                                    | 0V                                                                  |

| Mid-scale - 1LSB | 0xFFFF                                        | -62.5µV                                                               | -76.29µV                                                            |

| -FSR + 1LSB      | 0x8001                                        | -2.047938V                                                            | -2.499923V                                                          |

| -FSR             | 0x8000                                        | -2.048V                                                               | -2.5V                                                               |

NOTE: 1. Bipolar Mode: With COM or INx- =  $V_{REF}/2$ .

#### **Input Configurations**

The SGM51613R4A and SGM51613R8A can be configured as single-ended input or pseudo differential input. In both modes, the positive pin input range is 0V to  $V_{REF}$ , and the negative input pin must be GND or  $V_{REF}/2$ . The selectable configurations are shown in the following 4 conditions:

Configuration A: CFG[12:10] = 111, all 4 channels/8 channels are single-ended input and referenced to GND pin. In this case, each input channel VIN+ is channel0+ to channel3+ (SGM51613R4A)/channel7+ (SGM51613R8A), each input channel VIN- is GND.

Configuration B: CFG[12:10] = 010, all 4 channels/8 channels are pseudo differential to COM pin, and COM pin is connected to  $V_{\text{REF}}/2$ . CFG[12:10] = 110, all 4 channels/8 channels are pseudo differential to COM pin, and COM pin is connected to GND. In this case, each input channel channelx+ is INx+, and the COM pin is INx-.

Configuration C: CFG[12:10] = 00x, two adjacent channels of all inputs are combined as differential pairs, and the channelx- is referenced to  $V_{REF}/2$ . CFG[12:10] = 10X, two adjacent channels of all inputs are combined as differential pairs, and the channelx- is referenced to GND. In this case,

which channel of these adjacent pairs is channelx+ or channelx- is defined by CFG[9:7]. For example, if CFG[9:7] = 000, the positive pin (channel0+) is IN0, and the negative pin (channel0-) is IN1, vice versa.

Configuration D: The chip supports dynamic combined configuration.

More details of input configuration please refer to Figure 8.

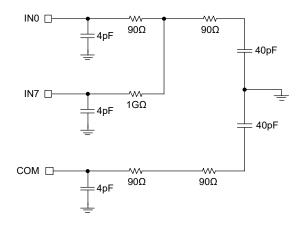

#### Input Structure

The input signal applied to INx and COM must be limited in the range that is listed in Electrical Characteristics table.

The SGM51613R4A and SGM51613R8A are capacitor array SAR ADCs. During the sampling period, there is an input current flowing into the ADC. The peak input current depends on sampling rate, reference voltage, input voltage and signal source impedance.

A driver amplifier is usually suggested to buffer the signal source. It makes the analog input source to charge the equivalent input capacitor (44pF) to a 16-bit accuracy level in the acquisition time. When the input capacitor is fully charged, no further current flows. An equivalent input circuit is shown in Figure 9.

Figure 8. Multiplexed Analog Input Configurations

NOTE: IN0 is assumed to be on, and IN7 is assumed to be off.

Figure 9. Equivalent Analog Input Circuit

#### Sequencer

The SGM51613R4A and SGM51613R8A support automatic channel scanning. The channel configuration can be single-ended, pseudo differential to COM or pseudo differential paired. And the temperature sensor also can be configured into the scan sequence, if it is selected, the temperature sensor will be read after the last ADC channel.

In the single-ended mode and differential to COM mode, the scan sequence starts at IN0 and ends at the channel which is configured by CFG[9:7].

In the differential paired mode, the scan sequence starts at channel0+ (IN0) and channel0- (IN1), and ends at the paired channel set by CFG[9:7]. In the auto scan mode, the positive input is always the even INx and the negative input is always the odd INx, regardless of the setting of CFG[9:7].

The auto scan sequence is initiated by setting the CFG[2:1]. Once the configuration of CFG[13:0] is uploaded to ADC, the DIN must be held low at least 13 SCLK clocks before the next CFG[13:0] is written to ADC. During these clocks, the ADC data can be read normally.

During the scan sequence, the CFG[13:0] can be updated. Once the CFG[11] or CFG[9:7] is changed, the scan sequence will be restarted from IN0 (or paired with IN1 in pseudo differential mode).

When using the sequencer, the channel number corresponding to the conversion result can be achieved by reading back register configuration. Because the register configuration contains channel information and information is updated in real time. In other words, the channel number is constantly updated and corresponds one-to-one with the new conversion result. For example, set the sequencer to sample channel Ch0 to Ch5 for one cycle. After reading the conversion result of Ch0, send another 14 SCLKs and read back the register configuration. Bit[9:7] of CFG must be 0. After reading the conversion result of Ch5, send another 14 SCLKs and read back the register configuration. Bit[9:7] of CFG must be 5. Additionally, if temperature data needs to be read back in sequencer mode, the temperature data will be attached at the end of codes.

#### **Driver Amplifier Choice**

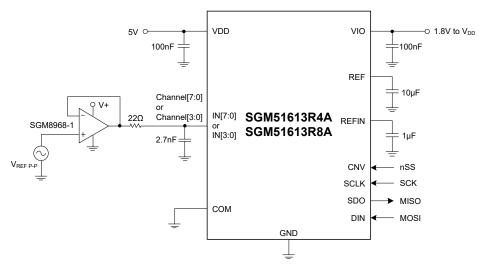

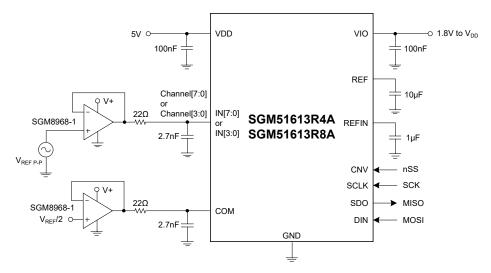

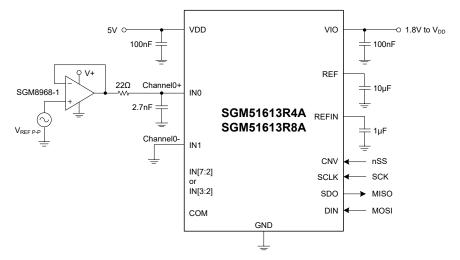

To get the best performance, an input buffer amplifier is recommended. Refer to Figure 10 to Figure 13.

Figure 10. Typical Application with Single-Ended Input or Differential Input to a Common Reference (to GND)

Figure 11. Typical Application with Differential Input to a Common Reference (to 1/2V<sub>REF</sub>)

Figure 12. Typical Application with Differential Pairs Input (Reference to GND)

Figure 13. Typical Application with Differential Pairs Input (Reference to 1/2V<sub>REF</sub>)

# 16-Bit, 1MSPS, 4-Channel/8-Channel Low Power, Serial Interface ADC

# **DETAILED DESCRIPTION (continued)**

#### **Voltage Reference**

The SGM51613R4A and SGM51613R8A have an on-chip low drift reference. The chip can work with internal reference or external reference. More details are described in Table 3 and Table 4.

If the internal reference is enabled, the voltage is output on the REFIN pin which needs a decoupling capacitor. If the voltage is used for the other circuit, a buffer amplifier is recommended.

If an external reference is used for the better system performance, it can be connected to REFIN pin or REF pin. When it is connected to VREFIN pin, the internal reference buffer must be enabled at the same time. When it is connected to REF pin, an external buffer is optional.

#### **Temperature Sensor**

To enable the internal temperature sensor, the internal reference must be active and the internal buffer enabling is not necessary at the same time.

The temperature sensor is a single-ended input to ADC and referenced to GND. Its output is straight binary.

The output code of the temperature sensor can be described as follows:

Temperature Sensor Code = Temperature Sensor Voltage  $\times$  (Reference Voltage)/( $2^{16}$  - 1)

In which, the voltage of the temperature sensor output is typically 620mV at +25  $^{\circ}$ C. The sensitivity of temperature senor is about 2mV/ $^{\circ}$ C.

**Table 3. Register Content**

| D[13] | D[12] | D[11]     | D[10] | D[9] | D[8]     | D[7] | D[6] | D[5] | D[4]     | D[3] | D[2] | D[1]  | D[0] |

|-------|-------|-----------|-------|------|----------|------|------|------|----------|------|------|-------|------|