# SGM4591Q Automotive Low Voltage 16-Bit I<sup>2</sup>C and SMBus Low-Power I/O Expander

#### **GENERAL DESCRIPTION**

The SGM4591Q is a general-purpose parallel input and output (I/O) expander device, which consists of two lanes and 8 bits parallel I/O expansion. The device communicates with processor through two-line bidirectional I<sup>2</sup>C bus (or SMBus), supporting I<sup>2</sup>C standard mode (100kHz) and I<sup>2</sup>C fast mode (400kHz) clock frequency. The SGM4591Q provides a simple solution for the devices that need additional I/Os, such as LEDs, buttons, sensors, etc.

The SGM4591Q is specified for automotive applications, which may select device address by the A0 and A1 pins. The SGM4591Q features an interrupt generated on the nINT whenever the state of input port changes. An output anomaly may also be indicated by the nINT pin when the corresponding Output Anomaly Indication port register is set to 1. The SGM4591Q can cycle the power supply and cause a power-on reset to reset itself to the default state. In addition, the device can use a hardware nRESET pin to reset itself to the default state.

The device is AEC-Q100 qualified (Automotive Electronics Council (AEC) standard Q100 Grade 1) and it is suitable for automotive applications.

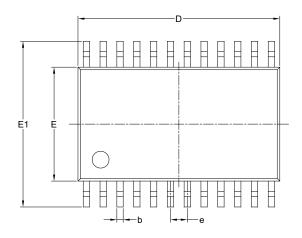

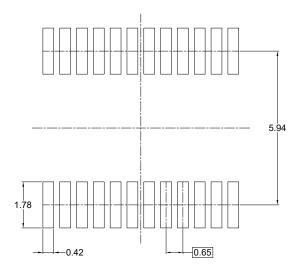

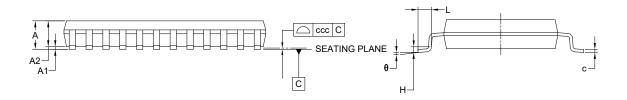

The SGM4591Q is available in a Green TSSOP-24 package and supports -40°C to +125°C temperature range.

#### **FEATURES**

- AEC-Q100 Qualified for Automotive Applications

Device Temperature Grade 1

T<sub>A</sub> = -40°C to +125°C

- 1.65V to 5.5V Input Voltage Range

- Parallel I<sup>2</sup>C I/O Expander

- 5V Tolerant Input and Output Ports

- Active Low Reset Input

- Active Low Interrupt Output

- Support 400kHz I<sup>2</sup>C Fast Mode

- Internal Power-on Reset

- No Glitch on Power-up

- Polarity Inversion Register

- Compatible with Most Processors

- Select Device Address by Two Pins (up to Four Devices)

- Latched Outputs Drive LEDs Directly

- Latch-up Performance (>100mA) to Meet JESD

78 Class II Standard

- -40°C to +125°C Operating Temperature Range

- Available in a Green TSSOP-24 Package

#### **APPLICATIONS**

I<sup>2</sup>C GPIO Expansion

Automotive Infotainment and Body Electronics, ADAS, Hybrid Vehicles, Electric Vehicles and Powertrains Automation in Industrial, Factory, Building, Test and Measurement

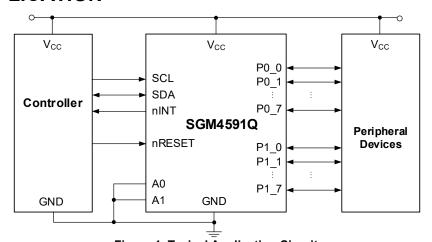

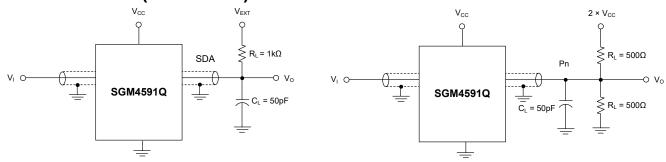

### TYPICAL APPLICATION

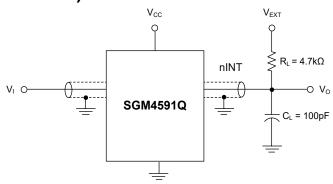

Figure 1. Typical Application Circuit

### PACKAGE/ORDERING INFORMATION

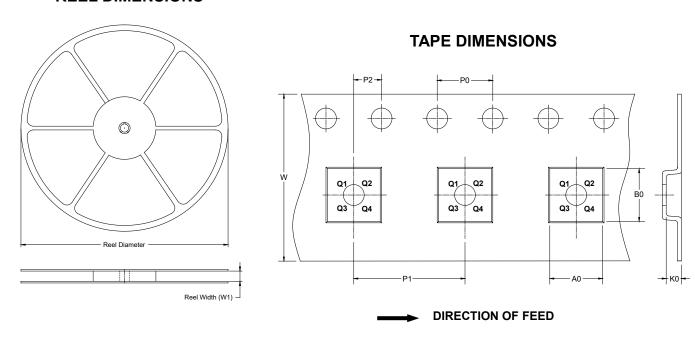

| MODEL    | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING | PACKING<br>OPTION   |  |

|----------|------------------------|-----------------------------------|--------------------|--------------------|---------------------|--|

| SGM4591Q | TSSOP-24               | -40°C to +125°C                   | SGM4591QTS24G/TR   | 0RQTS24G<br>XXXXX  | Tape and Reel, 4000 |  |

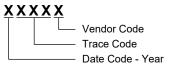

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage Range, V <sub>CC</sub> 0.5V to 6V                                                        |

|---------------------------------------------------------------------------------------------------------|

| Input Voltage Range <sup>(1)</sup> , V <sub>I</sub>                                                     |

| Output Voltage Range <sup>(1)</sup> , V <sub>0</sub>                                                    |

| Input Clamp Current, I <sub>IK</sub> (V <sub>I</sub> < 0V)20mA                                          |

| Output Clamp Current, $I_{OK}$ ( $V_O < 0V$ )20mA                                                       |

| Input-Output Clamp Current, I <sub>IOK</sub> (V <sub>O</sub> < 0V or V <sub>O</sub> > V <sub>CC</sub> ) |

|                                                                                                         |

| ±20mA                                                                                                   |

| Continuous Output Low Current, $I_{OL}$ ( $V_O = 0V$ to $V_{CC}$ ) 50mA                                 |

| Continuous Output High Current, $I_{OH}$ ( $V_O$ = 0V to $V_{CC}$ ) -50mA                               |

| Continuous Current through GND250mA                                                                     |

| Continuous Current through V <sub>CC</sub> 160mA                                                        |

| Package Thermal Resistance                                                                              |

| TSSOP-24, θ <sub>JA</sub> 105.8°C/W                                                                     |

| TSSOP-24, θ <sub>JB</sub> 73.0°C/W                                                                      |

| TSSOP-24, θ <sub>JC</sub>                                                                               |

| Junction Temperature+150°C                                                                              |

| Storage Temperature Range65°C to +150°C                                                                 |

| Lead Temperature (Soldering, 10s)+260°C                                                                 |

| ESD Susceptibility (2)(3)                                                                               |

| HBM±4000V                                                                                               |

| CDM±1000V                                                                                               |

|                                                                                                         |

#### NOTES:

- 1. When the input and output current ratings are observed, the input and I/O negative voltage ratings may be exceeded.

- 2. For human body model (HBM), all pins comply with AEC-Q100-002 specification.

- 3. For charged device model (CDM), all pins comply with AEC-Q100-011 specification.

#### RECOMMENDED OPERATING CONDITIONS

| Supply Voltage Range, $V_{CC}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| For P0_7-0, P1_7-0 Configured as Inputs <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| High-Level Input Voltage, V <sub>IH</sub> SCL, SDA, A0, A1, nRESET, P0_7-0, P1_7-00.7 × V <sub>CC</sub> (MIN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Low-Level Input Voltage, V <sub>IL</sub> SCL, SDA, A0, A1, nRESET, P0_7-0, P1_7-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| -10mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Low-Level Output Current, I <sub>OL</sub> (P0_7-0, P1_7-0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| T <sub>J</sub> ≤ +65°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $T_J \le +65^{\circ}C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $T_{J} \le +65^{\circ}C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| $T_J \le +65^{\circ}C$ 25mA $T_J = +85^{\circ}C$ 18mA $T_J = +105^{\circ}C$ 9mA $T_J = +125^{\circ}C$ 4.5mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $T_J \le +65^{\circ}C$ 25mA $T_J = +85^{\circ}C$ 18mA $T_J = +105^{\circ}C$ 9mA $T_J = +125^{\circ}C$ 4.5mA $T_J = +135^{\circ}C$ 3.5mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $\begin{split} T_{J} & \leq +65^{\circ}\text{C} & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & & &$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $T_J \le +65^{\circ}C$ 25mA $T_J = +85^{\circ}C$ 18mA $T_J = +105^{\circ}C$ 9mA $T_J = +125^{\circ}C$ 4.5mA $T_J = +135^{\circ}C$ 3.5mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $\begin{split} T_{J} &\leq +65^{\circ}\text{C} & \\ T_{J} &= +85^{\circ}\text{C} & \\ T_{J} &= +105^{\circ}\text{C} & \\ T_{J} &= +125^{\circ}\text{C} & \\ T_{J} &= +125^{\circ}\text{C} & \\ T_{J} &= +135^{\circ}\text{C} & \\ T_{J} &= +85^{\circ}\text{C} & \\ & \\ Low-Level Output Current, I_{OL} (nINT, SDA) \\ T_{J} &\leq +85^{\circ}\text{C} & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\$ |

| $\begin{split} T_{J} &\leq +65^{\circ}\text{C} & 25\text{mA} \\ T_{J} &= +85^{\circ}\text{C} & 18\text{mA} \\ T_{J} &= +105^{\circ}\text{C} & 9\text{mA} \\ T_{J} &= +125^{\circ}\text{C} & 4.5\text{mA} \\ T_{J} &= +135^{\circ}\text{C} & 3.5\text{mA} \\ \text{Low-Level Output Current, I}_{OL} \text{ (nINT, SDA)} \\ T_{J} &\leq +85^{\circ}\text{C} & 6\text{mA} \\ T_{J} &= +105^{\circ}\text{C} & 3\text{mA} \end{split}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### NOTE

1. Voltages applied above  $V_{\text{CC}}$  will cause an increase in  $I_{\text{CC}}$ .

### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

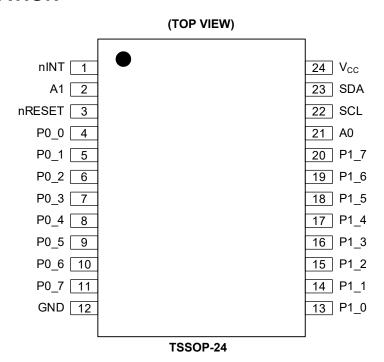

### **PIN CONFIGURATION**

#### PIN DESCRIPTION

| PIN   | NAME            | TYPE (1) | DESCRIPTION                                                                                                                        |

|-------|-----------------|----------|------------------------------------------------------------------------------------------------------------------------------------|

| 1     | nINT            | 0        | Open-Drain Output. A pull-up resistor is used to connect to V <sub>CC</sub> .                                                      |

| 2     | A1              | 1        | Analog Input A1. Connected to V <sub>CC</sub> or GND.                                                                              |

| 3     | nRESET          | I        | Active Low Reset Input. If there is no active connection, this pin is connected to the $V_{\text{CC}}$ pin via a pull-up resistor. |

| 4-11  | P0_0-7          | I/O      | P0 to P7 of Port 0 Input/Output. Default as an input at power-on.                                                                  |

| 12    | GND             | _        | Ground.                                                                                                                            |

| 13-20 | P1_0-7          | I/O      | P0 to P7 of Port 1 Input/Output. Default as an input at power-on.                                                                  |

| 21    | A0              | I        | Analog Input A0. Connected to V <sub>CC</sub> or GND.                                                                              |

| 22    | SCL             | I        | Clock Signal.                                                                                                                      |

| 23    | SDA             | I/O      | Data Signal.                                                                                                                       |

| 24    | V <sub>cc</sub> | _        | Supply Voltage.                                                                                                                    |

NOTE: 1. I = Input, O = Output, I/O = Input and Output.

## **ELECTRICAL CHARACTERISTICS**

(Full = -40°C to +125°C, all typical values are measured at  $T_A$  = +25°C and  $V_{CC}$  = 1.8V, 2.5V, 3.3V or 5V, unless otherwise noted.)

| PARAMETER                                         | SYMBOL            | CONDITIONS                                              |                                                         |                                           | MIN  | TYP  | MAX | UNITS |    |

|---------------------------------------------------|-------------------|---------------------------------------------------------|---------------------------------------------------------|-------------------------------------------|------|------|-----|-------|----|

| Input Diode Clamp Voltage                         | V <sub>IK</sub>   | I <sub>I</sub> = -18mA, V <sub>CC</sub> = 1.65V to 5.5V |                                                         |                                           | -1.2 |      |     | V     |    |

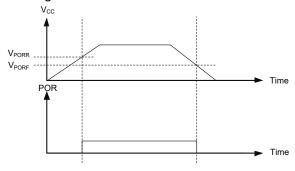

| Power-on Reset Voltage on V <sub>CC</sub> Rising  | V <sub>PORR</sub> | $V_1 = V_{CC}$ or GND, $V_{CC} = 1.65V$ to 5.5V         |                                                         |                                           |      | 1.2  | 1.5 | V     |    |

| Power-on Reset Voltage on V <sub>CC</sub> Falling | V <sub>PORF</sub> | V <sub>I</sub> = V <sub>CC</sub> or G                   | ND, $V_{CC} = 1.65V$ to                                 | 5.5V                                      | 0.55 | 1.0  |     | V     |    |

|                                                   |                   |                                                         |                                                         | V <sub>CC</sub> = 1.65V                   |      | 1.20 |     |       |    |

|                                                   |                   |                                                         | V <sub>CC</sub> = 2.3V                                  |                                           | 1.90 |      |     |       |    |

|                                                   |                   | $I_{OH} = -8mA$                                         | V <sub>CC</sub> = 3.0V                                  |                                           | 2.65 |      |     |       |    |

|                                                   |                   |                                                         | V <sub>CC</sub> = 3.6V                                  |                                           | 3.30 |      |     |       |    |

| P-Port High-Level Output                          |                   |                                                         | V <sub>CC</sub> = 4.75V                                 |                                           | 4.45 |      |     |       |    |

| Voltage (1)                                       | V <sub>OH</sub>   |                                                         | V <sub>CC</sub> = 1.65V                                 |                                           | 1.10 |      |     | V     |    |

|                                                   |                   |                                                         | V <sub>CC</sub> = 2.3V                                  |                                           | 1.80 |      |     |       |    |

|                                                   |                   | I <sub>OH</sub> = -10mA                                 | V <sub>CC</sub> = 3.0V                                  |                                           | 2.60 |      |     |       |    |

|                                                   |                   |                                                         | V <sub>CC</sub> = 3.6V                                  |                                           | 3.20 |      |     | 1     |    |

|                                                   |                   |                                                         | V <sub>CC</sub> = 4.75V                                 |                                           | 4.35 |      |     |       |    |

|                                                   |                   | SDA                                                     | $V_{CC} = 1.65V \text{ to } 5.5$                        | V, V <sub>OL</sub> = 0.4V                 | 3    |      |     |       |    |

|                                                   | I <sub>OL</sub>   |                                                         | D D (2)                                                 | $V_{CC}$ = 1.65V to 5.5V, $V_{OL}$ = 0.5V |      | 8    |     |       | mA |

| Low-Level Output Current                          |                   | P-Port (2)                                              | V <sub>CC</sub> = 1.65V to 5.5                          | V, V <sub>OL</sub> = 0.7V                 | 10   |      |     |       |    |

|                                                   |                   | nINT                                                    | $V_{CC} = 1.65V \text{ to } 5.5$                        | 10                                        |      |      |     |       |    |

|                                                   |                   | SCL, SDA                                                |                                                         |                                           |      | ±1   |     |       |    |

| Input Leakage Current                             | l <sub>1</sub>    | A0, A1,<br>nRESET                                       | $V_1 = V_{CC}$ or GND, $V_{CC} = 1.65V$ to 5.5V         |                                           |      |      | ±1  | μΑ    |    |

| High-Level Input Current                          | I <sub>IH</sub>   | P-Port                                                  | $V_{I} = V_{CC}, V_{CC} = 1.6$                          | 5V to 5.5V                                |      |      | 1   |       |    |

| Low-Level Input Current                           | I <sub>IL</sub>   | P-Port                                                  | $V_I = GND, V_{CC} = 1$                                 | .65V to 5.5V                              |      |      | -1  | μA    |    |

|                                                   |                   |                                                         | $V_1 = V_{CC}$ or GND,<br>$I_0 = 0A$ ,<br>I/O = inputs, | V <sub>CC</sub> = 5.5V                    |      | 25.8 | 40  |       |    |

|                                                   |                   | Operating                                               |                                                         | V <sub>CC</sub> = 3.6V                    |      | 14.0 | 30  |       |    |

|                                                   |                   | Mode                                                    | $f_{SCL} = 400kHz,$                                     | V <sub>CC</sub> = 2.7V                    |      | 9.5  | 18  |       |    |

|                                                   |                   |                                                         | no load                                                 | V <sub>CC</sub> = 1.95V                   |      | 6.5  | 11  |       |    |

|                                                   |                   |                                                         | V <sub>I</sub> = V <sub>CC.</sub>                       | V <sub>CC</sub> = 5.5V                    |      | 5.0  | 15  |       |    |

| Quissaant Supply Current                          |                   |                                                         | I <sub>O</sub> = 0A,<br>I/O = inputs,                   | V <sub>CC</sub> = 3.6V                    |      | 2.5  | 8   |       |    |

| Quiescent Supply Current                          | I <sub>CC</sub>   |                                                         | $f_{SCL} = 0kHz,$                                       | V <sub>CC</sub> = 2.7V                    |      | 1.5  | 5   | μA    |    |

|                                                   |                   | Standby                                                 | no load                                                 | V <sub>CC</sub> = 1.95V                   |      | 0.9  | 3.5 |       |    |

|                                                   |                   | Mode                                                    | V <sub>I</sub> = GND,                                   | V <sub>CC</sub> = 5.5V                    |      | 5.0  | 15  |       |    |

|                                                   |                   |                                                         | $I_O = 0A$ ,                                            | V <sub>CC</sub> = 3.6V                    |      | 2.5  | 8   |       |    |

|                                                   |                   |                                                         | I/O = inputs,<br>f <sub>SCL</sub> = 0kHz,               | V <sub>CC</sub> = 2.7V                    |      | 1.5  | 5   |       |    |

|                                                   |                   |                                                         | no load                                                 | V <sub>CC</sub> = 1.95V                   |      | 0.9  | 3.5 |       |    |

| Input Capacitance                                 | Cı                | SCL                                                     | V <sub>I</sub> = V <sub>CC</sub> or GND                 | V <sub>CC</sub> = 1.65V to 5.5V           |      | 6    |     | pF    |    |

| Input/Output Conscitons                           |                   | SDA                                                     | \/ =\/ ar CND                                           | \/ = 1.65\/ to 5.5\/                      |      | 7.5  |     | ,r    |    |

| Input/Output Capacitance                          | C <sub>I/O</sub>  | P-Port                                                  | $V_{I/O} = V_{CC}$ or GND                               | $V_{CC} = 1.65V \text{ to } 5.5V$         |      | 9.5  |     | pF    |    |

#### NOTES:

- 1. Each octal (P0\_7-0 and P1\_7-0) has a limitation to the maximum allowed  $I_{OL}(100mA)$  externally and a total of 200mA for a device at  $T_J \le +85^{\circ}C$ .

- 2. The maximum total sourced current by all I/Os must be less than 160mA.

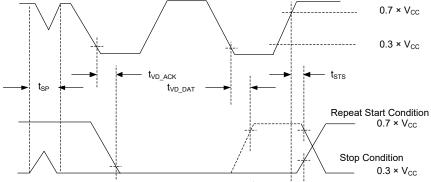

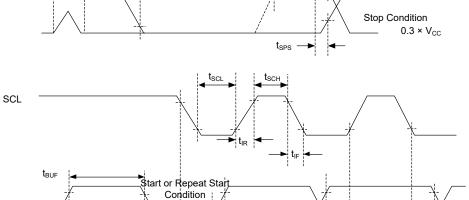

# I<sup>2</sup>C INTERFACE TIMING REQUIREMENTS

$(T_A = -40$ °C to +125°C, unless otherwise noted.)

| PARAMETER                                           | SYMBOL              | CONDITIONS                               | MIN (1)                         | TYP | MAX (1) | UNITS |

|-----------------------------------------------------|---------------------|------------------------------------------|---------------------------------|-----|---------|-------|

| I <sup>2</sup> C Bus—Standard Mode                  |                     |                                          |                                 |     |         |       |

| Clock Frequency                                     | f <sub>SCL</sub>    |                                          | 0                               |     | 100     | kHz   |

| Clock High Time                                     | t <sub>SCH</sub>    |                                          | 4                               |     |         | μs    |

| Clock Low Time                                      | t <sub>SCL</sub>    |                                          | 4.7                             |     |         | μs    |

| Spike Time                                          | t <sub>SP</sub>     |                                          |                                 |     | 50      | ns    |

| Serial-Data Setup Time                              | t <sub>SU_DAT</sub> |                                          | 250                             |     |         | ns    |

| Serial-Data Hold Time                               | t <sub>HD_DAT</sub> |                                          | 0                               |     |         | ns    |

| Input Rise Time                                     | t <sub>IR</sub>     |                                          |                                 |     | 1000    | ns    |

| Input Fall Time                                     | t <sub>IF</sub>     |                                          |                                 |     | 300     | ns    |

| Output Fall Time                                    | t <sub>OF</sub>     | 10pF to 400pF bus                        |                                 |     | 300     | ns    |

| Bus Free Time between Stop and Start                | t <sub>BUF</sub>    |                                          | 4.7                             |     |         | μs    |

| Setup Time for Start or<br>Repeated Start Condition | t <sub>STS</sub>    |                                          | 4.7                             |     |         | μs    |

| Hold Time for Start or<br>Repeated Start Condition  | t <sub>STH</sub>    |                                          | 4                               |     |         | μs    |

| Setup Time for Stop Condition                       | t <sub>SPS</sub>    |                                          | 4                               |     |         | μs    |

| Valid Data Time                                     | t <sub>VD_DAT</sub> | SCL low to SDA output valid              |                                 |     | 3.45    | μs    |

| Valid Data Time of ACK<br>Condition                 | t <sub>VD_ACK</sub> | ACK signal from SCL low to SDA (out) low |                                 |     | 3.45    | μs    |

| Bus Capacitive Load                                 | Св                  |                                          |                                 |     | 400     | pF    |

| I <sup>2</sup> C Bus—Fast Mode                      |                     |                                          |                                 |     |         |       |

| Clock Frequency                                     | f <sub>SCL</sub>    |                                          | 0                               |     | 400     | kHz   |

| Clock High Time                                     | t <sub>SCH</sub>    |                                          | 0.6                             |     |         | μs    |

| Clock Low Time                                      | t <sub>SCL</sub>    |                                          | 1.3                             |     |         | μs    |

| Spike Time                                          | t <sub>SP</sub>     |                                          |                                 |     | 50      | ns    |

| Serial-Data Setup Time                              | t <sub>SU_DAT</sub> |                                          | 100                             |     |         | ns    |

| Serial-Data Hold Time                               | t <sub>HD_DAT</sub> |                                          | 0                               |     |         | ns    |

| Input Rise Time                                     | t <sub>IR</sub>     |                                          | 20                              |     | 300     | ns    |

| Input Fall Time                                     | t <sub>IF</sub>     |                                          | 20 ×<br>(V <sub>CC</sub> /5.5V) |     | 300     | ns    |

| Output Fall Time                                    | t <sub>OF</sub>     | 10pF to 400pF bus                        | 20 ×<br>(V <sub>CC</sub> /5.5V) |     | 300     | ns    |

| Bus Free Time between Stop and Start                | t <sub>BUF</sub>    |                                          | 1.3                             |     |         | μs    |

| Setup Time for Start or<br>Repeated Start Condition | t <sub>STS</sub>    |                                          | 0.6                             |     |         | μs    |

| Hold Time for Start or<br>Repeated Start Condition  | t <sub>sth</sub>    |                                          | 0.6                             |     |         | μs    |

| Setup Time for Stop Condition                       | t <sub>SPS</sub>    |                                          | 0.6                             |     |         | μs    |

| Valid Data Time                                     | t <sub>VD_DAT</sub> | SCL low to SDA output valid              |                                 |     | 0.9     | μs    |

| Valid Data Time of ACK Condition                    | t <sub>VD_ACK</sub> | ACK signal from SCL low to SDA (out) low |                                 |     | 0.9     | μs    |

| Bus Capacitive Load                                 | Св                  |                                          |                                 |     | 400     | pF    |

NOTE: 1. Specified by design and characterization, not production tested.

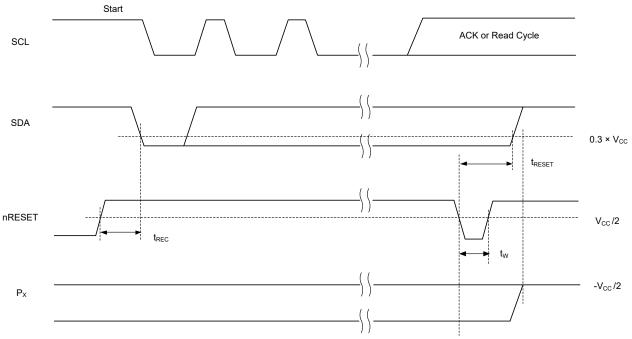

## **nreset timing requirements**

$(T_A = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETER                | SYMBOL             | CONDITIONS                      | MIN | TYP | MAX | UNITS |

|--------------------------|--------------------|---------------------------------|-----|-----|-----|-------|

| Reset Pulse Duration (1) | t <sub>W</sub>     |                                 | 6   |     |     | ns    |

| Reset Recovery Time (1)  | t <sub>REC</sub>   |                                 | 0   |     |     | ns    |

| Time to Reset            |                    | V <sub>CC</sub> = 2.3V to 5.5V  | 450 |     |     | 20    |

| Time to Reset            | t <sub>RESET</sub> | V <sub>CC</sub> = 1.65V to 2.3V | 550 |     |     | ns    |

## **SWITCHING CHARACTERISTICS**

$(T_A = -40$ °C to +125°C,  $C_L \le 100$ pF, unless otherwise noted.)

| PARAMETER                  | SYMBOL             | CON                            | MIN                             | TYP | MAX | UNITS |     |

|----------------------------|--------------------|--------------------------------|---------------------------------|-----|-----|-------|-----|

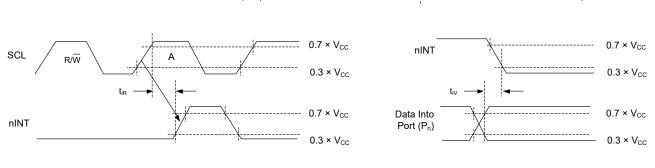

| Interrupt Valid Time       | t <sub>IV</sub>    | From P-Port to nINT            |                                 |     | 4   | μs    |     |

| Interrupt Reset Delay Time | t <sub>IR</sub>    | From SCL to nINT               |                                 |     | 4   | μs    |     |

| Data Outrat Valid Time     | From SCL to P-Port | V <sub>CC</sub> = 2.3V to 5.5V |                                 |     | 200 | ns    |     |

| Data Output Valid Time     | t <sub>DV</sub>    | FIOIII SCL to P-Poit           | V <sub>CC</sub> = 1.65V to 2.3V |     |     | 300   | ns  |

| Data Input Setup Time (1)  | t <sub>DSU</sub>   | From P-Port to SCL             |                                 | 2   |     |       | CLK |

| Data Input Hold Time (1)   | t <sub>DH</sub>    | From P-Port to SCL             | From P-Port to SCL              |     |     |       | μs  |

NOTE: 1. Specified by design and characterization, not production tested.

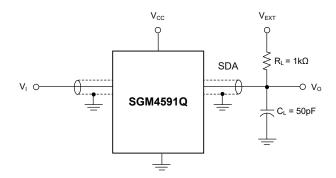

## **TEST CIRCUIT**

Figure 2. I<sup>2</sup>C Interface Load Circuit

#### NOTES:

- 1. R<sub>L</sub> refers to load resistance. C<sub>L</sub> refers to load capacitance (includes jig and probe).

- 2. All inputs are supplied by generators featured by: PRR  $\leq$  10MHz,  $Z_O = 50\Omega$ ,  $t_R/t_F \leq$  30ns.

### **WAVEFORMS**

Figure 3. I<sup>2</sup>C Interface Voltage Waveforms

$t_{\text{SU\_DAT}}$

$t_{\text{HD\_DAT}}$

SDA

## **TEST CIRCUIT (continued)**

Figure 4. Interrupt Load Circuit

#### NOTES:

- 1. R<sub>L</sub> refers to load resistance. C<sub>L</sub> refers to load capacitance (includes jig and probe).

- 2. All inputs are supplied by generators featured by: PRR  $\leq$  10MHz,  $Z_O$  = 50 $\Omega$ ,  $t_R/t_F \leq$  30ns.

#### **WAVEFORMS** SCL SDA START I<sup>2</sup>C Slave Address Data Byte ACK Data Byte ACK NACK STOP Read from Data Into Data 2 Data 3 Data 4 Data 5 Port t<sub>DSU</sub>-

Figure 5. Interrupt Voltage Waveforms

nINT

## **TEST CIRCUIT (continued)**

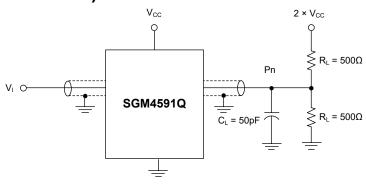

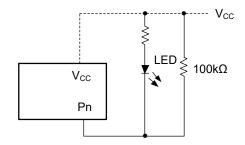

Figure 6. P-Port Load Circuit

#### NOTES:

- 1. R<sub>L</sub> refers to load resistance. C<sub>L</sub> refers to load capacitance (includes jig and probe).

- 2. All inputs are supplied by generators featured by: PRR  $\leq$  10MHz,  $Z_O$  = 50 $\Omega$ ,  $t_R/t_F \leq$  30ns.

- 3.  $t_{DV}$  is measured from 0.7 ×  $V_{CC}$  on SCL to 50% I/O ( $P_n$ ) output.

- 4. The outputs are measured one by one with a transition every measurement.

### **WAVEFORMS**

Figure 7. P-Port Voltage Waveforms

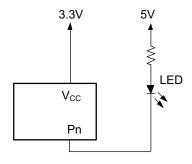

## **TEST CIRCUIT (continued)**

Figure 8. Reset Load Circuits

#### NOTES:

- 1. R<sub>L</sub> refers to load resistance. C<sub>L</sub> refers to load capacitance (includes jig and probe).

- 2. All inputs are supplied by generators featured by: PRR  $\leq$  10MHz,  $Z_O$  = 50 $\Omega$ ,  $t_r/t_f \leq$  30ns.

- 3. I/Os are designed as inputs.

- 4. The outputs are measured one by one with a transition every measurement.

#### **WAVEFORMS**

Figure 9. Reset Load Circuits and Voltage Waveforms

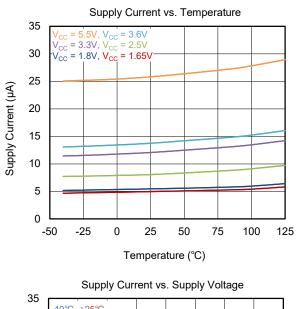

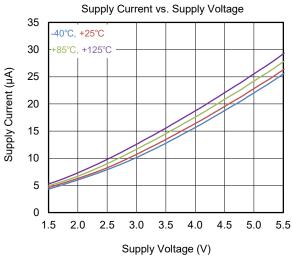

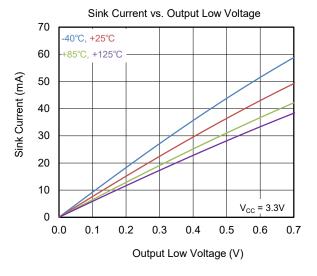

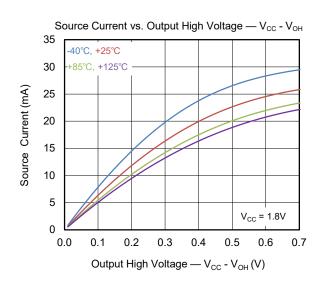

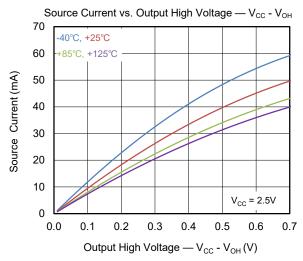

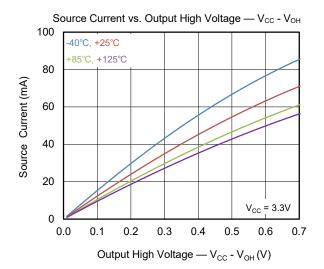

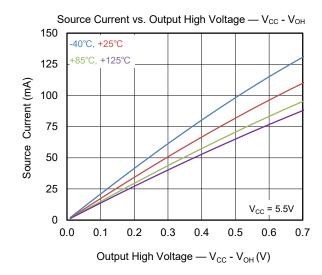

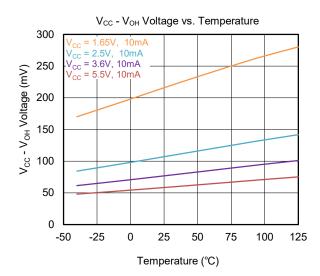

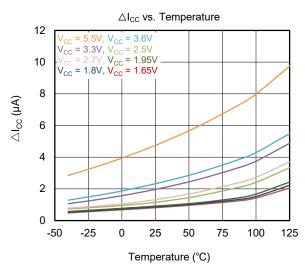

### TYPICAL PERFORMANCE CHARACTERISTICS

$T_A$  = +25°C, unless otherwise noted.

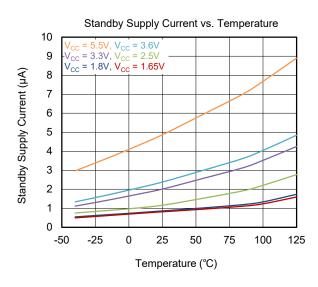

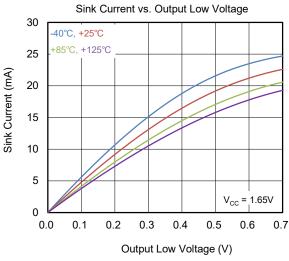

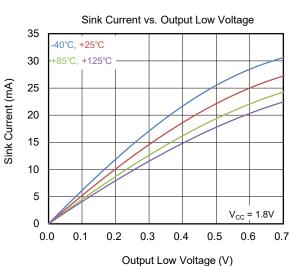

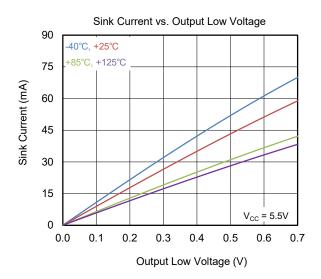

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_A$  = +25°C, unless otherwise noted.

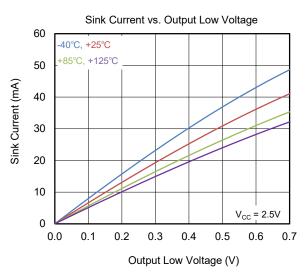

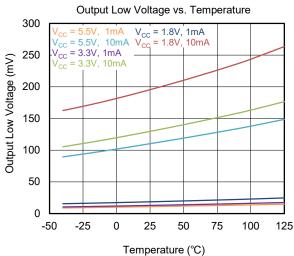

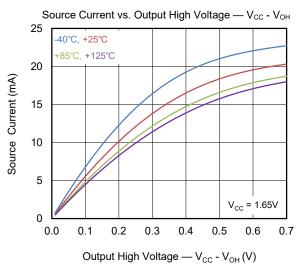

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_A = +25$ °C, unless otherwise noted.

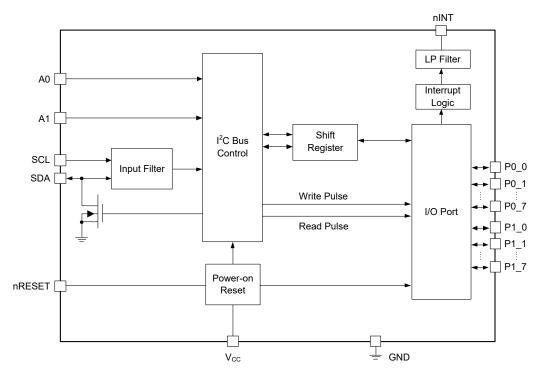

## **FUNCTIONAL BLOCK DIAGRAM**

NOTE: All I/Os are set as inputs when reset.

Figure 10. Functional Block Diagram (Positive Logic)

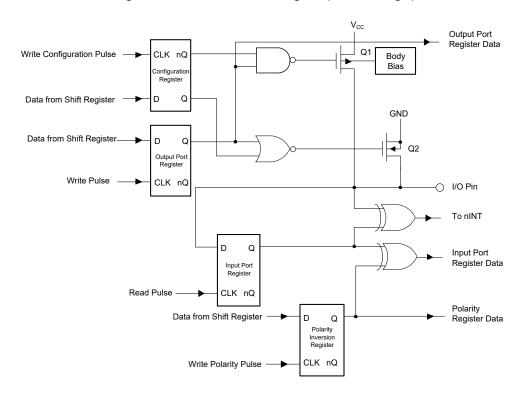

NOTE: At power-on reset, all registers return to default values.

Figure 11. Simplified Schematic of P-Port Inputs or Outputs

#### **DETAILED DESCRIPTION**

#### Overview

The SGM4591Q is a multi-use parallel I/O expander device, which consists of two lanes, 8 bits parallel I/O expansion. It communicates with processor through two-line bidirectional I<sup>2</sup>C bus (or SMBus).

The SGM4591Q has two groups of 8-bit registers, including Input Port x (x = 0, 1), Output Port x, Polarity Inversion x, Configuration Port x, Output Mode Configuration x, and Output Anomaly Port x. When the device is powered on, all ports are designed as inputs. Writing to the register Configuration Port x could set the corresponding ports as input or output. Writing '1' to the Polarity Inversion x register can invert the polarity of the input register. The register Output Mode Configuration x can configure ports as push-pull or open-drain when the corresponding ports are set as output mode. And the Output Anomaly Port x can be enabled to indicate the situation of output short-circuit. All registers can be read by the processor.

By setting the nRESET input low, the processor can reset the SGM4591Q when a timeout or other improper operation occurs. The power-on reset can initialize the I<sup>2</sup>C state machine, and reset all registers. Putting nRESET low could also perform the same reset operation without repowering the device.

Any input state differing from its corresponding Input Port x register can cause the open-drain interrupt (nINT) activation. If the Output Anomaly Port x is enabled, in the situation that the output state differs from its corresponding Output Port register, the nINT output is also activated. It is used to indicate an output anomaly to the processor.

The SGM4591Q can remain a simple target device. The nINT can be connected to the input of a processor, the remote I/O can inform the processor whether there is incoming data changing or an output anomaly without  $\rm I^2C$  bus.

The SGM4591Q may select device address by the A0 and A1 pins and allow up to four devices to share the same I<sup>2</sup>C or SMBus.

## **Feature Description**

#### I/O Ports

The I/Os would be in high-impedance state when configured as an input because FETs Q1 and Q2 are off.

The input voltage may be raised above  $V_{\text{CC}}$  to a maximum of 5.5V.

When the I/Os are designed as an output, the state of Output Port x decides whether Q1 or Q2 to be enabled. In this case, the low-impedance paths exist between the ports pin and either  $V_{\rm CC}$  or GND. For proper operation, the external voltage applied to this port pin must not exceed the recommended voltage. The output mode can be set as push-pull or open-drain via the Output Mode Configuration x register.

#### nRESET Input

Holding the nRESET pin low for a minimum of  $t_W$  can cause a reset.  $I^2C$  state machine is reset and all registers are held in their default values until nRESET is high once again. The input needs to be high via a pull-up resistor when there is no active connection.

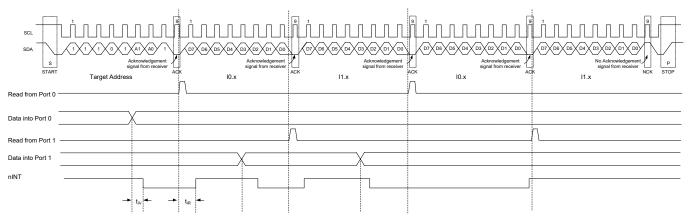

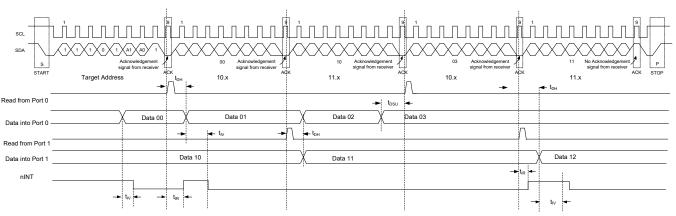

#### Interrupt (nINT) Output

Any change of the state of port pins can generate an interrupt in the input mode. It also can be generated when output anomaly occurs and the nINT indicator function is enabled in the output mode. The actual pin value can be read from the Input Port registers. Therefore, the abnormal output bits can be identified.

The nINT signal becomes valid after the interrupt valid time  $(t_{\text{IV}})$ . The nINT would be reset when the state of port pins changes to the original setting or the corresponding Input Port x register is read. In the read mode, the resetting occurs at the acknowledge (ACK) bit after the rising edge of SCL signal. Pay attention to that the nINT is reset at the ACK before sending the changed data bytes. Interrupt that occurs during the ACK clock pulse may be lost (or be very short) due to resetting of interrupt during this pulse. After resetting, each change of the port pin in the input mode would be detected and transmitted as nINT.

There is no effect on the interrupt circuit when operating a read or a write to another device. If the state of a port pin is not consistent with the content of the corresponding Input Port x register, a false interrupt may occur when changing an I/O port from an output state to an input state. Due to that each 8-bit port is read independently, when port 0 causes an interrupt, it will not be cleared by reading port 1, or vice versa.

nINT needs a pull-up resistor to  $V_{\text{CC}}$  due to the open-drain structure.

#### **Function Mode**

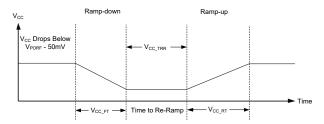

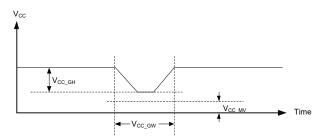

#### Power-on Reset (POR)

During power-on, the POR function keeps the SGM4591Q in a reset state until  $V_{\text{CC}}$  reaches  $V_{\text{PORR}}$ . Then, the SGM4591Q would release the reset condition and initialize its register to the default state. After that,  $V_{\text{CC}}$  must be lowered to  $V_{\text{PORF}}$  and then backs to the operating voltage for a power-reset cycle.

#### **Programming**

#### I<sup>2</sup>C Interface

The SGM4591Q has a standard bidirectional I<sup>2</sup>C interface that may be controlled by a processor that can configure or read the state of this device. The SGM4591Q has a specific device address to distinguish it from other targets on the same I<sup>2</sup>C bus.

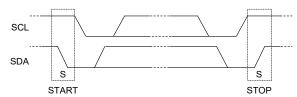

I<sup>2</sup>C is a well-known 2-wire serial communication interface that can connect one (or more) master device(s) to some slave devices for two-way communication. The bus lines are named serial data (SDA) and serial clock (SCL). The device that initiates a data transfer is a master. A master generates the SCL signal. Slave devices have unique addresses to identify. A master is typically a micro controller or a digital signal processor. Bus lines are pulled high by weak current source or pull-up resistors and in logic high state with no clocking when the bus is idle. The SDA and SCL pins are open-drain. Data transfer can only begin when the bus is idle. When both the SDA and SCL lines are high after the stop condition, the bus is considered idle.

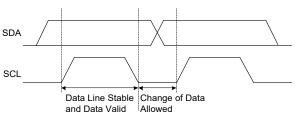

Figure 12 and Figure 13 show the general processor for a processor accessing a target device:

- 1. Send data to target:

- Controller-transmitter sends a START signal and device address to the target receiver.

- Controller-transmitter sends data to target receiver.

- Controller-transmitter sends a STOP signal to terminate this transfer.

- 2. Receive data from target:

- Controller-receiver sends a START signal and device address to the target transmitter.

- Controller-receiver sends the relevant register address to the target transmitter.

- Controller-receiver receives data from the target transmitter.

- Controller-receiver sends a STOP signal to terminate this transfer.

Figure 12. I<sup>2</sup>C Bus in START and STOP Conditions

Figure 13. Bit Transfer

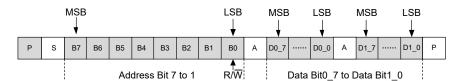

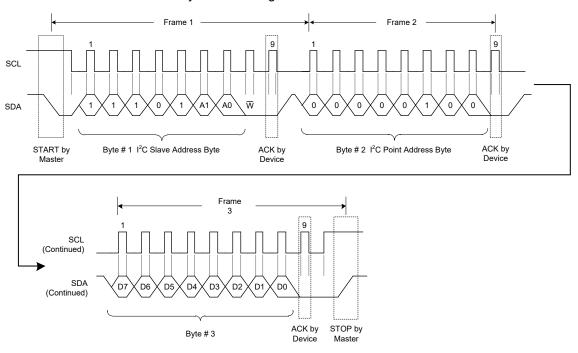

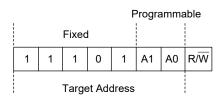

The interface definition is illustrated in Table 1.

**Table 1. Interface Definition**

|                                    |             | Bits |      |      |      |      |      |             |  |  |  |  |

|------------------------------------|-------------|------|------|------|------|------|------|-------------|--|--|--|--|

| Byte                               | D7<br>(MSB) | D6   | D5   | D4   | D3   | D2   | D1   | D0<br>(LSB) |  |  |  |  |

| I <sup>2</sup> C Target<br>Address | 1           | 1    | 1    | 0    | 1    | A1   | A0   | R/W         |  |  |  |  |

| P0_x I/O<br>Data Bus               | P0_7        | P0_6 | P0_5 | P0_4 | P0_3 | P0_2 | P0_1 | P0_0        |  |  |  |  |

| P1_x I/O<br>Data Bus               | P1_7        | P1_6 | P1_5 | P1_4 | P1_3 | P1_2 | P1_1 | P1_0        |  |  |  |  |

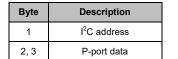

#### **Bus Transactions**

The controller and the SGM4591Q can finish data transactions through  $R/\overline{W}$  commands.

Registers are located in the memory of target containing information, no matter what it is the configuration information or some sampled data sent to the controller. The controller instructs the SGM4591Q to perform some tasks through writing information to these registers.

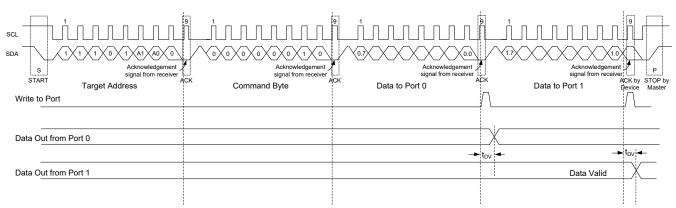

**WRITE:** The controller sends a START condition accompanied by the address of target, and the last bit

is written as '0', which indicates a 'write' command. After receiving the ACK signal, the controller sends the register address. The SGM4591Q sends the ACK signal again, indicating it is ready. Then, the controller starts transmitting the register data to the target until the controller has sent all the necessary data. The controller could send a STOP condition to terminate the transmission.

See the **Control Register and Command Byte** section for more details. Figure 14 indicates the write of a single byte to a target register.

Figure 14. Write to Register

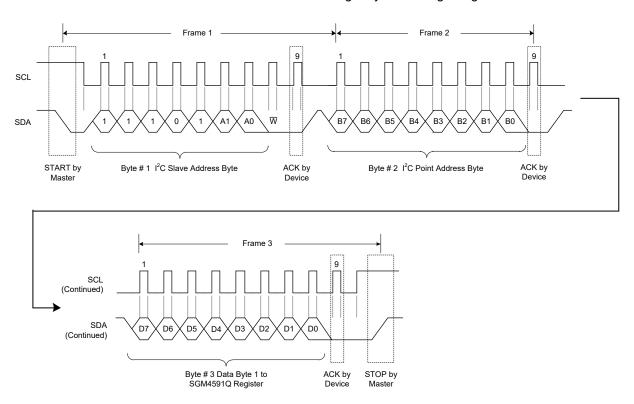

Figure 15 indicates the write to the Polarity Inversion register.

Figure 15. Write to the Polarity Inversion Port 0 Register

Figure 16 indicates the write to Output Port register.

Figure 16. Write to Output Port 0 Register

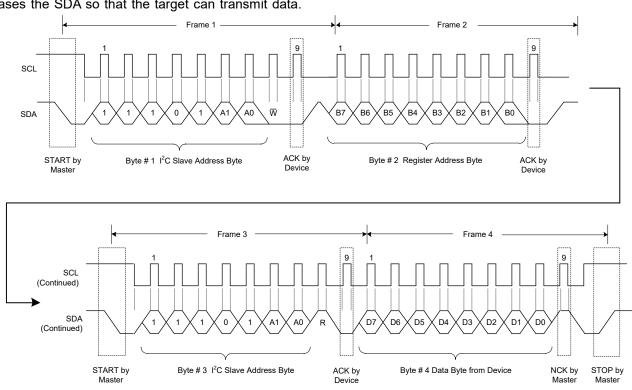

**READ:** 'Read' command is similar to 'write' command, but needs a few extra steps. Reading from a target requests that the controller must firstly give the target an instruction about which register it wants to read from. This step is consistent with 'write', and the last bit is written '0' (indicating a 'write'), followed by the register it wants to read from. After receiving the ACK signal, the controller sends a START again with the last bit written '1' (indicating a 'read'). Then, the SGM4591Q sends the ACK signal again, indicating it is ready. And the controller releases the SDA but still supplies the clock signal to the target. In this transaction, the controller becomes the receiver of data, and the SGM4591Q becomes the transmitter.

The controller continues to supply the clock signal but releases the SDA so that the target can transmit data.

The controller must send an ACK to the target at the end of every byte of data so that the target could send more data. The controller receives the number of bytes as expected, then it sends an NACK to the target to stop data transaction and release the SDA bus. After this, the controller sends a STOP condition.

If the command byte is not set through a write first, and a read is needed by the controller, the device NACKs until a command byte register address is set as described above.

See the **Control Register and Command Byte** section for more details. Figure 17 indicates the reading of a single byte from a target register.

Figure 17. Read from Register

After a single write request to a register, a repeated start signal occurs, then the requested register is used for the read request. Note that when reading multiple bytes, the data is clocked into the register on the rising edge of the ACK signal pulse before data is transferred. After reading the first byte, other bytes may also be

read. However, the current data just reflects the information in the other register of the pair. For instance, if Input Port 0 is read, Input Port1 is read next. During read operation, if a RESTART occurs, the data may be lost due to that the internal register has already been changed to the other register of the pair.

The number of received data bytes in one read transmission has no limitation, but the controller must not acknowledge the data when the final byte is

received. Figure 18 and Figure 19 show two different scenarios.

#### NOTES:

- 1. A STOP condition could stop data transaction at any time. Despite this, the data presented during the recent validation phase is valid (output mode), assuming that the command byte was previously set to 00.

- 2. This figure eliminates the command byte transfer, restart and target address call between the initial target address call and actual data transfer from P port (more details refers to Reads).

Figure 18. Scenario 1 of Read Input Port Register

#### NOTES:

- 1. A STOP condition could stop data transaction at any time. Despite this, the data presented during the recent validation phase is valid (output mode), assuming that the command byte was previously set to 00.

- 2. This figure eliminates the command byte transfer, restart, and target address call between the initial target address call and actual data transfer from the P port (more details refers to Reads).

Figure 19. Scenario 2 of Read Input Port Register

#### REGISTER MAPS

All registers are 8-bit and individual bits are named from D[7] (MSB) to D[0] (LSB).

## I<sup>2</sup>C Register Address Map

Figure 20 shows the address byte of the SGM4591Q.

Figure 20. SGM4591Q Address

Table 2 shows the address reference of the SGM4591Q.

**Table 2. Address Reference**

| Parar | neter | I <sup>2</sup> C Bus Target Address |             |  |  |  |

|-------|-------|-------------------------------------|-------------|--|--|--|

| A1    | A0    | Decimal                             | Hexadecimal |  |  |  |

| L     | L     | 116                                 | 74          |  |  |  |

| L     | Н     | 117                                 | 75          |  |  |  |

| Н     | L     | 118                                 | 76          |  |  |  |

| Н     | Н     | 119                                 | 77          |  |  |  |

The last bit of the target address defines the read or write operation. 1 (high) performs the read operation, while 0 (low) performs the write operation.

#### **Control Register and Command Byte**

After acknowledging the address byte of target device successfully, the controller-transmitter would send a command byte stored in the control register. Four bits of the command byte state the operation (read or write) and the internal register (input, output, polarity inversion, configuration, output mode and output anomaly indication) that is affected. These registers support read or write operation via the I<sup>2</sup>C bus. Command bytes are sent only during write transmission.

After sending a command byte, the addressed register pair continues to be accessed by reads until a new command byte is sent. Figure 21 shows the control register bits.

MSB

LSB

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

0

0

B3

B2

B1

B0

Figure 21. Control Register Bits

I<sup>2</sup>C Slave Register Addresses of SGM4591Q: 0x0X

| ADDRESS | REGISTER NAME                             | TYPE | D[7]    | D[6] | D[5] | D[4] | D[3]  | D[2] | D[1] | D[0] |

|---------|-------------------------------------------|------|---------|------|------|------|-------|------|------|------|

| 0x00    | Input Port 0 Register                     | R    |         |      |      | 10[  | 7:0]  |      |      |      |

| 0x01    | Input Port 1 Register                     | R    |         |      |      | 11[  | 7:0]  |      |      |      |

| 0x02    | Output Port 0 Register                    | R/W  |         |      |      | 00   | [7:0] |      |      |      |

| 0x03    | Output Port 1 Register                    | R/W  |         |      |      | 01   | [7:0] |      |      |      |

| 0x04    | Polarity Inversion Port 0 Register        | R/W  | N0[7:0] |      |      |      |       |      |      |      |

| 0x05    | Polarity Inversion Port 1 Register        | R/W  |         |      |      | N1[  | 7:0]  |      |      |      |

| 0x06    | Configuration Port 0 Register             | R/W  | C0[7:0] |      |      |      |       |      |      |      |

| 0x07    | Configuration Port 1 Register             | R/W  | C1[7:0] |      |      |      |       |      |      |      |

| 0x08    | Output Mode Setting Port 0 Register       | R/W  |         |      |      | oco  | [7:0] |      |      |      |

| 0x09    | Output Mode Setting Port 1 Register       | R/W  |         |      |      | OC1  | [7:0] |      |      |      |

| 0x0A    | Output Anomaly Indication Port 0 Register | R/W  |         |      |      | OAC  | [7:0] |      |      |      |

| 0x0B    | Output Anomaly Indication Port 1 Register | R/W  |         |      |      | OA1  | [7:0] |      |      |      |

Bit Types:

R/W: Read/Write bit(s)

R: Read only bit(s)

RC: Bit(s) cleared to 0 by being read

PORV: Power-on Reset Value

n: Parameter code formed by the bits as an unsigned binary number.

## **REG0x00:** Input Port 0 Register [Reset = 0xXX]

| BITS   | BIT NAME | DEFAULT   | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------|----------|-----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[7:0] | 10[7:0]  | xxxx xxxx | R    | This input port 0 register reflects the incoming logic levels of the corresponding pins. The register just only acts on the read operation, no matter whether the port pins are defined as I/O by the configuration port registers (REG0x06 and REG0x07). Writing to the two registers has no effect. The default value is set by the external port pins' logic level. Before a read operation, send a write transmission with a command byte to show the I <sup>2</sup> C device that this register is accessed next. |

### **REG0x01:** Input Port 1 Register [Reset = 0xXX]

| BITS   | BIT NAME | DEFAULT   | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------|----------|-----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[7:0] | l1[7:0]  | xxxx xxxx | K    | This input port 1 register reflects the incoming logic levels of the corresponding pins. The register just only acts on the read operation, no matter whether the port pins are defined as I/O by the configuration port registers (REG0x06 and REG0x07). Writing to the two registers has no effect. The default value is set by the external port pins' logic level. Before a read operation, send a write transmission with a command byte to show the I <sup>2</sup> C device that this register is accessed next. |

## **REG0x02: Output Port 0 Register [Reset = 0xFF]**

| BITS   | BIT NAME | DEFAULT   | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                             |

|--------|----------|-----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[7:0] | O0[7:0]  | 1111 1111 | R/W  | The output port 0 register reflects the outgoing logic levels of the corresponding pins defined as outputs by the configuration port registers (REG0x06 and REG0x07). The bit values in this register have no effect on the pins configured as input. Reading from the register reflects the value that is in the flip-flop controlling the output selection, not the actual pin value. |

### **REG0x03: Output Port 1 Register [Reset = 0xFF]**

| BITS   | BIT NAME | DEFAULT   | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                             |

|--------|----------|-----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|