# SGM51652H4/SGM51652H8 16-Bit, 500kSPS, 4- and 8-Channel, Single Supply, SAR ADCs with Bipolar Input Ranges

### GENERAL DESCRIPTION

The SGM51652H4 and SGM51652H8 are 4-channel and 8-channel, 16-bit resolution, high-precision successive approximation (SAR) analog-to-digital converters (ADCs).

These ADCs are powered by a single unipolar 5V, and support true bipolar  $\pm 10.24$ V,  $\pm 5.12$ V, and  $\pm 2.56$ V inputs, as well as unipolar input ranges of 0V to 10.24V and 0V to 5.12V. The input range is configured by software.

These chips provide over-voltage protection up to ±20V at the input.

These chips have an on-chip high accuracy and low drift 10ppm reference.

The input impedance of these chips is  $\sim 1 M\Omega$  and it is independent of input range selection.

The digital interface is compatible to the traditional SPI protocol.

### **FEATURES**

- Supported Input Ranges:

- Bipolar Single-Ended Ranges: ±10.24V, ±5.12V, and ±2.56V

- Unipolar Single-Ended Ranges: 0V to 10.24V and 0V to 5.12V

- Bipolar Differential Ranges: ±10.24V, ±5.12V, and ±2.56V

- Supply Voltage Ranges:

- Analog Supply: 5V

- I/O Supply: 1.65V to 5V

- On-Chip Reference: 4.096V

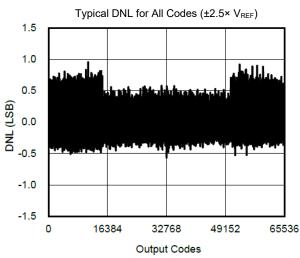

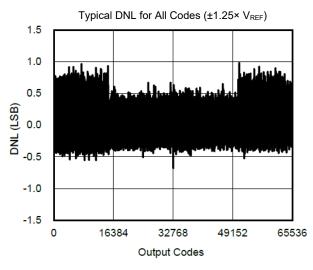

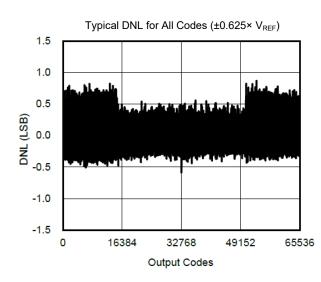

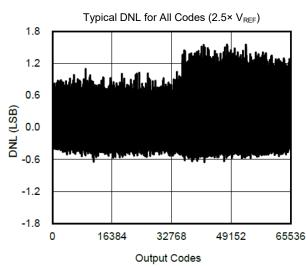

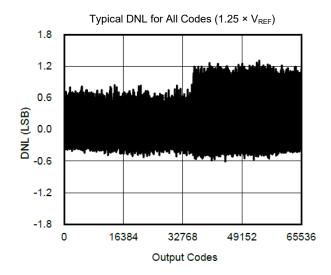

- Differential Nonlinearity (DNL): -0.6/+0.9LSB (TYP)

- Integral Nonlinearity (INL): ±1.3LSB (TYP)

- Signal-to-Noise Ratio (SNR): 89.5dB (TYP)

- Total Harmonic Distortion (THD): -99dB (TYP)

- Alarm Features

- Daisy-Chain Operation

- -40°C to +125°C Operating Temperature Range

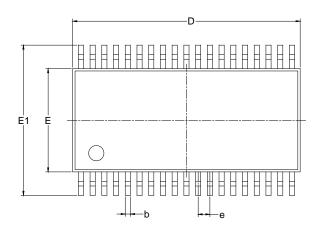

- Available in a Green TSSOP-38 Package

## **APPLICATIONS**

**Power Automation**

**Protection Relays**

PLC Analog Input Modules

**Factory Automation**

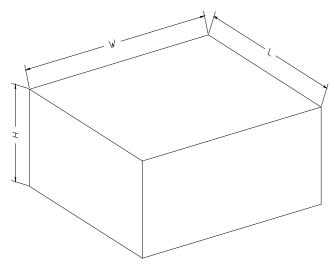

## PACKAGE/ORDERING INFORMATION

| MODEL               | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER    | PACKAGE<br>MARKING           | PACKING<br>OPTION   |

|---------------------|------------------------|-----------------------------------|-----------------------|------------------------------|---------------------|

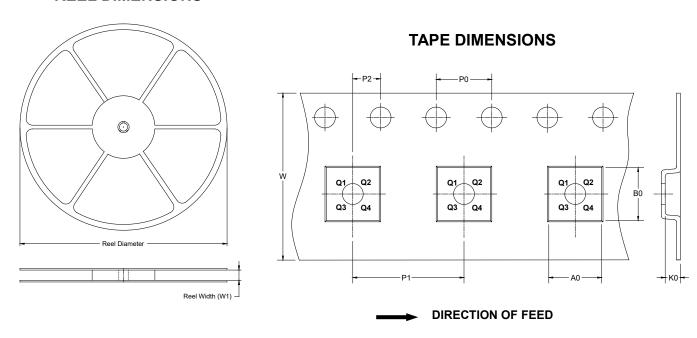

| SGM51652H4 TSSOP-38 | TSSOP-38               | -40°C to +125°C                   | SGM51652H4XTS38G-S/TR | SGM51652H4<br>XTS38<br>XXXXX | Tape and Reel, 500  |

| 3GINI31032H4        | 1550P-36               | -40 C to +125 C                   | SGM51652H4XTS38G/TR   | SGM51652H4<br>XTS38<br>XXXXX | Tape and Reel, 4000 |

| COME46EOLIO         | TSSOD 30               | 40°C to 1405°C                    | SGM51652H8XTS38G-S/TR | SGM51652H8<br>XTS38<br>XXXXX | Tape and Reel, 500  |

| SGM51652H8          | TSSOP-38               | -40°C to +125°C                   | SGM51652H8XTS38G/TR   | SGM51652H8<br>XTS38<br>XXXXX | Tape and Reel, 4000 |

### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

| AIN_nP, AIN_nN to AGND (1)     | 20V to 20V                     |

|--------------------------------|--------------------------------|

| AIN_nP, AIN_nN to AGND (2)     | 11V to 11V                     |

| AVDD to AGND                   | 0.3V to 6V                     |

| AUX_INP to AGND                | 0.3V to AVDD + 0.3V            |

| AUX_INN to AGND                | 0.3V to AVDD + 0.3V            |

| AGND to DGND                   | 0.3V to + 0.3V                 |

| REFCAP to REFGND or REFIO      | to REFGND0.3V to $5.7\mbox{V}$ |

| REFGND to AGND                 |                                |

| DVDD to DGND                   | 0.3V to AVDD                   |

| Digital Input Pins to DGND     | 0.3V to DVDD + 0.3V            |

| Digital Output Pins to DGND    | 0.3V to DVDD + 0.3V            |

| Junction Temperature           | +150°C                         |

| Storage Temperature Range      | 65°C to +150°C                 |

| Lead Temperature (Soldering, 1 | 0s)+260°C                      |

| ESD Susceptibility             |                                |

| HBM (Analog Input Pins: AIN_nl | P, AIN_nN)±7000V               |

| HBM (Other Pins)               | ±2000V                         |

| CDM                            | ±500V                          |

|                                |                                |

#### NOTES:

- 1. AVDD = 5V or offers a low impedance of  $< 30k\Omega$ .

- 2. AVDD = floating with an impedance >  $30k\Omega$ .

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

#### RECOMMENDED OPERATING CONDITIONS

| _                    | _            | _          | _       | _      |    |

|----------------------|--------------|------------|---------|--------|----|

| Analog Supply Volta  | age Range, A | VDD        |         |        |    |

|                      |              | 4.75V to   | 5.25V,  | 5V (TY | P) |

| Digital Supply Volta | ge Range, D  | VDD        |         |        |    |

|                      |              | 1.65V to A | VDD, 3. | 3V (TY | P) |

| Operating Tempera    | ture Range   |            | 40°C t  | o +125 | °C |

### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

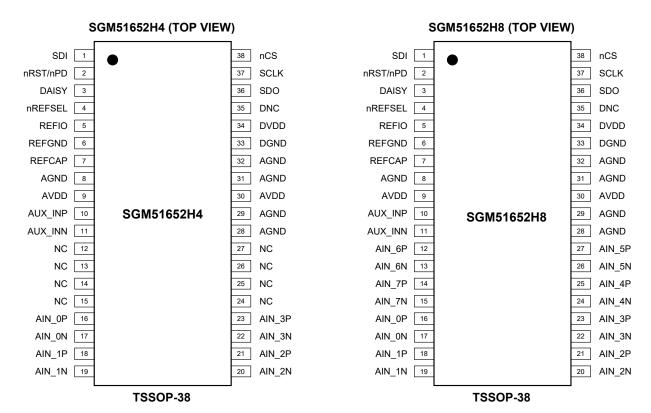

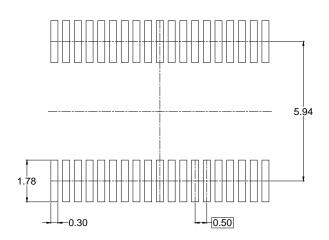

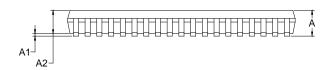

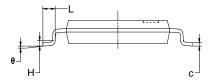

## PIN CONFIGURATIONS

## **PIN DESCRIPTION**

| PIN | NA                    | ME      | TYPE (1)                                                                 | FUNCTION                                                    |  |

|-----|-----------------------|---------|--------------------------------------------------------------------------|-------------------------------------------------------------|--|

| PIN | SGM51652H4 SGM51652H8 |         | ITPE                                                                     | FUNCTION                                                    |  |

| 1   | SI                    | Ol      | DI                                                                       | Serial Data Input.                                          |  |

| 2   | nRST                  | /nPD    | DI                                                                       | Dual-Function Pin: Reset/Power-Down the Device. Active low. |  |

| 3   | DAI                   | SY      | DI                                                                       | Chain the Serial Data Input in Daisy-Chain Mode.            |  |

| 4   | nREFSEL               |         | nREFSEL DI Active Low. When it is enabled, the internal reference is on. |                                                             |  |

| 5   | REFIO                 |         | AIO                                                                      | Internal Reference Output and External Reference Input Pin. |  |

| 6   | REF(                  | GND     | Al                                                                       | Reference Ground Pin.                                       |  |

| 7   | REF                   | CAP     | AO                                                                       | ADC Reference Decoupling Capacitor Pin.                     |  |

| 8   | AG                    | ND      | Р                                                                        | Analog Ground.                                              |  |

| 9   | AVI                   | AVDD    |                                                                          | Analog Power Supply.                                        |  |

| 10  | AUX_INP               |         | Al                                                                       | Positive Auxiliary Input Pin.                               |  |

| 11  | AUX                   | AUX_INN |                                                                          | Negative Auxiliary Input Pin.                               |  |

# **PIN DESCRIPTION (continued)**

| DIN               | NA         | ME         | TYPE (1) | FUNCTION                                   |

|-------------------|------------|------------|----------|--------------------------------------------|

| PIN               | SGM51652H4 | SGM51652H8 | ITPE     | FUNCTION                                   |

| 12                | NC         | AIN_6P     | AI       | Channel 6 Positive Analog Input.           |

| 13                | NC         | AIN_6N     | Al       | Channel 6 Negative Analog Input.           |

| 14                | NC         | AIN_7P     | Al       | Channel 7 Positive Analog Input.           |

| 15                | NC         | AIN_7N     | AI       | Channel 7 Negative Analog Input.           |

| 16                | AIN        | _0P        | Al       | Channel 0 Positive Analog Input.           |

| 17                | AIN        | _0N        | AI       | Channel 0 Negative Analog Input.           |

| 18                | AIN        | _1P        | Al       | Channel 1 Positive Analog Input.           |

| 19                | AIN        | _1N        | Al       | Channel 1 Negative Analog Input.           |

| 20                | AIN        | _2N        | AI       | Channel 2 Negative Analog Input.           |

| 21                | AIN_2P     |            | Al       | Channel 2 Positive Analog Input.           |

| 22                | AIN_3N     |            | AI       | Channel 3 Negative Analog Input.           |

| 23                | AIN        | AIN_3P     |          | Channel 3 Positive Analog Input.           |

| 24                | NC         | AIN_4N     | Al       | Channel 4 Negative Analog Input.           |

| 25                | NC         | AIN_4P     | Al       | Channel 4 Positive Analog Input.           |

| 26                | NC         | AIN_5N     | AI       | Channel 5 Negative Analog Input.           |

| 27                | NC         | AIN_5P     | Al       | Channel 5 Positive Analog Input.           |

| 28, 29,<br>31, 32 | AG         | ND         | Р        | Analog Ground.                             |

| 30                | AV         | DD         | Р        | Analog Power Supply.                       |

| 33                | DG         | ND         | Р        | Digital Ground.                            |

| 34                | DVDD       |            | Р        | Digital Power Supply.                      |

| 35                | DN         | DNC        |          | Do Not Connect This Pin. Keep it floating. |

| 36                | SE         | SDO        |          | Serial Data Output.                        |

| 37                | SC         | ELK        | DI       | Serial Clock Input.                        |

| 38                | nC         | CS         | DI       | Chip-Select Input Pin. Active low.         |

#### NOTE:

1. Al = Analog Input, AO = Analog Output, AIO = Analog Input and Output, DI = Digital Input, DO = Digital Output, DIO = Digital Input and Output, P = Power Supply.

## **ELECTRICAL CHARACTERISTICS**

(AVDD = 5V, DVDD = 3V,  $V_{REF}$  = 4.096V (internal), and  $f_{SAMPLE}$  = 500kSPS, Full = -40°C to +125°C, typical values are at  $T_A$  = +25°C, unless otherwise noted.)

| PARAMETER                                                  | SYMBOL                                                                     | CONDIT                                                     | TONS                     | MIN    | TYP | MAX   | UNITS  |

|------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------|--------------------------|--------|-----|-------|--------|

| Analog Inputs                                              |                                                                            |                                                            |                          |        |     |       |        |

|                                                            |                                                                            | Input range = ±2.5 × V                                     | REF                      | -10.24 |     | 10.24 |        |

|                                                            |                                                                            | Input range = ±1.25 × V <sub>REF</sub>                     |                          | -5.12  |     | 5.12  |        |

|                                                            | AIN_nP-AGND                                                                | Input range = ±0.625 >                                     | V <sub>REF</sub>         | -2.56  |     | 2.56  | V      |

|                                                            |                                                                            | Input range = 0 to 2.5                                     | × V <sub>REF</sub> (2)   | 0      |     | 10.24 |        |

| Abaalista laasit Valtaaa Danaa                             |                                                                            | Input range = 0 to 1.25                                    | 5 × V <sub>REF</sub> (2) | 0      |     | 5.12  |        |

| Absolute Input Voltage Range                               |                                                                            | Input range = ±2.5 × V                                     | REF                      | -10.24 |     | 10.24 |        |

|                                                            |                                                                            | Input range = ±1.25 ×                                      | V <sub>REF</sub>         | -5.12  |     | 5.12  |        |

|                                                            | AIN_nN-AGND                                                                | Input range = ±0.625 >                                     | V <sub>REF</sub>         | -2.56  |     | 2.56  | V      |

|                                                            |                                                                            | Input range = 0 to 2.5                                     | × V <sub>REF</sub> (2)   |        | 0   |       |        |

|                                                            |                                                                            | Input range = 0 to 1.25                                    | 5 × V <sub>REF</sub> (2) |        | 0   |       |        |

|                                                            |                                                                            | Input range = ±2.5 × V <sub>REF</sub>                      |                          | -10.24 |     | 10.24 |        |

|                                                            | AIN_nP-AIN_nN<br>(AIN_nN = AGND)<br>Or<br>AIN_nP-AIN_nN<br>(AIN_nP = AGND) | Input range = ±1.25 × V <sub>REF</sub>                     |                          | -5.12  |     | 5.12  | V      |

| Input Voltage Range <sup>(1)</sup><br>(Single-Ended Input) |                                                                            | Input range = $\pm 0.625 \times V_{REF}$                   |                          | -2.56  |     | 2.56  |        |

| (09.0000put)                                               |                                                                            | Input range = 0 to 2.5 × V <sub>REF</sub> (2)              |                          | 0      |     | 10.24 |        |

|                                                            |                                                                            | Input range = 0 to 1.25 × V <sub>REF</sub> (2)             |                          | 0      |     | 5.12  |        |

|                                                            |                                                                            | Input range = ±2.5 × V <sub>REF</sub>                      |                          | -10.24 |     | 10.24 |        |

|                                                            | AIN_nP-AIN_nN                                                              | Input range = ±1.25 × V <sub>REF</sub>                     |                          | -5.12  |     | 5.12  | V      |

| Input Voltage Range (1)                                    |                                                                            | Input range = ±0.625 × V <sub>REF</sub>                    |                          | -2.56  |     | 2.56  |        |

| (Bipolar Differential Input)                               |                                                                            | Input range = ±2.5 × V <sub>REF</sub> <sup>(3)</sup>       |                          | -5.0   |     | 7.5   |        |

|                                                            | Common Mode<br>Input Range                                                 | Input range = ±1.25 ×                                      | V <sub>REF</sub> (3)     | -2.5   |     | 5.0   | V      |

|                                                            | parriange                                                                  | Input range = ±0.625 × V <sub>REF</sub> <sup>(3)</sup>     |                          | -1.2   |     | 2.5   |        |

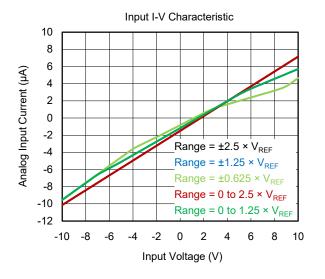

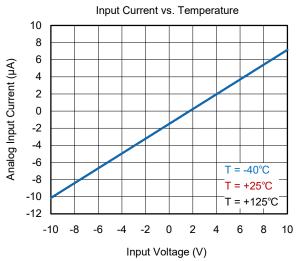

| Input Impedance                                            | R <sub>IN</sub>                                                            | T <sub>A</sub> = +25°C, all input ra                       | inges                    |        | 1   |       | ΜΩ     |

| Input Impedance Drift                                      |                                                                            | All input ranges                                           |                          |        | 15  |       | ppm/°C |

|                                                            |                                                                            |                                                            | V <sub>IN</sub> = 10.24V |        | 7.3 |       |        |

| Input Current                                              | I <sub>IN</sub>                                                            | With voltage at the AIN_nP pin = V <sub>IN</sub>           | V <sub>IN</sub> = 5.12V  |        | 2.8 |       | μA     |

|                                                            |                                                                            | 7                                                          | V <sub>IN</sub> = 2.56V  |        | 0.9 |       |        |

| Input Over-Voltage Protection                              | n                                                                          |                                                            |                          |        |     |       |        |

| Over-Voltage Protection                                    | V                                                                          | AVDD = 5V or offers low impedance < 30kΩ, all input ranges |                          | -20    |     | +20   | V      |

| Voltage                                                    | V <sub>OVP</sub>                                                           | AVDD = floating with impedance > 30kΩ, all input ranges    |                          | -11    |     | +11   | V      |

#### NOTES:

- 1. Ideal input range. It does not consider gain and offset error.

- 2. These two unipolar input ranges are only valid for unipolar single-ended input with AIN\_nN = AGND.

- 3. These input common mode voltage range is guaranteed by design, and tested by limited samples, and not covered by manufacture testing. When the input common mode voltage exceeds ±100mV, the critical DC and AC performance are not guaranteed.

# **ELECTRICAL CHARACTERISTICS (continued)**

(AVDD = 5V, DVDD = 3V,  $V_{REF}$  = 4.096V (internal), and  $f_{SAMPLE}$  = 500kSPS, Full = -40°C to +125°C, typical values are at  $T_A$  = +25°C, unless otherwise noted.)

| PARAMETER                                   | SYMBOL             | CON                                                                | MIN                                            | TYP         | MAX         | UNITS |                     |

|---------------------------------------------|--------------------|--------------------------------------------------------------------|------------------------------------------------|-------------|-------------|-------|---------------------|

| System Performance (If wit                  | hout otherwise not | ed, the following pa                                               | rameters are tested with                       | n single-eı | nded input) |       |                     |

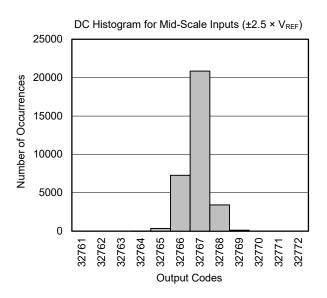

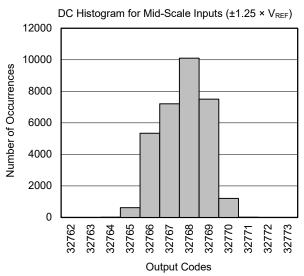

| Resolution                                  |                    |                                                                    |                                                |             | 16          |       | Bits                |

| No Missing Codes                            | NMC                |                                                                    |                                                |             | 16          |       | Bits                |

| Differential Nonlinearity                   | DNL                |                                                                    |                                                | -1          | -0.6/+0.9   | 2.1   | LSB (4)             |

|                                             |                    | All bis along the                                                  | T <sub>A</sub> = +25°C                         | -3          | ±1.3        | 3     |                     |

| Integral Nonlinearity (5)                   | INL                | All bipolar range                                                  | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$ | -5.7        | ±1.3        | 5.1   | LSB                 |

|                                             |                    | All unipolar range                                                 |                                                |             | -3.1/+1.2   |       |                     |

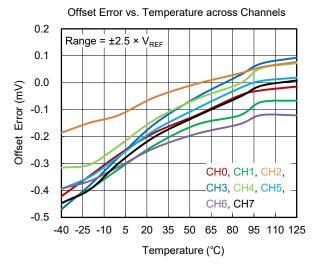

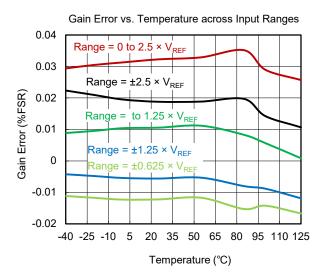

|                                             |                    | $T_A = +25^{\circ}C$ ,<br>input range = ±2.5                       | × V <sub>REF</sub>                             |             | ±0.07       | ±0.14 |                     |

|                                             |                    | $T_A = +25^{\circ}C$ ,<br>input range = ±1.2                       | 5 × V <sub>REF</sub>                           |             | ±0.07       | ±0.34 |                     |

| Gain Error                                  | E <sub>G</sub>     | $T_A = +25$ °C,<br>input range = ±0.6                              | 25 × V <sub>REF</sub>                          |             | ±0.2        | ±0.68 | %FSR <sup>(6)</sup> |

|                                             |                    | $T_A = +25^{\circ}C$ ,<br>input range = 0 to                       | 2.5 × V <sub>REF</sub>                         |             | ±0.07       | ±0.16 |                     |

|                                             |                    | $T_A = +25^{\circ}C$ ,<br>input range = 0 to                       | 1.25 × V <sub>REF</sub>                        |             | ±0.07       | ±0.45 |                     |

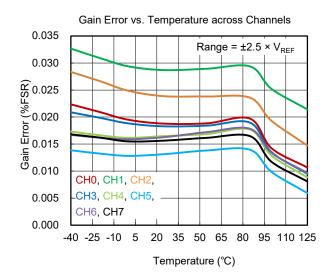

|                                             |                    | $T_A = +25^{\circ}C$ ,<br>input range = $\pm 2.5$                  | × V <sub>REF</sub>                             |             | ±0.05       | ±0.15 |                     |

|                                             |                    | $T_A = +25^{\circ}C$ ,<br>input range = $\pm 1.25 \times V_{REF}$  |                                                |             | ±0.05       | ±0.15 | l                   |

| Gain Error Matching<br>(Channel-to-Channel) |                    | $T_A = +25^{\circ}C$ ,<br>input range = ±0.6                       |                                                | ±0.1        | ±0.3        | %FSR  |                     |

|                                             |                    | $T_A = +25^{\circ}C$ ,<br>input range = 0 to 2.5 × $V_{REF}$       |                                                |             | ±0.05       | ±0.15 | _                   |

|                                             |                    | $T_A = +25^{\circ}C$ ,<br>input range = 0 to 1.25 × $V_{REF}$      |                                                |             | ±0.05       | ±0.15 |                     |

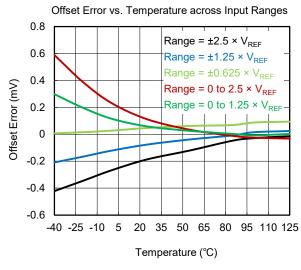

|                                             |                    | $T_A = +25^{\circ}C$ ,<br>input range = $\pm 2.5$                  | × V <sub>REF</sub>                             |             | ±0.3        | ±2.8  |                     |

|                                             |                    | $T_A = +25$ °C,<br>input range = ±1.25 × $V_{REF}$                 |                                                |             | ±0.3        | ±2.9  |                     |

| Offset Error                                | Eo                 | $T_A = +25^{\circ}C$ ,<br>input range = $\pm 0.625 \times V_{REF}$ |                                                |             | ±0.3        | ±3.1  | mV                  |

|                                             |                    | $T_A$ = +25°C,<br>input range = 0 to 2.5 × $V_{REF}$               |                                                |             | ±0.3        | ±2.9  |                     |

|                                             |                    | $T_A = +25^{\circ}C$ ,<br>input range = 0 to                       | 1.25 × V <sub>REF</sub>                        |             | ±0.3        | ±2.6  |                     |

|                                             |                    | $T_A = +25$ °C,<br>input range = ±2.5                              | × V <sub>REF</sub>                             |             | ±0.5        | ±2.5  |                     |

| Offset Error Matching (Channel-to-Channel)  |                    | $T_A = +25^{\circ}C$ ,<br>input range = ±1.25 × $V_{REF}$          |                                                |             | ±0.5 ±2     | ±2.5  |                     |

|                                             |                    | $T_A = +25$ °C,<br>input range = ±0.6                              | 25 × V <sub>REF</sub>                          |             | ±0.5        | ±2.5  | mV                  |

|                                             |                    | $T_A = +25^{\circ}C$ ,<br>input range = 0 to                       |                                                | ±0.5        | ±2.5        |       |                     |

|                                             |                    | $T_A = +25^{\circ}C$ ,<br>input range = 0 to                       | 1.25 × V <sub>REF</sub>                        |             | ±0.5        | ±2.5  |                     |

### NOTES:

- 4. LSB = Least significant bit.

- 5. This is best-fit INL.

- 6. FSR = Full-scale range.

# **ELECTRICAL CHARACTERISTICS (continued)**

(AVDD = 5V, DVDD = 3V,  $V_{REF}$  = 4.096V (internal), and  $f_{SAMPLE}$  = 500kSPS, Full = -40°C to +125°C, typical values are at  $T_A$  = +25°C, unless otherwise noted.)

| PARAMETER                                                          |           | SYMBOL                                         | CONDITIONS                                                         | MIN                             | TYP        | MAX                             | UNITS |

|--------------------------------------------------------------------|-----------|------------------------------------------------|--------------------------------------------------------------------|---------------------------------|------------|---------------------------------|-------|

| Sampling Dynamics (If with                                         | out other | wise noted,                                    | the following parameters are tested with                           | single-end                      | ed input.) |                                 |       |

| Conversion Time                                                    |           | t <sub>CONV</sub>                              |                                                                    |                                 |            | 1000                            | ns    |

| Acquisition Time                                                   |           | t <sub>ACQ</sub>                               |                                                                    | 1000                            |            |                                 | ns    |

| Maximum Throughput Rate w Latency                                  | ithout    | f <sub>S</sub>                                 |                                                                    |                                 |            | 500                             | kSPS  |

| Dynamic Characteristics (If                                        | without   | otherwise no                                   | ted, the following parameters are tested                           | with single                     | -ended inp | ut.)                            |       |

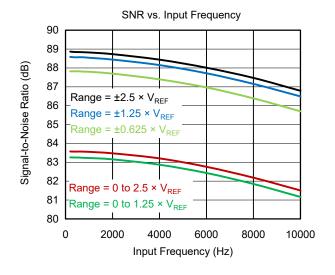

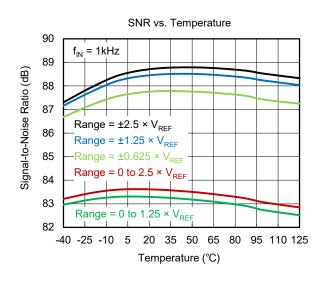

|                                                                    |           |                                                | Input range = ±2.5 × V <sub>REF</sub>                              | 84.6                            | 89.5       |                                 |       |

| o:                                                                 |           |                                                | Input range = ±1.25 × V <sub>REF</sub>                             | 84.4                            | 89.3       |                                 |       |

| Signal-to-Noise Ratio (V <sub>IN</sub> - 0.5dBFS at 1kHz)          |           | SNR                                            | Input range = ±0.625 × V <sub>REF</sub>                            | 83.7                            | 88.4       |                                 | dB    |

| ,                                                                  |           |                                                | Input range = 0 to $2.5 \times V_{REF}$                            | 80.2                            | 84.4       |                                 |       |

|                                                                    |           |                                                | Input range = 0 to 1.25 × V <sub>REF</sub>                         | 79.7                            | 84.1       |                                 |       |

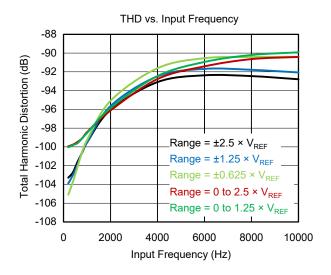

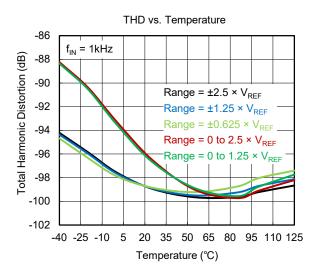

| Total Harmonic Distortion (V <sub>IN</sub> - 0.5dBFS at 1kHz)      |           | THD                                            | All input ranges                                                   |                                 | -99        |                                 | dB    |

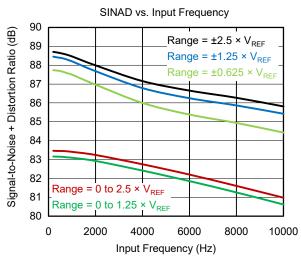

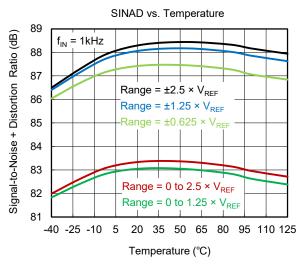

| ,                                                                  |           |                                                | Input range = ±2.5 × V <sub>REF</sub>                              | 84.0                            | 89.1       |                                 |       |

|                                                                    |           |                                                | Input range = ±1.25 × V <sub>REF</sub>                             | 83.6                            | 88.9       |                                 |       |

| Signal-to-Noise Ratio (V <sub>IN</sub> - 0.5dBFS at 1kHz)          |           | SINAD                                          | Input range = ±0.625 × V <sub>REF</sub>                            | 83.2                            | 88         |                                 | dB    |

| (VIN - 0.5dbi O at IKI12)                                          |           |                                                | Input range = 0 to 2.5 × V <sub>REF</sub>                          | 79.4                            | 84.2       |                                 |       |

|                                                                    |           |                                                | Input range = 0 to 1.25 × V <sub>REF</sub>                         | 79.1                            | 83.9       |                                 |       |

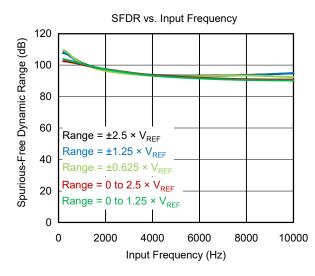

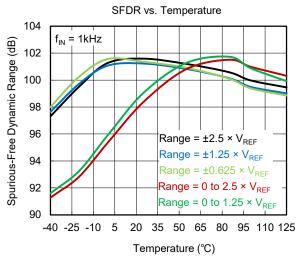

| Spurious-Free Dynamic Range<br>(V <sub>IN</sub> - 0.5dBFS at 1kHz) |           | SFDR                                           | All input ranges                                                   |                                 | 101        |                                 | dB    |

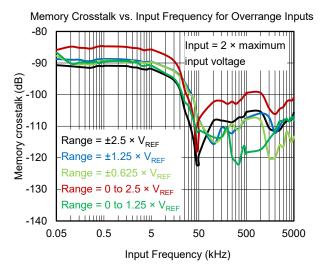

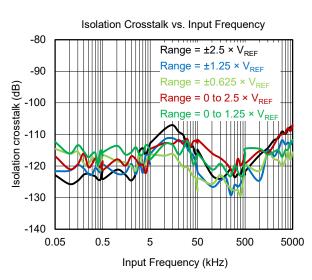

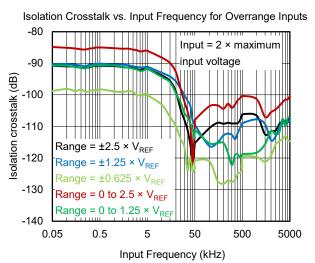

| Crosstalk Isolation (8)                                            |           |                                                | Aggressor channel input is overdriven to 2 × maximum input voltage |                                 | 120        |                                 | dB    |

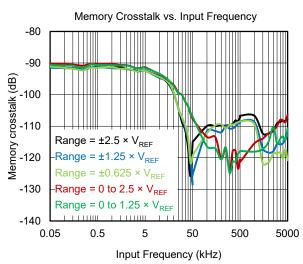

| Crosstalk Memory (9)                                               |           |                                                | Aggressor channel input is overdriven to 2 × maximum input voltage |                                 | 94         |                                 | dB    |

| Small-Signal Bandwidth                                             | -3dB      | BW <sub>-3dB</sub>                             | T <sub>A</sub> = +25°C, all input ranges                           |                                 | 13         |                                 | kHz   |

| oman-oighai bandwidin                                              | -0.1dB    | BW <sub>-0.1dB</sub>                           | T <sub>A</sub> = +25°C, all input ranges                           |                                 | 2.1        |                                 | KI IZ |

| Auxiliary Channel                                                  |           |                                                |                                                                    |                                 |            |                                 |       |

| Resolution                                                         |           |                                                |                                                                    | 16                              |            |                                 | Bits  |

| Input Voltage Range                                                |           | V <sub>AUX_INP</sub> -<br>V <sub>AUX_INN</sub> | AUX_INP - AUX_INN                                                  | -V <sub>REF</sub>               |            | +V <sub>REF</sub>               | V     |

| Operating Input Range                                              |           |                                                | AUX_INP                                                            | 2.5 -<br>0.5 × V <sub>REF</sub> |            | 2.5 +<br>0.5 × V <sub>REF</sub> | V     |

|                                                                    |           |                                                | AUX_INN                                                            | 2.5 -<br>0.5 × V <sub>REF</sub> |            | 2.5 +<br>0.5 × V <sub>REF</sub> |       |

|                                                                    |           | _                                              | During sampling                                                    |                                 | 75         |                                 | _     |

| Input Capacitance                                                  |           | Cı                                             | During conversion                                                  |                                 | 5          |                                 | pF    |

| Input Leakage Current                                              |           | I <sub>IKG(IN)</sub>                           |                                                                    |                                 | 100        |                                 | nA    |

| Differential Nonlinearity                                          |           | DNL                                            |                                                                    |                                 | -0.6/+0.9  |                                 | LSB   |

| Integral Nonlinearity                                              |           | INL                                            |                                                                    |                                 | ±1.3       |                                 | LSB   |

| Gain Error                                                         |           | E <sub>G(AUX)</sub>                            | T <sub>A</sub> = +25°C                                             |                                 | ±0.08      | ±0.2                            | % FSR |

| Offset Error                                                       |           | E <sub>O(AUX)</sub>                            | T <sub>A</sub> = +25°C                                             |                                 | ±0.3       | ±2                              | mV    |

| Signal-to-Noise Ratio                                              |           | SNR                                            | V <sub>AUX_INP</sub> - V <sub>AUX_INN</sub> = -0.5dBFS at 1kHz     | 83.2                            | 88.1       |                                 | dB    |

| Total Harmonic Distortion (7)                                      |           | THD                                            | V <sub>AUX_INP</sub> - V <sub>AUX_INN</sub> = -0.5dBFS at 1kHz     |                                 | -99.1      |                                 | dB    |

| Signal-to-Noise + Distortion                                       |           | SINAD                                          | V <sub>AUX_INP</sub> - V <sub>AUX_INN</sub> = -0.5dBFS at 1kHz     | 83.0                            | 87.8       |                                 | dB    |

| Spurious-Free Dynamic Rang                                         | je        | SFDR                                           | V <sub>AUX INP</sub> - V <sub>AUX INN</sub> = -0.5dBFS at 1kHz     |                                 | 100.7      |                                 | dB    |

# **ELECTRICAL CHARACTERISTICS (continued)**

(AVDD = 5V, DVDD = 3V,  $V_{REF}$  = 4.096V (internal), and  $f_{SAMPLE}$  = 500kSPS, Full = -40°C to +125°C, typical values are at  $T_A$  = +25°C, unless otherwise noted.)

|                                | therwise noted.)   | 0)///                   | . CONDITIONS                                        |                                               | B. G. P. Y.   | <b>D</b> /D | 54.537                              |            |  |      |      |   |

|--------------------------------|--------------------|-------------------------|-----------------------------------------------------|-----------------------------------------------|---------------|-------------|-------------------------------------|------------|--|------|------|---|

|                                | METER              | SYMBOL                  | CONDITION                                           | NS .                                          | MIN           | TYP         | MAX                                 | UNITS      |  |      |      |   |

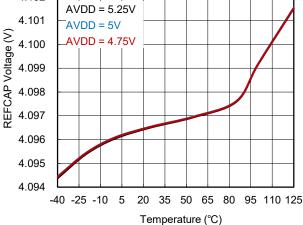

| Internal Referen               | nce Output         |                         | 1                                                   |                                               |               |             | ı                                   | 1          |  |      |      |   |

| Decoupling Capa                | acitor on REFIO    | $C_{\text{OUT\_REFIO}}$ |                                                     |                                               |               | 100         |                                     | nF         |  |      |      |   |

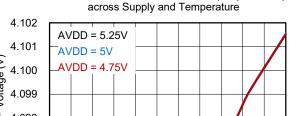

| Initial Reference              | •                  | $V_{REFCAP}$            | T <sub>A</sub> = +25°C                              |                                               | 4.093         | 4.096       | 4.099                               | V          |  |      |      |   |

| Reference Buffe<br>Impedance   | r Output           |                         |                                                     |                                               |               | 0.5         |                                     | Ω          |  |      |      |   |

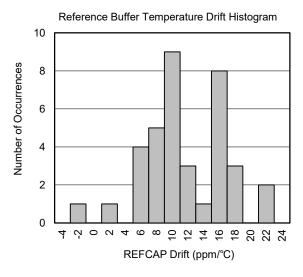

| Reference Buffe<br>Drift       | r Temperature      |                         |                                                     |                                               |               | 9           |                                     | ppm/°C     |  |      |      |   |

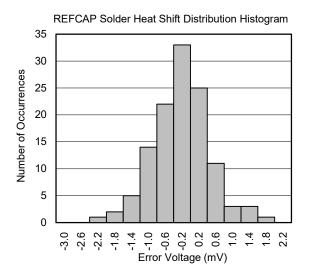

| Decoupling Capa                | acitor on REFCAP   | C <sub>OUT_REFCAP</sub> |                                                     |                                               |               | 22          |                                     | μF         |  |      |      |   |

| Turn-On Time                   |                    |                         | C <sub>OUT_REFCAP</sub> = 22µF, C <sub>OUT_RE</sub> | <sub>FIO</sub> = 100nF                        |               | 25          |                                     | ms         |  |      |      |   |

| External Refere                | nce Input          |                         |                                                     |                                               |               |             |                                     |            |  |      |      |   |

| External Referer<br>REFIO (10) | nce Voltage on     | V <sub>REFIO_EXT</sub>  | REFIO pin configured as ar                          | n input                                       | 4.046         | 4.096       | 4.146                               | V          |  |      |      |   |

| Power-Supply F                 | Requirements       |                         |                                                     |                                               |               |             |                                     |            |  |      |      |   |

| Analog Power-S                 | upply Voltage      | AVDD                    | Analog supply                                       |                                               | 4.75          | 5           | 5.25                                | V          |  |      |      |   |

| Digital Davis Co               | unuli ( ) /alka ma | DVDD                    | Digital supply range                                |                                               | 1.65          | 3.3         | AVDD                                |            |  |      |      |   |

| Digital Power-Su               | ippiy voitage      | DVDD                    | Digital supply range for specified performance      |                                               | 2.7           | 3.3         | AVDD                                | V          |  |      |      |   |

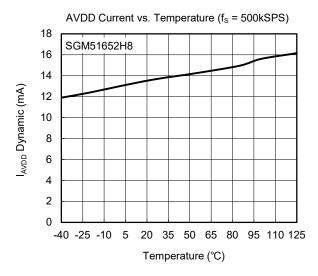

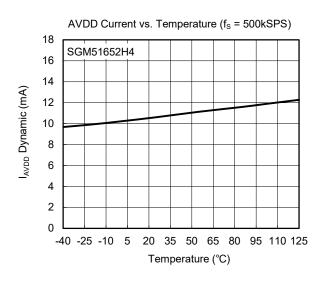

|                                |                    |                         | Domestic AVDD                                       | Dynamia AV/DD                                 | Dynamic AV/DD | _           | AVDD = 5V, f <sub>S</sub> = maximum | SGM51652H8 |  | 14.5 | 19.5 | A |

|                                | Dynamic, AVDD      | $I_{AVDD\_DYN}$         | and internal reference                              | SGM51652H4                                    |               | 11          | 15.5                                | mA         |  |      |      |   |

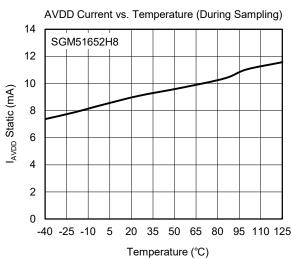

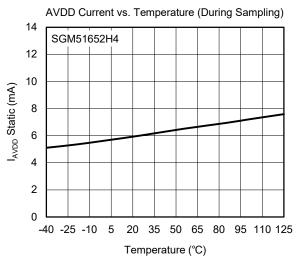

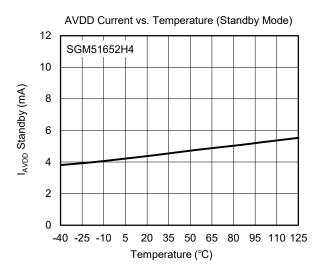

|                                | Static             | Statio                  |                                                     | AVDD = 5V, device not converting and internal | SGM51652H8    |             | 10                                  | 15         |  |      |      |   |

| Analog Supply<br>Current       |                    | I <sub>AVDD_STC</sub>   | reference                                           | SGM51652H4                                    |               | 5           | 10.5                                | - mA       |  |      |      |   |

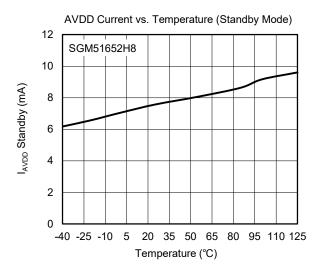

| Carrone                        | Ot an allow        |                         | AVDD = 5V, device in                                | SGM51652H8                                    |               | 8.5         | 12.5                                | 4          |  |      |      |   |

|                                | Standby            | I <sub>STDBY</sub>      | STDBY mode and internal reference                   | SGM51652H4                                    |               | 4.5         | 8.5                                 | - mA       |  |      |      |   |

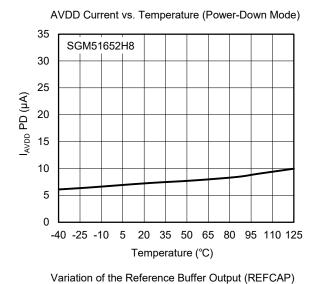

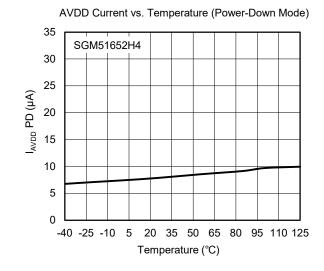

|                                | Power-Down         | I <sub>PWR_DOWN</sub>   | AVDD = 5V, device in PWR                            | DOWN mode                                     |               | 4           | 20                                  | μA         |  |      |      |   |

| Digital Supply Co              | urrent             | I <sub>DVDD_DYN</sub>   | DVDD = 3.3V, output = 000                           | 0h                                            |               | 0.5         |                                     | mA         |  |      |      |   |

| Digital Inputs                 |                    |                         |                                                     |                                               |               |             |                                     |            |  |      |      |   |

|                                |                    | V <sub>IH</sub>         | - DVDD > 2.1V                                       |                                               | 0.7 ×<br>DVDD |             | DVDD                                |            |  |      |      |   |

| Digital Input Log              | ic Levels          | V <sub>IL</sub>         |                                                     |                                               | 0             |             | 0.3 ×<br>DVDD                       | - V        |  |      |      |   |

|                                |                    | V <sub>IH</sub>         |                                                     |                                               | 0.8 ×<br>DVDD |             | DVDD                                |            |  |      |      |   |

| Digital Input Log              | ic Levels          | V <sub>IL</sub>         | DVDD ≤ 2.1V                                         |                                               | 0             |             | 0.15 ×<br>DVDD                      | V          |  |      |      |   |

| Input Leakage C                | urrent             |                         |                                                     |                                               |               | 100         |                                     | nA         |  |      |      |   |

| Input Pin Capaci               | tance              |                         |                                                     |                                               |               | 5           |                                     | pF         |  |      |      |   |

| Digital Outputs                |                    |                         | •                                                   |                                               |               |             | •                                   | •          |  |      |      |   |

| Digital Output Lo              | ogic Lovols        | V <sub>OH</sub>         | I <sub>O</sub> = 100μA source                       |                                               | 0.8 ×<br>DVDD |             | DVDD                                | V          |  |      |      |   |

| Digital Output LC              | gio Leveis         | V <sub>OL</sub>         | I <sub>O</sub> = 100μA sink                         |                                               | 0             |             | 0.2 ×<br>DVDD                       |            |  |      |      |   |

| Floating State Le              | eakage Current     |                         | Only for SDO                                        |                                               |               | 1           |                                     | μΑ         |  |      |      |   |

| Internal Pin Cap               | acitance           | _                       |                                                     |                                               |               | 5           |                                     | pF         |  |      |      |   |

#### NOTES:

- 7. Accumulated the first nine harmonics.

- 8. A full-scale sinusoidal 10kHz signal is applied to a channel which is not selected in conversion sequence, and measures its effect on any selected channel.

- 9. A full-scale sinusoidal 10kHz signal is applied to a channel which is selected in conversion sequence, and measures its effect on the next selected conversion channel.

- 10. Limits set by characterization at room temperature only.

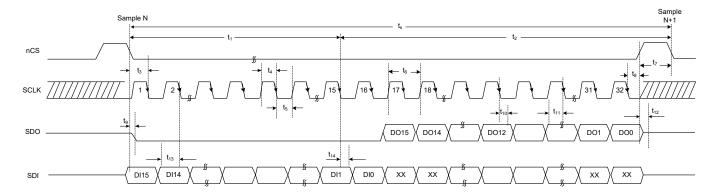

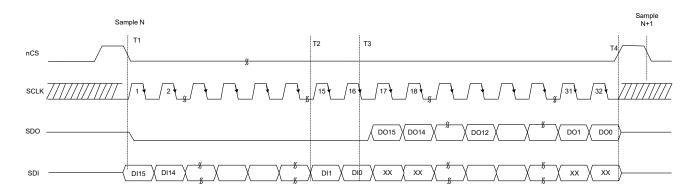

## **TIMING REQUIREMENTS: SERIAL INTERFACE**

(AVDD = 5V, DVDD = 3V,  $V_{REF}$  = 4.096V (internal), SDO Load = 20pF, and  $f_{SAMPLE}$  = 500kSPS, Full = -40°C to +125°C, typical values are at  $T_A$  = +25°C, unless otherwise noted.)

| PARAMETER                                               | SYMBOL            | CONDITIONS | MIN                 | TYP | MAX  | UNITS             |

|---------------------------------------------------------|-------------------|------------|---------------------|-----|------|-------------------|

| Timing Specifications                                   |                   |            | •                   |     |      |                   |

| Sampling Frequency (f <sub>CLK</sub> = max)             | fs                |            |                     |     | 500  | kSPS              |

| ADC Cycle Time Period (f <sub>CLK</sub> = max)          | ts                |            | 2                   |     |      | μs                |

| Serial Clock Frequency (f <sub>S</sub> = max)           | f <sub>SCLK</sub> |            |                     |     | 17   | MHz               |

| Serial Clock Time Period (f <sub>S</sub> = max)         | t <sub>SCLK</sub> |            | 1/f <sub>SCLK</sub> |     |      | ns                |

| Conversion Time                                         | t <sub>1</sub>    |            |                     |     | 1000 | ns                |

| Delay Time: nCS Falling to Data Enable                  | t <sub>9</sub>    |            |                     |     | 13   | ns                |

| Delay Time: Last SCLK Falling to nCS Rising             | t <sub>8</sub>    |            | 10                  |     |      | ns                |

| Delay Time: nCS Rising to SDO Going to 3-State          | t <sub>12</sub>   |            | 15                  |     |      | ns                |

| Timing Requirements                                     |                   |            |                     |     |      |                   |

| Acquisition Time                                        | t <sub>2</sub>    |            | 1000                |     |      | ns                |

| Clock High Time                                         | t <sub>4</sub>    |            | 0.4                 |     | 0.6  | t <sub>SCLK</sub> |

| Clock Low Time                                          | t <sub>5</sub>    |            | 0.4                 |     | 0.6  | t <sub>SCLK</sub> |

| nCS High Time                                           | t <sub>7</sub>    |            | 30                  |     |      | ns                |

| Setup Time: nCS Falling to SCLK Falling                 | t <sub>3</sub>    |            | 30                  |     |      | ns                |

| Hold Time: SCLK Falling to (Previous) Data Valid on SDO | t <sub>10</sub>   |            | 5                   |     |      | ns                |

| Setup Time: SDO Data Valid to SCLK Falling              | t <sub>11</sub>   |            | 5                   |     |      | ns                |

| Setup Time: SDI Data Valid to SCLK Falling              | t <sub>13</sub>   |            | 5                   |     |      | ns                |

| Hold Time: SCLK Falling to (Previous) Data Valid on SDI | t <sub>14</sub>   |            | 5                   |     |      | ns                |

Figure 1. Serial Interface Timing Diagram

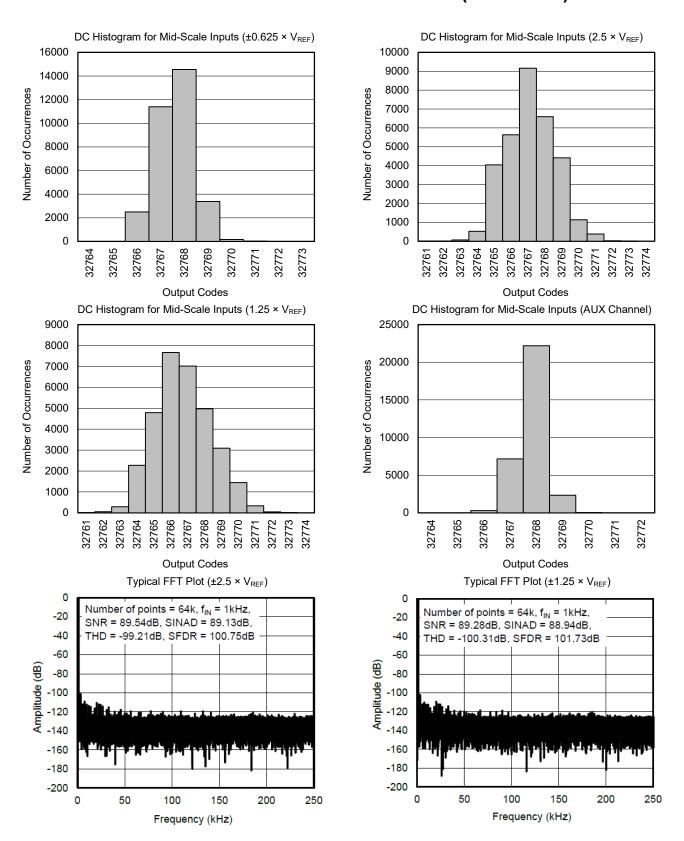

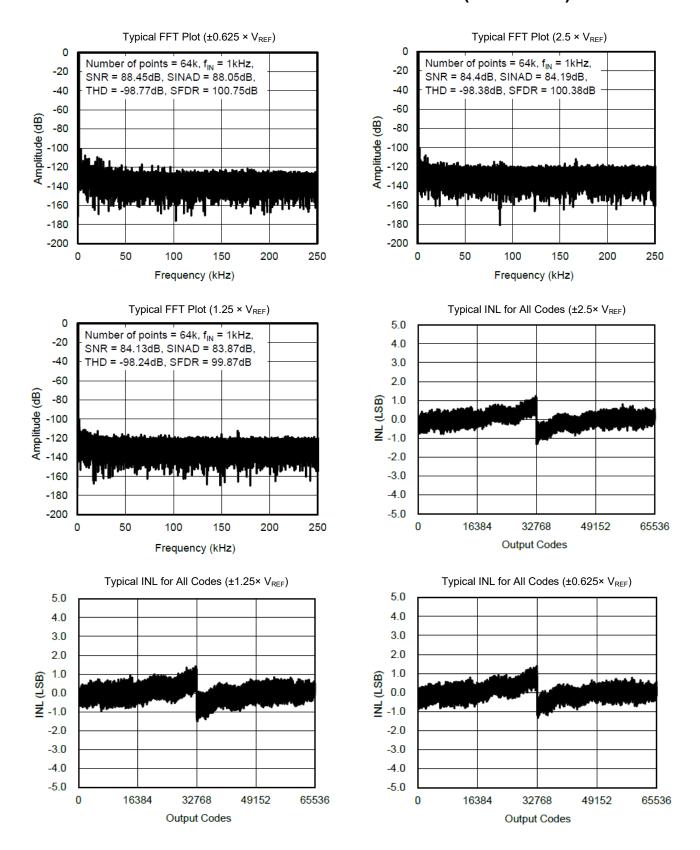

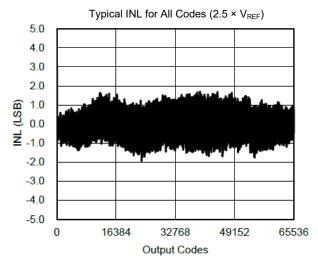

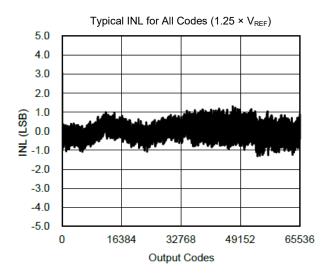

## TYPICAL PERFORMANCE CHARACTERISTICS

## **FUNCTIONAL BLOCK DIAGRAM**

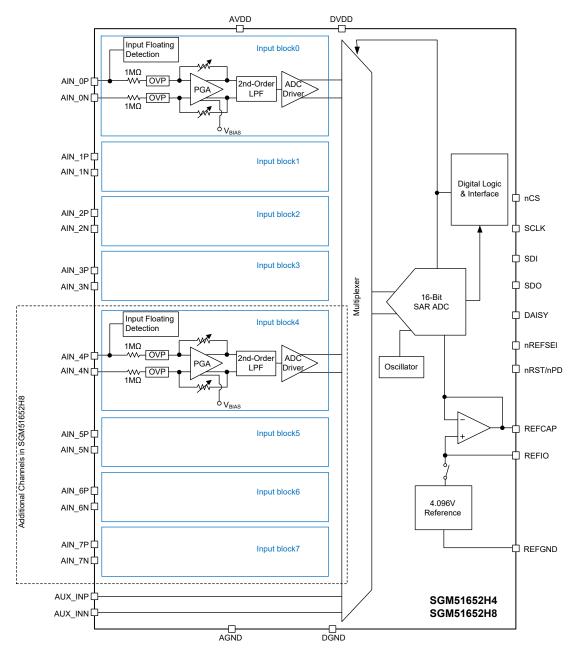

Figure 2. Block Diagram

## **DETAILED DESCRIPTION**

#### Overview

The SGM51652H4 has 4 channels inputs. The SGM51652H8 has 8 channels inputs. They both have a 16-bit 500kSPS SAR ADC core. The interface is SPI-compatible serial interface and supports with daisy-chain (DAISY) features.

## **Analog Inputs**

The chip supports bipolar single-ended input, bipolar differential input, and unipolar single-ended input.

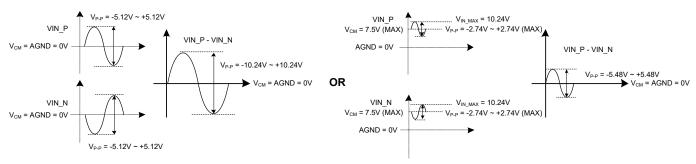

When it works in bipolar single-ended input, tie the AIN\_nN to AGND (system ground), the signal applied to AIN\_nP can be bipolar  $\pm 2.5 \times V_{REF}, \pm 1.25 \times V_{REF},$  and  $\pm 0.625 \times V_{REF}.$  Another selection is that tie the AIN\_nP to AGNG (system ground), the signal applied to AIN\_nN can be bipolar  $\pm 2.5 \times V_{REF}, \pm 1.25 \times V_{REF},$  and  $\pm 0.625 \times V_{REF}.$

When it works in unipolar single-ended input, tie the AIN\_nN to AGND (system ground), the signal applied to AIN\_nP can be unipolar 0 to  $2.5 \times V_{REF}$ , and 0 to  $1.25 \times V_{REF}$ .

When it works in bipolar differential input, then AIN\_nN and AIN\_nP are differential inputs referring to AGND. For each pin, the absolute voltage referring to AGND must be within the limited voltage specified in electrical characteristic table, at the same time, the differential voltage of AIN\_nP-AIN\_nN must be compatible with the according input ranges. The common mode voltage of AIN\_nP and AIN\_nN are limited in according input ranges. Please refer to electrical characteristic table. When the chip works in bipolar differential input, the valid input ranges are bipolar  $\pm 2.5 \times V_{REF}, \pm 1.25 \times V_{REF}, \text{ and } \pm 0.625 \times V_{REF}.$  The illustrative input signals are shown in Figure 3, as shown in this example, if input common mode voltage is not 0V, there will be some dynamic range (ADC conversion code) losing accordingly.

The input voltage range is configured by software, and it can be bipolar  $\pm 2.5 \times V_{REF}$ ,  $\pm 1.25 \times V_{REF}$ , and  $\pm 0.625 \times V_{REF}$  or unipolar 0 to  $2.5 \times V_{REF}$ , and 0 to  $1.25 \times V_{REF}$ . If there is a reference voltage of 4.096V (internal or external), then the input ranges of the device can be configured to bipolar ranges of  $\pm 10.24$ V,  $\pm 5.12$ V, and  $\pm 2.56$ V, or unipolar ranges of 0V to 10.24V and 0V to 5.12V.

### **Analog Input Impedance**

The input impedance of each channel is  $\geq 1M\Omega$ .

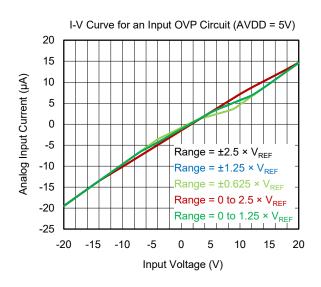

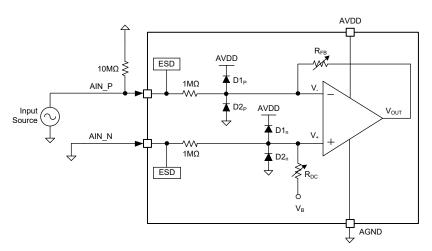

## Input Over-Voltage Protection Circuit

The chip has input over-voltage protection (OVP) circuit. Table 1 shows these characteristics.

Table 1. Input Over-Voltage Protection Limits when AVDD = 5V  $^{(1)}$

| Input Condition<br>(V <sub>OVP</sub> = ±20V)                  | ADC<br>Output | Comments                                                              |

|---------------------------------------------------------------|---------------|-----------------------------------------------------------------------|

| V <sub>IN</sub>   <  V <sub>RANGE</sub>                       | Valid         | Work normally.                                                        |

| V <sub>RANGE</sub>   <  V <sub>IN</sub>   <  V <sub>OVP</sub> | Saturated     | ADC output is saturated, and the internal protection circuits are on. |

| $ V_{IN}  >  V_{OVP} $                                        | Saturated     | This may damage the chip.                                             |

NOTE: 1. AGND = 0V,  $|V_{RANGE}|$  is the maximum input voltage for any selected input range, and  $|V_{OVP}|$  is the break-down voltage for the internal OVP circuit. Assume that  $R_S$  is approximately  $0\Omega$ .

In the following condition, the input signal is applied before analog AVDD is powered on or the input signal is applied and keep analog AVDD is floating, the input OVP circuits will be on. And if the input voltage exceeds the  $|V_{OVP}|$ , the chip will be damaged.

NOTE: V<sub>CM</sub> means common mode voltage. V<sub>P-P</sub> means peak-to-peak voltage.

Figure 3. Examples of Bipolar Differential ±10.24V Input

### **Input Floating Detection Function**

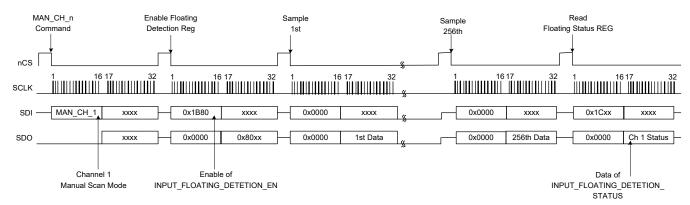

The device features an input floating detection function, when this function is enabled by setting INPUT FLOATING DETECTION EN register corresponding bit (see Table 16). Besides setting the INPUT FLOATING DETECTION EN register, it also needs a pull-down resistor  $10M\Omega$  connected to system ground (AGND), please refer to typical connection in Figure 4. After setting INPUT FLOATING DETECTION EN register (see Table 16), the host needs to send the manual mode command to continuously convert the channel that needs floating detection. When the detected input is floating, the corresponding bit in the INPUT\_FLOATING\_ DETECTION STATUS register is set to 1 (see Table 17). After the floating detection is completed, the bit in the INPUT\_FLOATING\_DETECTION\_EN register is automatically set to 0 (see Table 16). If the detected input is given an input signal source later, please repeat the above floating detection steps. Then the INPUT FLOATING DETECTION STATUS register referred bit can be cleared.

Note that, to perform a complete input floating detection, there must be a consecutive 256 times conversions, which cannot be interrupted by normal input sampling. At same time, if there is still an input signal at input pin, the input floating detection will report an untrusted result.

### **Programmable Gain Amplifier (PGA)**

The chip has a programmable gain amplifier (PGA), and the PGA gain can be adjusted by setting the RANGE\_CHn[3:0] (n = 0 to 3 or 0 to 7) bits in the configuration register (see the Channel n Input Range Registers).

**Table 2. Input Range Selection Bits Details**

| Analog Input Range                          | RANGE_CHn[3:0] |       |       |       |  |  |  |  |

|---------------------------------------------|----------------|-------|-------|-------|--|--|--|--|

| Alialog iliput Kalige                       | Bit 3          | Bit 2 | Bit 1 | Bit 0 |  |  |  |  |

| ±2.5 × V <sub>REF</sub> (default)           | 0              | 0     | 0     | 0     |  |  |  |  |

| ±1.25 × V <sub>REF</sub>                    | 0              | 0     | 0     | 1     |  |  |  |  |

| ±0.625 × V <sub>REF</sub>                   | 0              | 0     | 1     | 0     |  |  |  |  |

| 0 to 2.5 × V <sub>REF</sub> <sup>(1)</sup>  | 0              | 1     | 0     | 1     |  |  |  |  |

| 0 to 1.25 × V <sub>REF</sub> <sup>(1)</sup> | 0              | 1     | 1     | 0     |  |  |  |  |

NOTE: 1. These two unipolar input ranges are only valid for unipolar single-ended input with AIN nN = AGND.

#### Multiplexer (MUX)

The maximum throughout data rate of scanning all channels is 500kSPS. For the SGM51652H4, it means the maximum data rate per channel is 125kSPS if all 4 channels are enabled. For the SGM51652H8, it means the maximum data rate per channel is 62.5kSPS if all 8 channels are enabled.

Please refer to Table 6 for details of auto-scan mode and manual mode settings.

#### Reference

The chip can be operated with an internal reference or an external voltage reference.

**Figure 4. Input Floating Detection Connection**

### **Auxiliary Channel**

The chip has a true differential input channel (AUX\_INP and AUX\_INN). This AUX channel goes to ADC only through the MUX. There is no PGA, driver or low pass filter in the AUX channel.

The absolute input on AUX\_INP and AUX\_INN must be 0 to  $V_{REF}$ . The differential input range of  $V_{AUX\_INP}$  -  $V_{AUX\_IND}$  is - $V_{REF}$  to + $V_{REF}$ .

### **ADC Description**

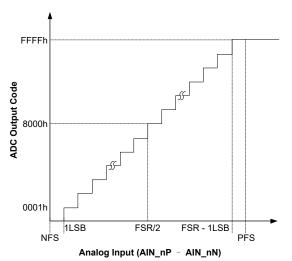

The chip output code is in straight-binary format.

Figure 5. Device Transfer Function (Straight-Binary Format)

Table 3. ADC LSB Values for Different Input Ranges ( $V_{REF} = 4.096V$ )

| Input Range                                 | Positive<br>Full-Scale<br>(V) | Negative<br>Full-Scale<br>(V) | Full-Scale<br>Range (V) | LSB<br>(µV) |

|---------------------------------------------|-------------------------------|-------------------------------|-------------------------|-------------|

| ±2.5 × V <sub>REF</sub>                     | 10.24                         | -10.24                        | 20.48                   | 312.5       |

| ±1.25 × V <sub>REF</sub>                    | 5.12                          | -5.12                         | 10.24                   | 156.25      |

| ±0.625 × V <sub>REF</sub>                   | 2.56                          | -2.56                         | 5.12                    | 78.125      |

| 0 to 2.5 × V <sub>REF</sub> <sup>(1)</sup>  | 10.24                         | 0                             | 10.24                   | 156.25      |

| 0 to 1.25 × V <sub>REF</sub> <sup>(1)</sup> | 5.12                          | 0                             | 5.12                    | 78.125      |

NOTE: 1. These two unipolar input ranges are only valid for unipolar single-ended input with AIN nN = AGND.

#### **Device Functional Modes**

nRST/nPD (Input)

nRST/nPD is a dual-function pin. The timing of this pin is shown in Figure 6, and Table 4 explains the usage of this pin.

Figure 6. nRST/nPD Pin Timing

#### Table 4. nRST/nPD Pin Functionality

| Condition                              | Device Mode                                                                                                              |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| 40ns < t <sub>PL_RST_PD</sub> ≤ 100ns  | The device goes into RESET mode.                                                                                         |

| 100ns < t <sub>PL_RST_PD</sub> < 400ns | The device is in RESET mode and has the possibility to go into PWR_DOWN mode. Note that this setting is not recommended. |

| t <sub>PL_RST_PD</sub> ≥ 400ns         | The device goes into PWR_DOWN mode and the program registers are reset to default value.                                 |

The chip can be powered down by pulling nRST/nPD pin for at least 400ns. And this operation is asynchronous to chip's operation clock and working status. In power-down mode, the chip has no response to any digital inputs except operating on nRST/nPD pin.

When chip goes into RESET mode and PWR\_DOWN mode, the program registers are reset to default value.

When the nRST/nPD pin is pulled high again, the chip wakes up and goes into a default state. To let the chip work correctly, it must re-configure the program registers accordingly.

#### **Data Acquisition Example**

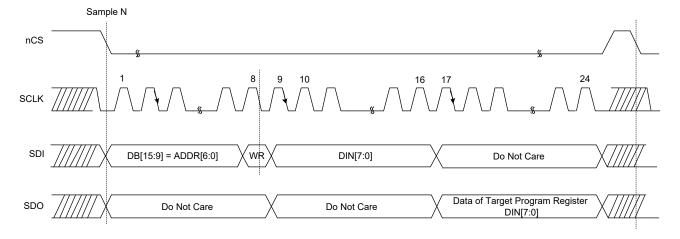

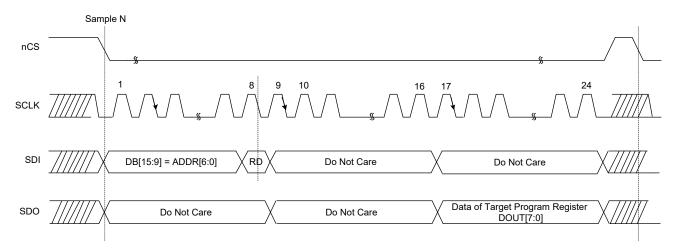

This section briefly introduces how the chip works and interfaces with the host controller. Figure 7 shows the timing marks.

As shown in Figure 7, there are four events T1 ~ T4.

T1: The input signal is sampled at the moment of the nCS falling edge. The ADC conversion is driven by internal oscillator clock. The current ADC result is from the input channel selected by previous data frame. The current SDI data setting is for the next conversion. The SDO goes low because of there is no ADC conversion result during the first 16 SCLK cycles.

T2: The conversion time is 16 SCLK cycles. Therefore, the maximum SCLK frequency must be compliance with the timing requirement (which is listed in Electrical Characteristics table). Otherwise, if the conversion time is not enough, the ADC conversion result is corrupt. The MSB of ADC result

starts to be shifted out on SDO at the 16<sup>th</sup> falling edge of SCLK.

T3: After the 16<sup>th</sup> falling edge of the SCLK, the chip doesn't read any more data on SDI. The host controller can read the ADC result at every falling edge of the SCLK cycle which is from 17<sup>th</sup> to 32<sup>nd</sup>. If there are more SCLK cycles, the SDO is filled with 0 until next conversion is initiated.

T4: The host controller stops the data frame by pulling nCS high. The SDO goes into 3-state until the next data frame starts.

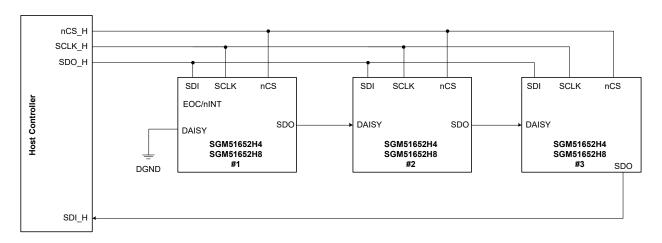

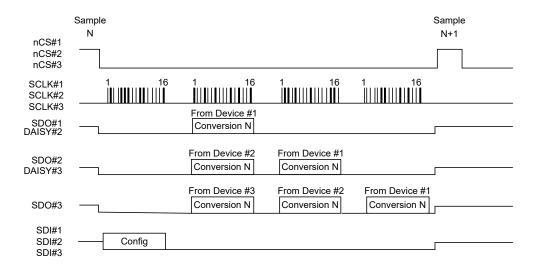

### **Daisy-Chain Topology**

A typical connection diagram showing multiple devices in daisy-chain mode is shown in Figure 8. The devices can enter daisy-chain mode without any special hardware or software configuration.

Figure 7. Timing Diagram of Device Operation Using the Serial Interface

Figure 8. Daisy-Chain Connection Schematic

A typical timing diagram for three devices connected in daisy-chain mode is shown in Figure 9.

As shown in the example, the three chips are connected in daisy-chain mode in Figure 9. Each chip samples its respective signal input on the falling edge of the nCS. At the first 16 SCLK cycles, SDO outputs keep low. At the second 16 SCLK cycles, each chip outputs its ADC result to SDO, and receives the data from DAISY pin. On every subsequence SCLK cycle, the DAISY pin data is shifted in and stored in internal register, and the chip shifts out the internal shift register data to its SDO pin. In this example,  $16 \times 3 = 48$  SCLK cycles are required to shift all data to the tail chip SDO pin. In total 64 SCLK cycles for all 3 chips to conversion and shift out all data.

#### **Device Modes**

After power-up, the SGM51652H4 and SGM51652H8 stay in IDLE state and don't perform any function until a command from the host controller.

#### Continued Operation in the Selected Mode (NO OP)

If the chip receives a NO\_OP command (0x0000), it will follow the same settings which are already in the program registers. The previous selected mode can be STDBY, PWR\_DOWN, AUTO SCAN and MAN CH n.

If the NO\_OP command (0x0000) occurs during any other configure operation to the command register, the chip retains the old settings of the program registers. Then the chip goes back to IDLE state and waits for a new command.

#### Frame Abort Condition (FRAME\_ABORT)

As shown in Data Acquisition Example section, a complete command is at least composed of 16 SCLK cycles, and the command is locked in at the falling of the 16<sup>th</sup> SCLK. If the SCLK is not accumulated to 16, the chip keeps waiting and the nCS must stay low all operation process. If the nCS goes high before the command transmission is completed, the chip goes to an invalid state. It will not skip out the invalid condition until a new proper command is performed.

Figure 9. Timing Diagram of Three Devices Connected in Daisy-Chain Mode

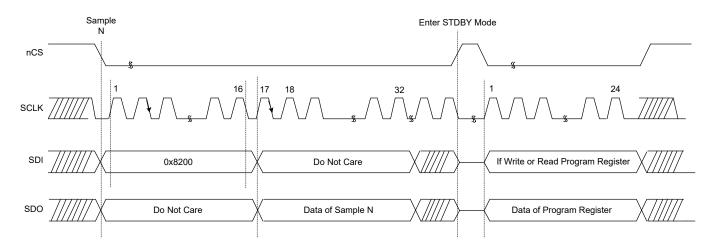

#### STANDBY Mode (STDBY)

The chip supports a low power consumption standby mode (STDBY). In STDBY mode, only parts of the circuits are powered off, and they will take the chip about 20µs to exit the STDBY mode. After getting out of the STDBY, the chip program registers retain its customer's setting value.

As shown in Figure 10, issuing a STDBY command 0x8200, the command will be valid and the chip goes into STDBY mode on the rising edge of nCS. To exit STDBY mode, a valid command AUTO\_SCAN or MAN\_CH\_n must be issued and it will be valid on the rising edge of nCS (see Figure 11). In the STDBY mode, the program registers can be read or written.

But the chip doesn't do conversion, thus any conversion data read back is invalid (more details in Program Register Read/Write Operation section).

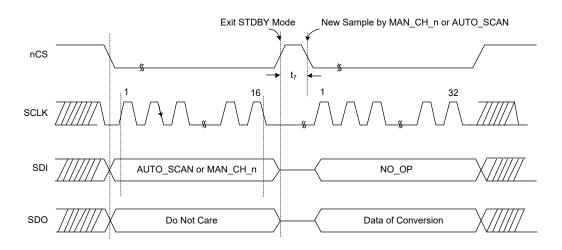

Figure 11 shows the command AUTO\_SCAN or MAN\_CH\_n can call the chip out of the STDBY mode. It is valid at the rising edge of the nCS. It will take the chip about 30µs to fully be ready to sample and do conversion after exiting STDBY mode. It is necessary to hold nCS high at least 30µs before a new data frame starting. On the next nCS falling edge, the chip samples the input channel which is selected by MAN\_CH\_n or the first channel of the AUTO\_SCAN mode sequence (more details refer to Figure 7).

Figure 10. Timing Diagram for Entering and Remaining in STDBY Mode

Figure 11. Timing Diagram for Exiting STDBY Mode

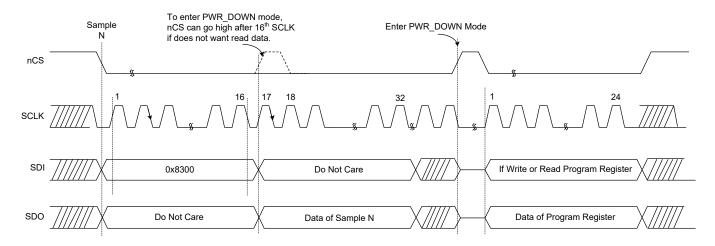

#### Power-Down Mode (PWR DOWN)

The chip supports both software and hardware power-down mode (PWR\_DOWN). The hardware power-down mode is talked in the nRST/nPD section. When the chip is waked up from software power-down, all previous settings of program registers are retained. When the chip is waked up from hardware power-down mode, all the registers are reset to default values. It will take the chip about 15ms to fully power up and ready to work after receiving wake up command (AUTO SCAN or MAN CH n).

As shown in Figure 12, issuing a PWR\_DOWN command 0x8300, the command will be valid and the chip goes into PWR\_DOWN mode on the rising edge of nCS. To exit PWR\_DOWN mode, a valid command AUTO\_SCAN or MAN\_CH\_n must be issued and it will be valid on the rising

edge of nCS (See Figure 13). Being in the PWR\_DOWN mode, the program registers can be read or written. But the chip doesn't do conversion, thus any conversion data read back is invalid (more details in Program Register Read/Write Operation section).

Figure 13 shows the command AUTO\_SCAN or MAN\_CH\_n can call the chip out of the PWR\_DOWN mode. It is valid at the rising edge of the nCS. It will take the chip about 15ms to fully be ready to sample and do conversion after exiting PWR\_DOWN mode. It is necessary to hold nCS high at least 15ms before a new data frame starting. On the next nCS falling edge, the chip samples the input channel which is selected by MAN\_CH\_n or the first channel of the AUTO\_SCAN mode sequence (more details refer to Figure 8).

Figure 12. Timing Diagram for Entering and Remaining in PWR\_DOWN Mode

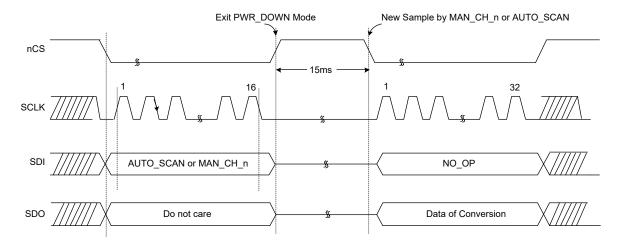

Figure 13. Timing Diagram for Exiting PWR\_DOWN Mode

# **DETAILED DESCRIPTION (continued)**

#### Auto Channel Enable with Reset (AUTO\_SCAN)

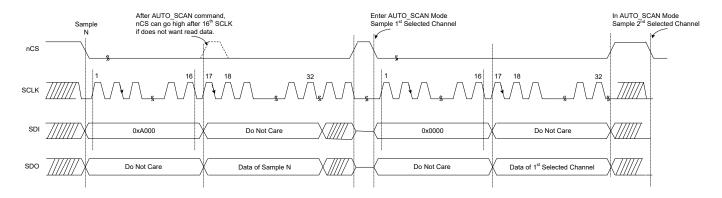

In Figure 14, if a chip is set to work in AUTO\_SCAN (0xA000) mode, it can scan all selected channels automatically. In order to read every selected channel conversion result correctly, each of the data frame must be at least 32 SCLK cycles.

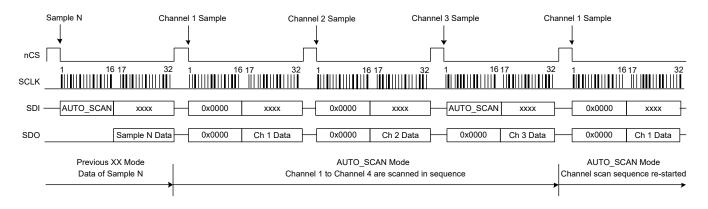

The selected channels which the chip goes through in AUTO\_SCAN mode is configured by the program register 0x01 and register 0x02 (please see the Program Register Map section). In this mode, the chip goes through all selected

channels in ascending order from the lowest channel. When it scans all channels, it will repeat the cycle from the lowest channel. The input range of each channel can be configured separately in the Range Select Registers.

An example is shown in Figure 15, during the AUTO\_SCAN operation sequence, if an AUTO\_SCAN command is inserted, the chip re-starts scanning from the lowest selected channel. Figure 14 shows a scan sequence from channel 1 to channel 4 and an AUTO\_SCAN command is inserted after channel 3 conversion.

Figure 14. Timing Diagram for Entering AUTO\_SCAN Mode

Figure 15. Example of Device Operation in AUTO\_SCAN Mode

# **DETAILED DESCRIPTION (continued)**

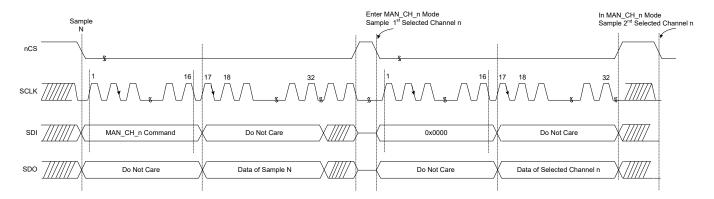

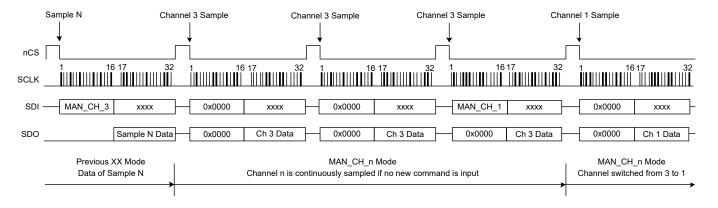

#### Manual Channel n Select (MAN\_CH\_n)

As shown in Figure 16, the chip can work in manual channel mode (MAN\_CH\_n) and do conversion in a specified channel by manual mode command. In order to read every selected channel conversion result correctly, each of the data frame must be at least 32 SCLK cycles. Refer to Table 5 for a list of commands of MAN CH n mode.

An example is shown in Figure 17, if there is no other new valid command, the chip will keep sampling the current channel selected by MAN\_CH\_n. The input range of each channel can be configured separately in the Range Select Registers. Figure 17 shows an example MAN\_CH\_3 to MAN CH 1 in manual select mode.

Figure 16. Timing Diagram for Entering MAN\_CH\_n Scan Mode

Figure 17. Example of Device Operation in MAN\_CH\_n Mode

# **DETAILED DESCRIPTION (continued)**

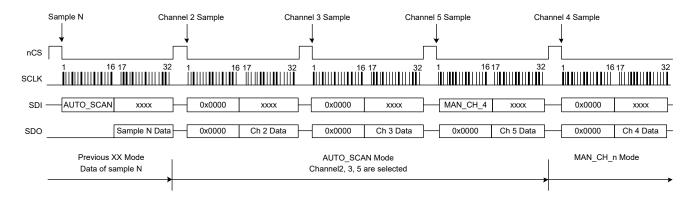

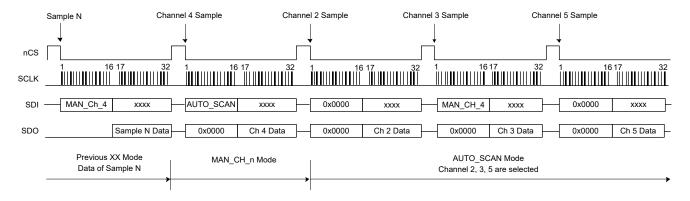

#### **Channel Sequencing Modes**

The chip supports two kinds of channel sequence modes, auto channel scanning (AUTO\_SCAN) and manual channel selection (MAN CH n).

In AUTO\_SCAN mode, the chip goes through all selected channels in ascending order from the lowest channel.

In MAN\_CH\_n mode, the chip samples the same input channel if there is no new command input. If a new input channel is selected by MAN CH n command, then the new

selected channel is sampled in the next data frame. Figure 18 shows an example channel sequence switching from AUTO\_SCAN (channel 2, 3, 5 are selected) to MAN\_CH\_n (MAN\_CH\_4).

Figure 19 shows an example channel sequence switching from MAN\_CH\_n (MAN\_CH\_5) to AUTO\_SCAN (channel 2, 3, 5 are selected). A new command is executed in the next operation frame.

Figure 18. Transitioning from AUTO\_SCAN to MAN\_CH\_n Mode

Figure 19. Transitioning from MAN\_CH\_n to AUTO\_SCAN Mode

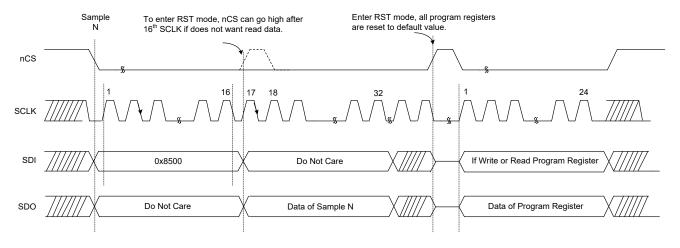

#### Reset Program Registers (RST)

The chip supports both hardware and software reset (RST command 0x8500). In both cases, all program registers are reset to default values. The hardware reset is explained in nRST/nPD section.

As shown in Figure 20, a valid RST command can be issued during any data frame. After receiving the RST command, the chip reset all program registers on the rising edge of nCS. In the RESET mode, the program registers can be read or written. But the chip doesn't do conversion, thus any conversion data read back is invalid (more details in Program Register Read/Write Operation section).

An AUTO\_SCAN command or a MAN\_CH\_n command can call the chip out of RESET mode. To initiate a conversion on a particular analog channel, a valid AUTO\_SCAN or MAN\_CH\_n command must be executed using the default program register settings.

# Input Floating Detection Function Operating Sequences

The device provides a function to detect input floating. To perform this function, it is necessary to follow the operations as bellow.

Step1: Change to manual mode, and selected target channel n by MAN CH n command.

Step2: Write 0x80 to INPUT FLOATING\_DETECTION\_EN Register (address is 0x0D, see Table 16).

Step3: Perform consecutive 256 times of conversions. Note that, to perform a complete input floating detection, there must be a consecutive 256 times conversions, it can't be interrupted by normal input sampling. At same time, if there is still an input signal at input pin, the input floating detection will report an untrusted result.

Step4: Read INPUT FLOATING\_DETECTION\_STATUS Register (address is 0x0E, see Table 17). Note that the alarm bit in INPUT\_FLOATING\_DETECTION\_STATUS register will not be cleared, until an input floating detection operation is performed again and the inputs of ADC are connected with an input signal source.

For an example operation sequences of channel 1, please refer to Figure 23.

Figure 20. Timing Diagram of Reset Program Registers (RST)

Figure 21. Input Floating Detection Operating Sequences

## **REGISTER MAPS**

The SGM51652H4 and SGM51652H8 have two kinds of internal registers, command registers and program registers.

The command registers are listed in Table 5. They are used for working modes setting, including AUTO\_SCAN, MAN CH n, STDBY, PWR DOWN and RST.

The program registers are listed in Table 8. They are used for working conditions setting, including channels scanning

sequence, SDO output format, and input range settings of each individual channels.

### **Command Register Description**

The command register is a 16-bit, write-only register which is used for setting SGM51652H4/SGM51652H8 working modes.

**Table 5. Command Register Maps**

| Deviates                                        | MSB Byte |     |     |     |     |     |    |    | LSB Byte  | Command | Operation in Next Frame             |  |