# SGM2049 2A, High Accuracy, Low Noise, Low Dropout Linear Regulator

#### **GENERAL DESCRIPTION**

The SGM2049 is a high accuracy, low noise, very low dropout linear regulator. It is capable of supplying 2A output current with typical dropout voltage of only 75mV. The operating input voltage range is from 1.1V to 7V with BIAS and 1.4V to 7V without BIAS. The output voltage of the SGM2049 can be set from 0.8V to 3.95V in pin-selectable operation and adjusted from 0.8V to 5.2V by using an external resistor divider.

Other features include logic-controlled shutdown mode, short-circuit current limit and thermal shutdown protection. The SGM2049 has automatic discharge function to quickly discharge V<sub>OUT</sub> in the disabled status.

The SGM2049 is suitable for application which needs high accuracy, low noise and high current power supply, such as analog-to-digital converters (ADCs), digital-to-analog converters (DACs) and RF components.

With very high accuracy, remote sensing, and soft-start capabilities to reduce inrush current, the SGM2049 ensures the optimal system performance for powering digital loads such as FPGAs, DSPs and ASICs.

The SGM2049 is available in Green TQFN-3.5×3.5-20L and TQFN-5×5-20L packages. It operates over an operating temperature range of -40°C to +125°C.

#### **APPLICATIONS**

Wireless Equipment

Industrial, Instrumentation and Medical

ADC and DAC

ATE

#### **FEATURES**

- Operating Input Voltage Range:

- With BIAS: 1.1V to 7V

- Without BIAS: 1.4V to 7V

- Output Voltage Range:

- Adjustable Operation: 0.8V to 5.2V

- Pin-Selectable Operation: 0.8V to 3.95V

- Output Voltage Accuracy: ±1% at +25°C

- Low Dropout Voltage: 75mV (TYP) at 2A

- Low Noise: 5μV<sub>RMS</sub> (TYP) with BIAS

- Excellent Load and Line Transient Responses

- With Output Automatic Discharge

- Adjustable Soft-Start Inrush Control

- Support Power-Good Indicator Function

- -40°C to +125°C Operating Temperature Range

- Available in Green TQFN-3.5×3.5-20L and TQFN-5×5-20L Packages

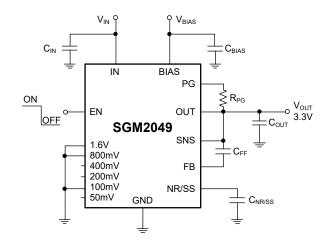

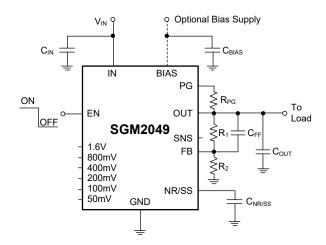

#### TYPICAL APPLICATION

Figure 1. Typical Application Circuit

#### PACKAGE/ORDERING INFORMATION

| MODEL   | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING         | PACKING<br>OPTION   |

|---------|------------------------|-----------------------------------|--------------------|----------------------------|---------------------|

| SGM2049 | TQFN-3.5×3.5-20L       | -40°C to +125°C                   | SGM2049XTRL20G/TR  | SGM2049<br>XTRL20<br>XXXXX | Tape and Reel, 4000 |

| 3GW2049 | TQFN-5×5-20L           | -40°C to +125°C                   | SGM2049XTRM20G/TR  | SGM2049<br>XTRM20<br>XXXXX | Tape and Reel, 3000 |

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

| IN, BIAS, PG, EN to GND0.3V to 8V                      |

|--------------------------------------------------------|

| SNS, OUT to GND0.3V to Min(V <sub>IN</sub> + 0.3V, 8V) |

| NR/SS, FB to GND0.3V to 3.6V                           |

| 50mV, 100mV, 200mV, 400mV, 800mV, 1.6V to GND          |

| 0.3V to (V <sub>OUT</sub> + 0.3V)                      |

| PG Current (Sink Current into Device)5mA               |

| Package Thermal Resistance                             |

| TQFN-3.5×3.5-20L, θ <sub>JA</sub>                      |

| TQFN-3.5×3.5-20L, θ <sub>JB</sub>                      |

| TQFN-3.5×3.5-20L, $\theta_{JC}$                        |

| TQFN-5×5-20L, $\theta_{JA}$                            |

| TQFN-5×5-20L, θ <sub>JB</sub>                          |

| TQFN-5×5-20L, θ <sub>JC</sub>                          |

| Junction Temperature+150°C                             |

| Storage Temperature Range65°C to +150°C                |

| Lead Temperature (Soldering, 10s)+260°C                |

| ESD Susceptibility                                     |

| HBM6000V                                               |

| CDM1000V                                               |

#### RECOMMENDED OPERATING CONDITIONS

| Input Supply Voltage Range                   | 1.1V to 7V            |

|----------------------------------------------|-----------------------|

| Bias Supply Voltage Range (1)                | 3V to 7V              |

| Output Voltage Range                         | 0.8V to 5.2V          |

| Enable Voltage Range                         | 0V to V <sub>IN</sub> |

| Output Current                               | 0A to 2A              |

| Input Effective Capacitance, C <sub>IN</sub> | 5µF (MIN)             |

| Output Effective Capacitance, Cout           | 10µF to 1000µF        |

| Bias Effective Capacitance, CBIAS            | 5µF (MIN)             |

| Power-Good Pull-Up Resistance                | 10kΩ to 100kΩ         |

| Operating Junction Temperature Range         | 40°C to +125°C        |

|                                              |                       |

#### NOTE

1. Bias supply voltage is required when  $V_{IN}$  < 1.4V and not required when  $V_{IN} \ge 1.4V$ .

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

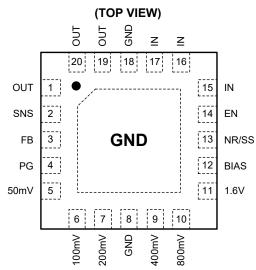

#### **PIN CONFIGURATIONS**

TQFN-3.5×3.5-20L/TQFN-5×5-20L

#### **PIN DESCRIPTION**

| PIN            | NAME  | FUNCTION                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1, 19, 20      | OUT   | Regulator Output Pin. It is recommended to use an output capacitor with effective capacitance in the range of $10\mu\text{F}$ to $1000\mu\text{F}$ to ensure stability. This ceramic capacitor should be placed as close as possible to OUT pin. |  |  |  |  |  |  |

| 2              | SNS   | Output Voltage Sense Input Pin. The SNS pin is connected to the load side of the output trace only when the pin-selectable programming mode is used. Keep SNS pin floating if the $V_{\text{OUT}}$ voltage is set by external resistor.          |  |  |  |  |  |  |

| 3              | FB    | Feedback Voltage Input Pin. Connect this pin to the midpoint of an external resistor divider to adjust the output voltage. Place the resistors as close as possible to this pin.                                                                 |  |  |  |  |  |  |

| 4              | PG    | Power-Good Indicator Output Pin. An open-drain, active-high output that indicates the status of $V_{OUT}$ . When the output voltage reaches $V_{IT(PG)}$ of the target, the PG pin goes into a high-impedance state.                             |  |  |  |  |  |  |

| 5              | 50mV  |                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| 6              | 100mV |                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| 7              | 200mV | Output Voltage Setting Pins. Select the desired output voltage by connecting these pins to the ground. Connecting these pins to the ground increases the output voltage value corresponding to the pin                                           |  |  |  |  |  |  |

| 9              | 400mV | name. Multiple pins can be connected to GND at the same time. When V <sub>OUT</sub> is set by an external resistor, leave these pins floating (open).                                                                                            |  |  |  |  |  |  |

| 10             | 800mV | resister, reave trees pine reading (epon).                                                                                                                                                                                                       |  |  |  |  |  |  |

| 11             | 1.6V  |                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| 12             | BIAS  | Bias Supply Voltage Pin for Internal Control Circuits. This pin is monitored by internal under-voltage lockout circuit and enables the use of low-input voltage, low-output voltage conditions ( $V_{IN}$ < 1.4V).                               |  |  |  |  |  |  |

| 13             | NR/SS | Noise-Reduction and Soft-Start Pin. Using an external capacitor $C_{NR/SS}$ to decouple this pin to GND can not only reduce output noise to very low level but also slow down the $V_{OUT}$ rise like a soft-start behavior.                     |  |  |  |  |  |  |

| 14             | EN    | Enable Pin. Drive EN high to turn on the regulator. Drive EN low to turn off the regulator. This pin must be connected to IN or BIAS pin if enable functionality is not used.                                                                    |  |  |  |  |  |  |

| 15, 16, 17     | IN    | Input Supply Voltage Pin. It is recommended to use a 10µF or larger ceramic capacitor from IN pin to ground to get good power supply decoupling. This ceramic capacitor should be placed as close as possible to IN pin.                         |  |  |  |  |  |  |

| 8, 18          | GND   | Ground.                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Exposed<br>Pad | GND   | Exposed Pad. Connect it to GND internally. Connect it to a large ground plane to maximize thermal performance; this pad is not an electrical connection point.                                                                                   |  |  |  |  |  |  |

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN}=(V_{OUT(NOM)}+0.4V) \text{ or } 1.4V \text{ (whichever is greater)}, V_{BIAS}=Open, V_{OUT(NOM)}=0.8V, V_{EN}=1.1V, C_{IN}=10\mu\text{F}, C_{OUT}=22\mu\text{F}, C_{NR/SS}=0n\text{F}, C_{FF}=0n\text{F} \text{ and PG pin pulled up to } V_{IN} \text{ with } 100\text{k}\Omega, T_{J}=-40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ typical values are at } T_{J}=+25^{\circ}\text{C}, \text{ unless otherwise noted.)}$

| PARAMETER                          | SYMBOL                          | CONDITIONS                                                                         |                                                              | MIN   | TYP  | MAX   | UNITS |

|------------------------------------|---------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------|-------|------|-------|-------|

| Input Supply Voltage Range         | V <sub>IN</sub>                 |                                                                                    |                                                              | 1.1   |      | 7     | V     |

| Bias Supply Voltage Range          | V <sub>BIAS</sub>               | V <sub>IN</sub> = 1.1V                                                             |                                                              | 3     |      | 7     | V     |

| Out at Vallage Day                 | V                               | Pin-selectable operation                                                           |                                                              | 0.8   |      | 3.95  | .,    |

| Output Voltage Range               | V <sub>out</sub>                | Adjustable operation, using external resistors                                     |                                                              | 0.8   |      | 5.2   | V     |

| For all and Malkers                | .,                              | T <sub>J</sub> = +25°C                                                             |                                                              | 0.792 | 0.8  | 0.808 | .,    |

| Feedback Voltage                   | $V_{FB}$                        |                                                                                    |                                                              | 0.784 |      | 0.816 | V     |

| NR/SS Pin Voltage                  | V <sub>NR/SS</sub>              |                                                                                    |                                                              |       | 0.8  |       | V     |

| Input Supply UVLO with Bias        | V <sub>UVLO1(IN)</sub>          | V <sub>IN</sub> rising with V <sub>BIAS</sub> = 3V                                 |                                                              |       | 0.78 | 0.95  | V     |

| V <sub>UVLO1(IN)</sub> Hysteresis  | V <sub>HYS1(IN)</sub>           | V <sub>BIAS</sub> = 3V                                                             |                                                              |       | 100  |       | mV    |

| Input Supply UVLO without Bias     | V <sub>UVLO2(IN)</sub>          | V <sub>IN</sub> rising                                                             |                                                              |       | 1.14 | 1.4   | V     |

| V <sub>UVLO2(IN)</sub> Hysteresis  | V <sub>HYS2(IN)</sub>           |                                                                                    |                                                              |       | 40   |       | mV    |

| Bias Supply UVLO                   | V <sub>UVLO(BIAS)</sub>         | V <sub>BIAS</sub> rising, V <sub>IN</sub> = 1.1V                                   |                                                              |       | 2.5  | 2.8   | V     |

| V <sub>UVLO(BIAS)</sub> Hysteresis | V <sub>HYS(BIAS)</sub>          | V <sub>IN</sub> = 1.1V                                                             |                                                              |       | 260  |       | mV    |

|                                    |                                 | $V_{IN} = 1.4V$ to 7V without BIAS,                                                | T <sub>J</sub> = +25°C                                       | -1    |      | 1     |       |

| Output Voltage Accuracy            | V <sub>OUT</sub>                | or $V_{IN} = 1.1V$ , $V_{BIAS} = 3V$ to $7V$ , $T_{JOUT} = 5mA$ to $2A$            | $T_J = -40^{\circ}C \text{ to } +125^{\circ}C$               | -1.7  |      | 1.3   | - %   |

|                                    |                                 | i ili-scicciable operation,                                                        | T <sub>J</sub> = +25°C                                       | -1.4  |      | 1.4   |       |

|                                    |                                 |                                                                                    | $T_J = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}$ | -2    |      | 2     |       |

| Line Regulation                    | $\Delta V_{OUT}/\Delta V_{IN}$  | $V_{IN}$ = 1.4V to 7V, $I_{OUT}$ = 5mA                                             |                                                              |       | 0.04 | 1.5   | mV/V  |

|                                    |                                 | V <sub>BIAS</sub> = 3V to 7V, V <sub>IN</sub> = 1.1V, I <sub>OUT</sub> = 5mA to 2A |                                                              |       | 0.1  | 1.8   |       |

| Load Regulation                    | $\Delta V_{OUT}/\Delta I_{OUT}$ | I <sub>OUT</sub> = 5mA to 2A                                                       |                                                              |       | 0.1  | 2.2   | mV/A  |

|                                    |                                 | $I_{OUT}$ = 5mA to 2A, $V_{OUT}$ = 5.2V                                            |                                                              |       | 0.7  | 4.5   |       |

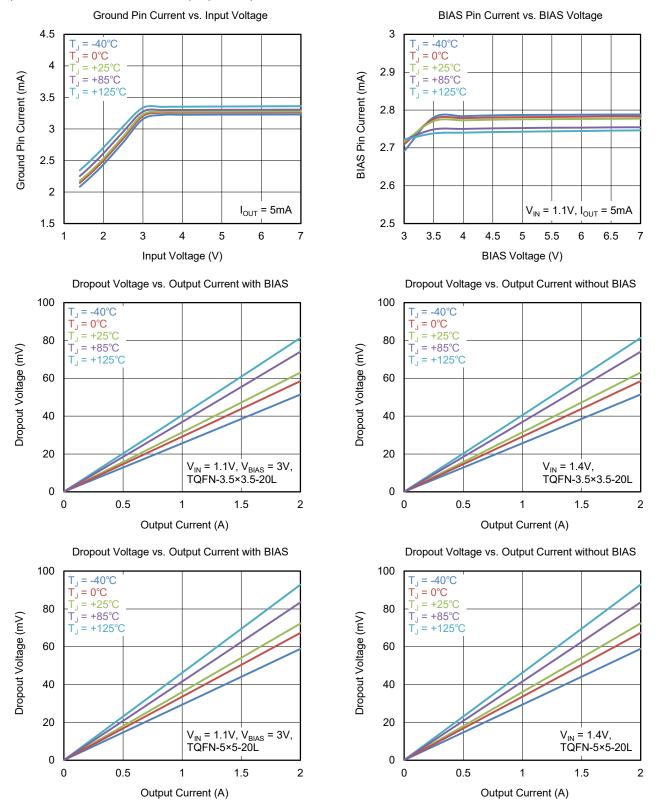

|                                    |                                 | V <sub>IN</sub> = 1.4V, I <sub>OUT</sub> = 2A, V <sub>FB</sub> = 0.776V            |                                                              |       | 75   | 120   | mV    |

| Dropout Voltage                    | $V_{DROP}$                      | $V_{IN} = 5.2V$ , $I_{OUT} = 2A$ , $V_{FB} = 0.7$                                  |                                                              | 75    | 120  |       |       |

|                                    |                                 | V <sub>IN</sub> = 1.1V, V <sub>BIAS</sub> = 5V, I <sub>OUT</sub> = 2A              | A, V <sub>FB</sub> = 0.776V                                  |       | 75   | 120   |       |

| Output Current Limit               | I <sub>LIMIT</sub>              | $V_{OUT}$ forced at 90% × $V_{OUT(NOM)}$ ,<br>$V_{IN} = V_{OUT(NOM)} + 0.4V$       |                                                              | 2.2   | 3.2  | 4     | Α     |

| Short-Circuit Current Limit        | I <sub>sc</sub>                 | $R_{LOAD} = 20m\Omega$ , under foldback                                            | operation                                                    |       | 1.7  |       | Α     |

| OND Die Owwent                     |                                 | V <sub>IN</sub> = 7V, I <sub>OUT</sub> = 5mA                                       |                                                              |       | 3.3  | 4.1   | mA    |

| GND Pin Current                    | I <sub>GND</sub>                | V <sub>IN</sub> = 1.4V, I <sub>OUT</sub> = 2A                                      |                                                              |       | 2.3  | 3     | mA    |

| Chuthaum Cumant                    |                                 | PG = Open, V <sub>IN</sub> = 7V, V <sub>EN</sub> = 0.5V, T <sub>J</sub> = +25°C    |                                                              |       | 1.4  | 3     |       |

| Shutdown Current                   | I <sub>SHDN</sub>               | PG = Open, V <sub>IN</sub> = 7V, V <sub>EN</sub> = 0.5V                            |                                                              |       |      | 15    | μA    |

| BIAS Pin Current                   | I <sub>BIAS</sub>               | $V_{IN} = 1.1V$ , $V_{BIAS} = 7V$ , $V_{OUT(NOM)} = 0.8V$ , $I_{OUT} = 2A$         |                                                              |       | 2.9  | 3.6   | mA    |

| EN Pin Low-Level Input Voltage     | $V_{IL(EN)}$                    | EN input voltage "L"                                                               |                                                              | 0     |      | 0.5   | V     |

| EN Pin High-Level Input Voltage    | V <sub>IH(EN)</sub>             | EN input voltage "H"                                                               |                                                              | 1.1   |      | 7     | V     |

| EN Pin Current                     | I <sub>EN</sub>                 | V <sub>IN</sub> = 7V, V <sub>EN</sub> = 0V and 7V                                  |                                                              | -0.3  |      | 0.3   | μΑ    |

| Turn-On Time                       | t <sub>ON</sub>                 | From assertion of $V_{EN}$ to $V_{OUT} = 90\% \times V_{OUT(NOM)}$                 |                                                              |       | 300  |       | μs    |

| Output Discharge Resistance        | R <sub>DIS</sub>                | V <sub>IN</sub> = 1.4V, V <sub>EN</sub> = 0V, V <sub>OUT</sub> = 0.5V              |                                                              |       | 260  | 330   | Ω     |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = (V_{OUT(NOM)} + 0.4V) \text{ or } 1.4V \text{ (whichever is greater)}, V_{BIAS} = Open, V_{OUT(NOM)} = 0.8V, V_{EN} = 1.1V, C_{IN} = 10 \mu F, C_{OUT} = 22 \mu F, C_{NR/SS} = 0nF, C_{FF} = 0nF \text{ and PG pin pulled up to } V_{IN} \text{ with } 100 k\Omega, T_J = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}, \text{ typical values are at } T_J = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.)}$

| PARAMETER                       | SYMBOL                       | CONDITIONS                                                                                    |                                                          | MIN                        | TYP                       | MAX | UNITS             |

|---------------------------------|------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------|---------------------------|-----|-------------------|

| PG Pin Threshold                | V <sub>IT(PG)</sub>          | For falling V <sub>OUT</sub>                                                                  | 84% ×<br>V <sub>OUT</sub>                                | 89% ×<br>V <sub>OUT</sub>  | 93% ×<br>V <sub>OUT</sub> | ٧   |                   |

| PG Pin Hysteresis               | V <sub>HYS(PG)</sub>         | For rising V <sub>OUT</sub>                                                                   |                                                          | 1.7% ×<br>V <sub>OUT</sub> |                           | V   |                   |

| PG Pin Low-Level Output Voltage | $V_{OL(PG)}$                 | $V_{OUT} < V_{IT(PG)}$ , $I_{PG} = -1mA$ (current                                             | into device)                                             |                            | 0.17                      | 0.3 | V                 |

| PG Pin Leakage Current          | I <sub>Ikg(PG)</sub>         | $V_{OUT} > V_{IT(PG)}$ , $V_{PG} = 7V$ , $V_{IN} = 7V$                                        |                                                          |                            | 0.01                      | 0.5 | μΑ                |

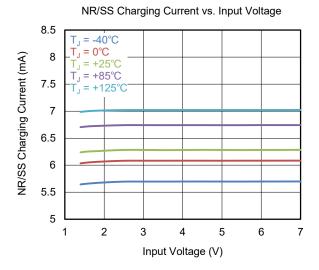

| NR/SS Pin Charging Current      | I <sub>NR/SS</sub>           | V <sub>NR/SS</sub> = GND, V <sub>IN</sub> = 7V                                                |                                                          | 3.5                        | 5.8                       | 8.5 | μΑ                |

| FB Pin Leakage Current          | I <sub>FB</sub>              | V <sub>IN</sub> = 7V                                                                          |                                                          | -120                       |                           | 120 | nA                |

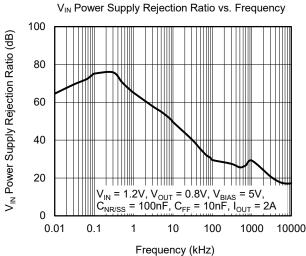

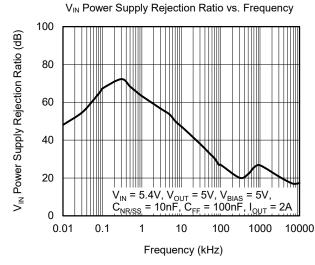

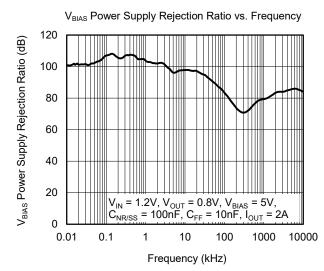

|                                 | PSRR                         | $V_{IN}$ to $V_{OUT}$ , $V_{OUT} = 0.8V$ ,<br>$(V_{IN} - V_{OUT}) = 0.4V$ , $V_{BIAS} = 5V$ , | f = 10kHz                                                |                            | 51                        |     | - dB              |

| Dayer Supply Rejection Retio    |                              | $I_{OUT} = 2A, C_{NR/SS} = 100nF,$<br>$C_{FF} = 10nF, C_{OUT} = 22\mu F$                      | f = 500kHz                                               |                            | 23                        |     |                   |

| Power Supply Rejection Ratio    |                              | $V_{IN}$ to $V_{OUT}$ , $V_{OUT} = 5V$ , $(V_{IN} - V_{OUT}) = 0.4V$ , $I_{OUT} = 2A$ ,       | f = 10kHz                                                |                            | 47                        |     | αБ                |

|                                 |                              | $C_{NR/SS}$ = 100nF, $C_{FF}$ = 10nF, $C_{OUT}$ = 22 $\mu$ F                                  | f = 500kHz                                               |                            | 20                        |     |                   |

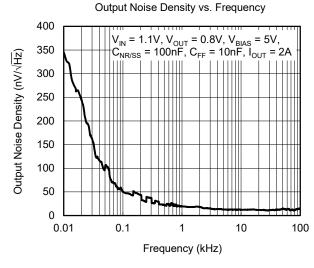

| Outrod Voltages Nation          | /oltage Noise e <sub>n</sub> | f = 10Hz to 100kHz, I <sub>OUT</sub> = 2A,                                                    | $V_{OUT} = 0.8V,$<br>$V_{IN} = 1.1V,$<br>$V_{BIAS} = 5V$ |                            | 5                         |     |                   |

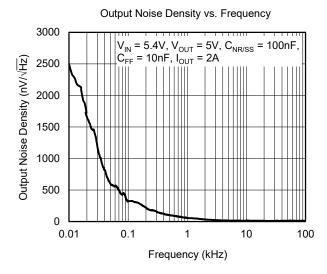

| Output Voltage Noise            |                              | $C_{NR/SS} = 100nF$ , $C_{FF} = 10nF$                                                         | $V_{OUT} = 5V,$<br>$V_{IN} = 5.4V,$<br>$V_{BIAS} = 0V$   |                            | 11                        |     | μV <sub>RMS</sub> |

| Thermal Shutdown Temperature    | T <sub>SHDN</sub>            |                                                                                               |                                                          |                            | 165                       |     | °C                |

| Thermal Shutdown Hysteresis     | $\Delta T_{SHDN}$            |                                                                                               |                                                          |                            | 25                        |     | °C                |

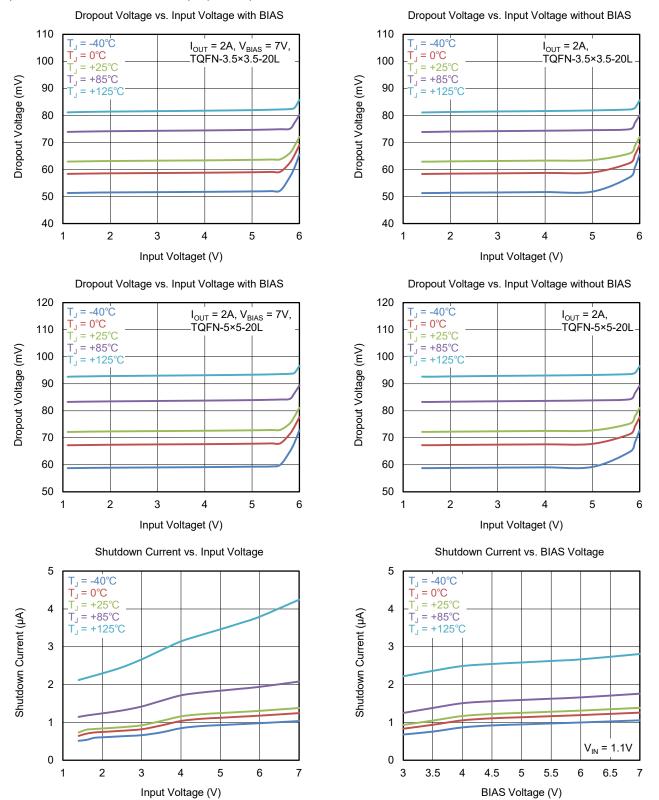

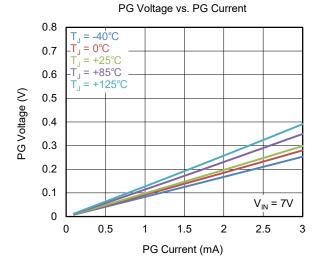

#### TYPICAL PERFORMANCE CHARACTERISTICS

$T_J$  = +25°C,  $V_{IN}$  = ( $V_{OUT(NOM)}$  + 0.4V) or 1.4V (whichever is greater),  $V_{BIAS}$  = Open,  $V_{OUT(NOM)}$  = 0.8V,  $V_{EN}$  = 1.1V,  $C_{IN}$  =10 $\mu$ F,  $C_{OUT}$  = 22 $\mu$ F,  $C_{NR/SS}$  = 0nF, no  $C_{FF}$ , and PG pin pulled up to  $V_{IN}$  with 100 $k\Omega$ , unless otherwise noted.

Time (50µs/div)

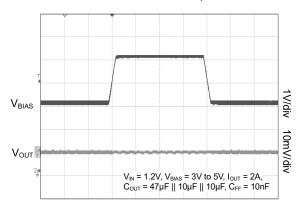

V<sub>BIAS</sub> Line Transient Response

Time (50µs/div)

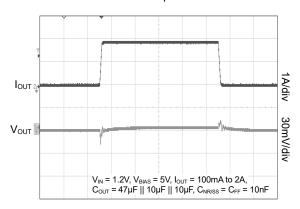

#### Load Transient Response with BIAS

Time (200µs/div)

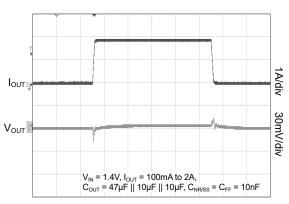

#### Load Transient Response without BIAS

Time (200µs/div)

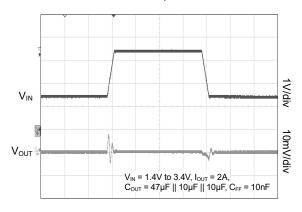

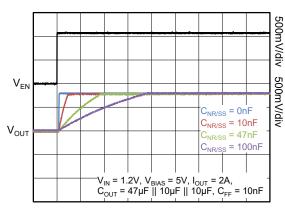

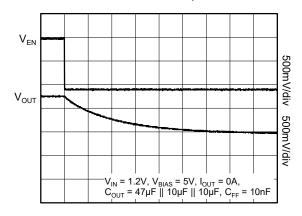

#### Enable Turn-On Response

Time (5ms/div)

#### Enable Turn-Off Response

Time (5ms/div)

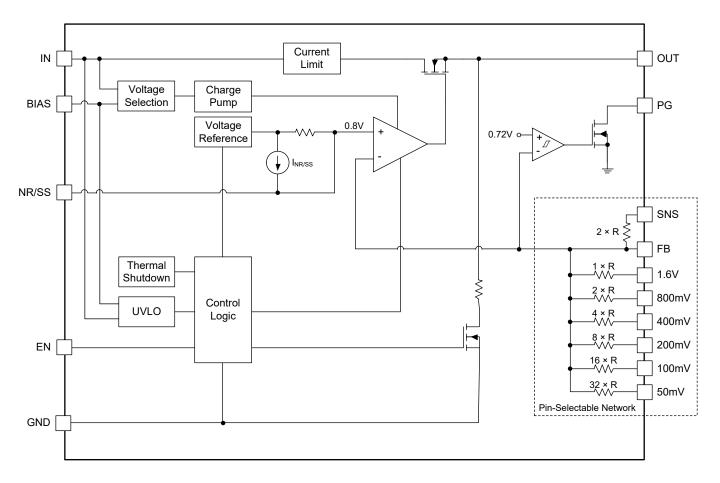

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. Block Diagram

#### **APPLICATION INFORMATION**

The SGM2049 is a high accuracy, low noise, fast transient response high performance LDO, it provides 2A output current. These features make the device a reliable solution to solve many challenging problems in the generation of clean and accurate power supply. The high performance also makes the SGM2049 useful in a variety of applications. The SGM2049 provides the protection functions for output overload, output short -circuit condition and overheating.

The SGM2049 provides an EN pin as an external chip enable control to enable/disable the device. When the regulator is in shutdown state, the shutdown current consumes as low as  $1.4\mu A$  (TYP).

#### Input Capacitor Selection (C<sub>IN.</sub> C<sub>BIAS</sub>)

The input decoupling capacitor should be placed as close as possible to the IN pin and BIAS pin for ensuring the device stability.  $C_{IN} = 10 \mu F/C_{BIAS} = 5 \mu F$  or larger X7R or X5R ceramic capacitors are selected to get good dynamic performance.

When  $V_{\text{IN}}$  is required to provide large current instantaneously, a large effective input capacitor is required. Multiple input capacitors can limit the input tracking inductance. Adding more input capacitors is available to restrict the ringing and to keep it below the device absolute maximum ratings.

#### **Output Capacitor Selection (COUT)**

The output capacitor should be placed as close as possible to the OUT pin.  $10\mu F$  or larger X7R or X5R ceramic capacitor is selected to get good dynamic performance. The minimum effective capacitance of  $C_{\text{OUT}}$  that SGM2049 can remain stable is  $10\mu F$ . For ceramic capacitor, temperature, DC bias and package size will change the effective capacitance, so enough margin of  $C_{\text{OUT}}$  must be considered in design. Additionally,  $C_{\text{OUT}}$  with larger capacitance and lower ESR will help increase the high frequency PSRR and improve the load transient response.

# Noise-Reduction and Soft-Start Capacitor Selection ( $C_{NR/SS}$ )

The SGM2049 is designed for a programmable, monotonic soft-start time of output rising, and it can be

achieved via an external capacitor ( $C_{NR/SS}$ ) on the NR/SS pin. Using an external  $C_{NR/SS}$  is recommended for general application. It not only minimizes the inrush current but also helps reduce the noise component from internal reference.

#### **Adjustable Output Voltage**

The SGM2049 can be set either with the internal pin-selectable network or by connecting with external resistors to achieve different output voltages. When the output voltage range is from 0.8V to 3.95V, the SGM2049 can be programmed by using the pin-selectable network. When the output voltage range is greater than 3.95V and up to 5.2V, external resistors must be used as shown in Figure 3. The output voltage is determined by the following equation:

$$V_{OUT} = 0.8V \times \left(1 + \frac{R_1}{R_2}\right)$$

(1)

One parallel capacitor ( $C_{FF}$  = 10nF) with  $R_1$  can be used to improve the feedback loop stability and PSRR, increase the transient response and reduce the output noise. Use an  $R_1$  approximately  $12k\Omega$  to maintain a  $5\mu A$  minimum load.

Figure 3. Adjustable Output Voltage Application

#### **APPLICATION INFORMATION (continued)**

# Pin-Selectable Programmable Output Voltage

Pin-selectable programmable output voltage is achieved with the pin-selectable resistors via pin 2 and pins 5 to 11. Each pin can be grounded (active) or floating (open) or connected to the SNS pin. Pin-selectable programming is set as the internal reference voltage by Equation 2 plus the accumulated sum of the respective voltages assigned to each active pin. Table 1 shows these voltage values related to each active pin setting for reference.

$V_{OUT} = 0.8V + (\Sigma Pin-Selectable Pins to Ground)$  (2)

Table 1. Pin-Selectable Programmable Output Voltage

| Pin-Selectable Program Pins (Active Low) | Additive Output Voltage Level |

|------------------------------------------|-------------------------------|

| Pin 5 (50mV)                             | 50mV                          |

| Pin 6 (100mV)                            | 100mV                         |

| Pin 7 (200mV)                            | 200mV                         |

| Pin 9 (400mV)                            | 400mV                         |

| Pin 10 (800mV)                           | 800mV                         |

| Pin 11 (1.6V)                            | 1.6V                          |

The output voltage is set according to Equation 1 as for the adjustable operation, but  $R_1$  and  $R_2$  are internally integrated and matched for higher accuracy. By reducing the value of  $R_1$  and connecting any of the pin-selectable pins to the SNS pin, the resolution of the internal feedback network can be improved.

#### **Enable Control**

The EN pin of the SGM2049 is used to enable/disable the device and to deactivate/activate the output automatic discharge function.

When the EN pin voltage is lower than  $V_{IL(EN)}$ , the device is in shutdown state, there is no current flowing from IN to OUT pins. In this state, the automatic discharge transistor is active to discharge the output voltage through a  $260\Omega$  (TYP) resistor.

When the EN pin voltage is higher than  $V_{\text{IH}(\text{EN})}$ , the device is in active state, the input voltage is regulated to the output voltage and the automatic discharge transistor is turned off.

#### **Reverse Current Protection**

The pass transistor has an inherent body diode which will be forward biased in the case when  $V_{OUT} > (V_{IN} +$

0.3V). If extended reverse voltage operation is anticipated, external limiting might be appropriate.

#### **Negatively Biased Output**

When the output voltage is negative, the chip may not start up due to parasitic effects. Ensure that the output is greater than -0.3V under all conditions. If negatively biased output is excessive and expected in the application, a Schottky diode can be added between the OUT pin and GND pin.

# Output Current Limit and Short-Circuit Protection

When overload events happen, the output current is internally limited to 3.2A (TYP). When the OUT pin is shorted to ground, the short-circuit protection will limit the output current to 1.7A (TYP).

#### Thermal Shutdown

The SGM2049 can detect the temperature of die. When the die temperature exceeds the threshold value of thermal shutdown, the SGM2049 will be in shutdown state and it will remain in this state until the die temperature decreases to +140°C.

#### Power Dissipation (P<sub>D</sub>)

Thermal protection limits power dissipation in the SGM2049. When power dissipation on pass element ( $P_D = (V_{IN} - V_{OUT}) \times I_{OUT}$ ) is too much and the operating junction temperature exceeds +165°C, the OTP circuit starts the thermal shutdown function and turns the pass element off.

Therefore, thermal analysis for the chosen application is important to guarantee reliable performance over all conditions. To guarantee reliable operation, the junction temperature of the SGM2049 must not exceed +125°C.

The maximum allowable power dissipation depends on the thermal resistance of the IC package, the PCB layout, the rate of surrounding airflow, and the difference between the junction temperature and ambient temperature. The maximum power dissipation can be approximated using the following equation:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A)/\theta_{JA}$$

(3)

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction -to-ambient thermal resistance.

### 2A, High Accuracy, Low Noise, **Low Dropout Linear Regulator**

#### **SGM2049**

#### **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Original (DECEMBER 2021) to REV.A

Page

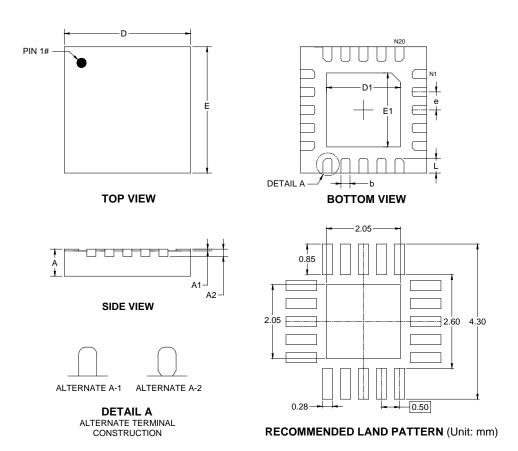

# PACKAGE OUTLINE DIMENSIONS TQFN-3.5×3.5-20L

| Complex | Dimensions In Millimeters |           |       |  |  |  |  |

|---------|---------------------------|-----------|-------|--|--|--|--|

| Symbol  | MIN                       | MOD       | MAX   |  |  |  |  |

| А       | 0.700                     | 0.750     | 0.800 |  |  |  |  |

| A1      | -                         | -         | 0.050 |  |  |  |  |

| A2      |                           | 0.203 REF |       |  |  |  |  |

| D       | 3.450                     | 3.500     | 3.550 |  |  |  |  |

| D1      | 2.000                     | 2.050     | 2.100 |  |  |  |  |

| E       | 3.450                     | 3.500     | 3.550 |  |  |  |  |

| E1      | 2.000                     | 2.050     | 2.100 |  |  |  |  |

| b       | 0.200                     | 0.250     | 0.300 |  |  |  |  |

| е       |                           | 0.500 BSC |       |  |  |  |  |

| L       | 0.350 0.400 0.450         |           |       |  |  |  |  |

NOTE: This drawing is subject to change without notice.

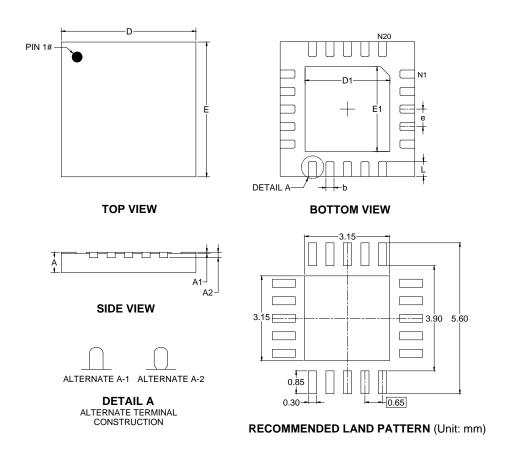

# PACKAGE OUTLINE DIMENSIONS TQFN-5×5-20L

| Cumb of | Dimensions In Millimeters |           |       |  |  |  |  |

|---------|---------------------------|-----------|-------|--|--|--|--|

| Symbol  | MIN                       | MOD       | MAX   |  |  |  |  |

| А       | 0.700                     | 0.750     | 0.800 |  |  |  |  |

| A1      | 0.000                     | -         | 0.050 |  |  |  |  |

| A2      |                           | 0.203 REF |       |  |  |  |  |

| D       | 4.950                     | 5.000     | 5.050 |  |  |  |  |

| D1      | 3.100                     | 3.150     | 3.200 |  |  |  |  |

| Е       | 4.950                     | 5.000     | 5.050 |  |  |  |  |

| E1      | 3.100                     | 3.150     | 3.200 |  |  |  |  |

| b       | 0.250                     | 0.300     | 0.350 |  |  |  |  |

| е       |                           | 0.650 BSC |       |  |  |  |  |

| L       | 0.500 0.550 0.600         |           |       |  |  |  |  |

NOTE: This drawing is subject to change without notice.

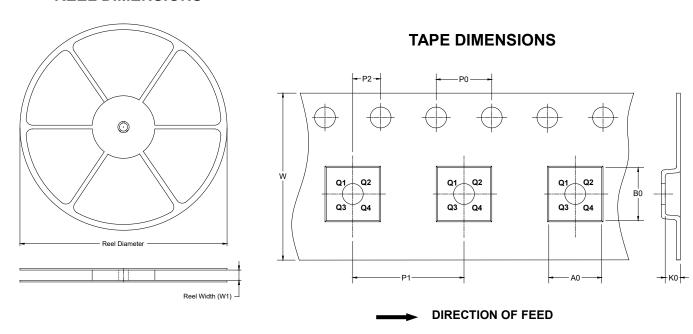

#### TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type     | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TQFN-3.5×3.5-20L | 13"              | 12.4                     | 3.80       | 3.80       | 0.95       | 4.0        | 8.0        | 2.0        | 12.0      | Q2               |

| TQFN-5×5-20L     | 13"              | 12.4                     | 5.30       | 5.30       | 1.10       | 4.0        | 8.0        | 2.0        | 12.0      | Q2               |

#### **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |

|-----------|----------------|---------------|----------------|--------------|

| 13"       | 386            | 280           | 370            | 5            |