# 3-Series to 16-Series High Accuracy Battery Monitor and Protector

### **GENERAL DESCRIPTION**

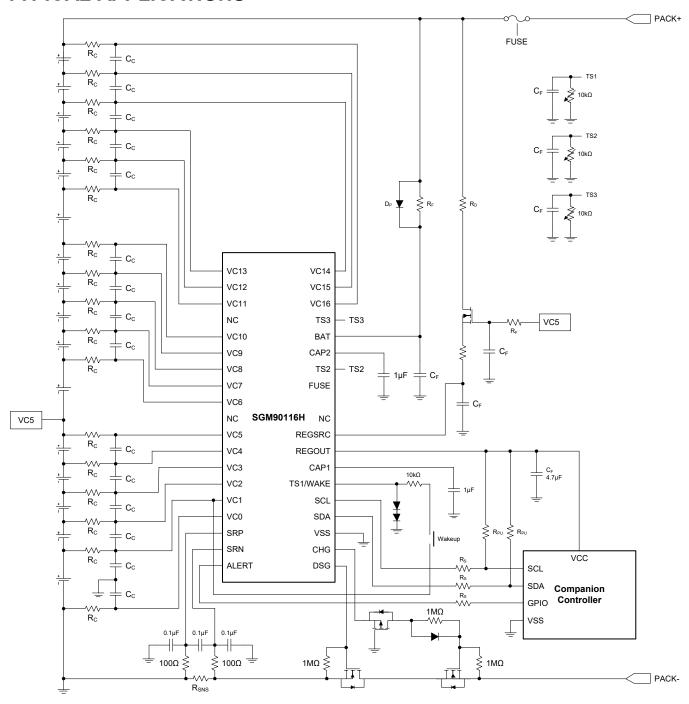

The SGM90116H is an analog front end (AFE) which is specified for general purpose monitoring and protecting of stacked Li-lon, Li-polymer, and LiFePO4 batteries. The device can monitor 3-series to 16-series battery cells.

The device supports autonomous and host controlled cell balancing.

The device supports software configurable primary protection and secondary protection.

The device has an on-chip charge up and supports low-side NFET drivers.

The device supports 100kHz I<sup>2</sup>C standards communication interface.

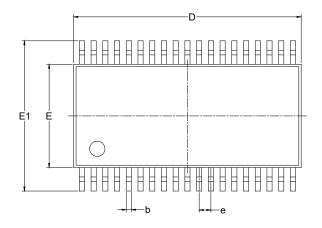

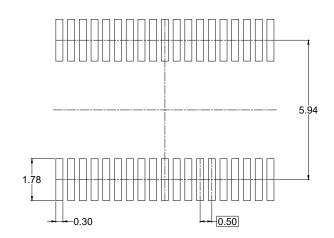

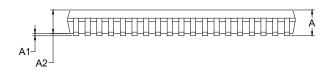

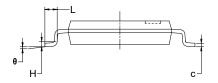

The SGM90116H is available in a Green TSSOP-38 package.

### **APPLICATIONS**

Battery Pack Management

E-Bike and E-Scooter

Battery Powered Electric Tools and Garden Tools

Unmanned Aerial Vehicle

Industrial Power Storage Battery Pack

### **FEATURES**

- Monitor 3-Series to 16-Series Cells

- Integrated Secondary Chemical Fuse Drive Protection

- Two Independent ADCs

- High Accuracy Coulomb Counter with ±2LSB (TYP) Input Offset Error

- High Accuracy Cell Voltage Measurement ±2.5mV (TYP)

- Support Simultaneous Current and Voltage Sampling

- Multiple Working Modes

- Support Temperature Sensing Using Internal Sensor and up to 3 External Thermistors

- Tolerant of Random Cell Attach Sequence on Production Line

- Programmable LDO for External System Power

- Available in a Green TSSOP-38 Package

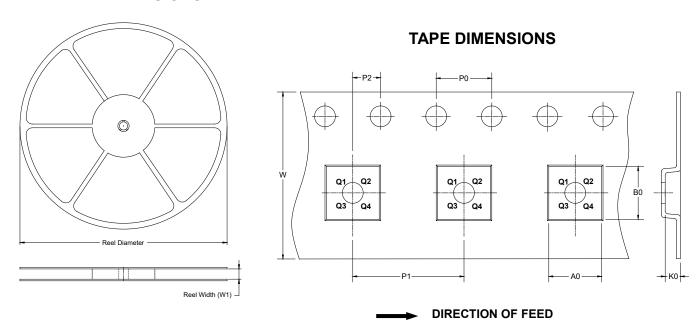

### PACKAGE/ORDERING INFORMATION

| MODEL     | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING          | PACKING<br>OPTION   |

|-----------|------------------------|-----------------------------------|--------------------|-----------------------------|---------------------|

| SGM90116H | TSSOP-38               | -40°C to +85°C                    | SGM90116HYTS38G/TR | SGM90116H<br>YTS38<br>XXXXX | Tape and Reel, 4000 |

### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

| $\mathbf{X}\mathbf{X}\mathbf{X}\mathbf{X}\mathbf{X}$ |                  |

|------------------------------------------------------|------------------|

|                                                      | Vendor Code      |

|                                                      | Trace Code       |

|                                                      | Date Code - Year |

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

## **ABSOLUTE MAXIMUM RATINGS**

| ABSOLUTE MAXIMUM RATI                              | NGS                           |

|----------------------------------------------------|-------------------------------|

| VC(n) - VC(n-1)                                    | 0.3V to 80V                   |

| Supply Voltage, V <sub>BAT</sub>                   | 0.3V to 80V                   |

| Cell Input Pins Voltage                            | 0.3V to 80V                   |

| SRN, SRP Input Voltage                             | 0.3V to 1.98V                 |

| SCL, SDA Input Voltage                             | 0.3V to V <sub>REGOUT</sub>   |

| REGSRC Input Voltage                               | 0.3V to 80V                   |

| REGOUT, ALERT Output Voltage                       | 0.3V to 6.6V                  |

| DSG Output Voltage                                 | 0.3V to 20V                   |

| CHG Output Voltage                                 | 0.3V to V <sub>CHGCLAMP</sub> |

| Cell Balancing Current (Per Cell), I <sub>CB</sub> | 50mA                          |

| Package Thermal Resistance                         |                               |

| TSSOP-38, $\theta_{JA}$                            | 56.6°C/W                      |

| TSSOP-38, θ <sub>JB</sub>                          | 30.1°C/W                      |

| TSSOP-38, $\theta_{JC}$                            | 16.4°C/W                      |

| Junction Temperature                               | +150°C                        |

| Storage Temperature Range                          |                               |

| Lead Temperature (Soldering, 10s)                  | +260°C                        |

| ESD Susceptibility (1) (2)                         |                               |

| HBM                                                |                               |

| CDM                                                | ±1000V                        |

| NOTES:                                             |                               |

- 1. For human body model (HBM), all pins comply with ANSI/ESDA/JEDEC JS-001 specifications.

- 2. For charged device model (CDM), all pins comply with ANSI/ESDA/JEDEC JS-002 specifications.

### RECOMMENDED OPERATING CONDITIONS

| Supply Voltage, V <sub>BAT</sub> | 6V to 72V                 |

|----------------------------------|---------------------------|

| Cell Input Pins Voltage          | 0V to 6.55V               |

| SRP - SRN Input Voltage          | 200mV to 200mV            |

| SCL, SDA Input Voltage           | 0V to V <sub>REGOUT</sub> |

| TSx - VSS Input Voltage          | 0V to 1.8V                |

| REGSRC Input Voltage             | 6V to 25V                 |

| CHG, DSG Output Voltage          | 0V to 16V                 |

| REGOUT Output Voltage            | 0V to 5V                  |

|                                  |                           |

| ALERT Output Voltage                               | 0V to V <sub>REGOUT</sub> |

|----------------------------------------------------|---------------------------|

| Cell Balancing Current (Per Cell), I <sub>CB</sub> | 0mA to 50mA               |

| External Cell Input Resistance, R <sub>C</sub>     | 20Ω to 100Ω               |

| External Cell Input Capacitance, Cc                | 0.1µF to 1µF              |

| External Supply Filter Resistance, R <sub>F</sub>  | 40Ωto 1kΩ                 |

| External Supply Filter Capacitance, C <sub>F</sub> | 1μF to 10μF               |

| Sense Resistor Filter Resistance, RFILT            | 100Ω                      |

| ALERT Pin to VSS Resistor, R <sub>ALERT</sub>      | 1ΜΩ                       |

| REGOUT Loading Capacitance, C <sub>L</sub>         | 1µF                       |

| REGSRC Input Capacitance, C <sub>1</sub>           | 1µF                       |

| CAP1, CAP2 (Output Capacitance), C <sub>CAP</sub>  |                           |

| External Thermistor Nominal Resistance             | e (103AT) at +25°C,       |

| R <sub>TS</sub>                                    | 10kΩ                      |

| Operating Temperature Range                        | 40°C to +85°C             |

|                                                    |                           |

### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

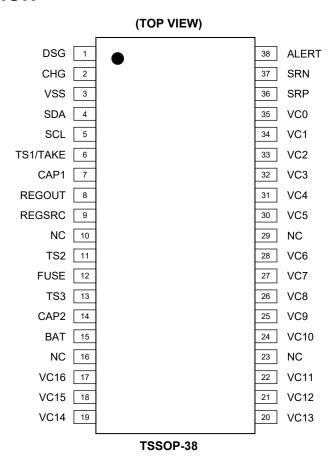

## **PIN CONFIGURATION**

## **PIN DESCRIPTION**

| PIN               | NAME     | TYPE  | FUNCTION                                                                                                                                                                |

|-------------------|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                 | DSG      | AO    | Discharge FET Driver.                                                                                                                                                   |

| 2                 | CHG      | AO    | Charge FET Driver.                                                                                                                                                      |

| 3                 | VSS      | GND   | Ground.                                                                                                                                                                 |

| 4                 | SDA      | DI/DO | I <sup>2</sup> C Interface, Serial Data Input and Output.                                                                                                               |

| 5                 | SCL      | DI    | I <sup>2</sup> C Interface, Serial Clock Input.                                                                                                                         |

| 6                 | TS1/WAKE | Al    | Thermistor Input/Wake up.                                                                                                                                               |

| 7                 | CAP1     | AO    | Internal LDO Decoupling Pin. It needs an external capacitor to be connected.                                                                                            |

| 8                 | REGOUT   | AO    | 1.8V/2.5V/3.0V/3.3V/5.0V Voltage Output.                                                                                                                                |

| 9                 | REGSRC   | Al    | REG LDO Input.                                                                                                                                                          |

| 10, 16,<br>23, 29 | NC       |       | Not Connected.                                                                                                                                                          |

| 11                | TS2      | Al    | Thermistor Input.                                                                                                                                                       |

| 12                | FUSE     | AO    | Fuse Blower.                                                                                                                                                            |

| 13                | TS3      | Al    | Thermistor Input.                                                                                                                                                       |

| 14                | CAP2     | AO    | Internal LDO Decoupling Pin. It needs an external capacitor to be connected.                                                                                            |

| 15                | BAT      | Al    | Primary Power Supply.                                                                                                                                                   |

| 17                | VC16     | Al    | Sense voltage input pin for the cell16 from the bottom of the stack, balance current input for the cell16 from the bottom of stack, and top-of-stack measurement point. |

## **PIN DESCRIPTION (continued)**

| PIN | NAME  | I/O | FUNCTION                                                                                                                                                                                                                                          |

|-----|-------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18  | VC15  | Al  | Sense voltage input pin for the cell15 from the bottom of the stack, balance current input for the cell15 from the bottom of stack, and return balance current for the cell16 from the bottom of stack.                                           |

| 19  | VC14  | AI  | Sense voltage input pin for the cell14 from the bottom of the stack, balance current input for the cell14 from the bottom of stack, and return balance current for the cell15 from the bottom of stack.                                           |

| 20  | VC13  | AI  | Sense voltage input pin for the cell13 from the bottom of the stack, balance current input for the cell13 from the bottom of stack, and return balance current for the cell14 from the bottom of stack.                                           |

| 21  | VC12  | AI  | Sense voltage input pin for the cell12 from the bottom of the stack, balance current input for the cell12 from the bottom of stack, and return balance current for the cell13 from the bottom of stack.                                           |

| 22  | VC11  | AI  | Sense voltage input pin for the cell11 from the bottom of the stack, balance current input for the cell11 from the bottom of stack, and return balance current for the cell12 from the bottom of stack.                                           |

| 24  | VC10  | AI  | Sense voltage input pin for the cell10 from the bottom of the stack, balance current input for the cell10 from the bottom of stack, and return balance current for the cell11 from the bottom of stack.                                           |

| 25  | VC9   | AI  | Sense voltage input pin for the cell9 from the bottom of the stack, balance current input for the cell9 from the bottom of stack, and return balance current for the cell10 from the bottom of stack.                                             |

| 26  | VC8   | AI  | Sense voltage input pin for the cell8 from the bottom of the stack, balance current input for the cell8 from the bottom of stack, and return balance current for the cell9 from the bottom of stack.                                              |

| 27  | VC7   | AI  | Sense voltage input pin for the cell7 from the bottom of the stack, balance current input for the cell7 from the bottom of stack, and return balance current for the cell8 from the bottom of stack.                                              |

| 28  | VC6   | AI  | Sense voltage input pin for the cell6 from the bottom of the stack, balance current input for the cell6 from the bottom of stack, and return balance current for the cell7 from the bottom of stack.                                              |

| 30  | VC5   | AI  | Sense voltage input pin for the cell5 from the bottom of the stack, balance current input for the cell5 from the bottom of stack, and return balance current for the cell6 from the bottom of stack.                                              |

| 31  | VC4   | AI  | Sense voltage input pin for the cell4 from the bottom of the stack, balance current input for the cell4 from the bottom of stack, and return balance current for the cell5 from the bottom of stack.                                              |

| 32  | VC3   | AI  | Sense voltage input pin for the cell3 from the bottom of the stack, balance current input for the cell3 from the bottom of stack, and return balance current for the cel4 from the bottom of stack.                                               |

| 33  | VC2   | Al  | Sense voltage input pin for the cell2 from the bottom of the stack, balance current input for the cell2 from the bottom of stack, and return balance current for the cell3 from the bottom of stack.                                              |

| 34  | VC1   | AI  | Sense voltage input pin for the cell1 from the bottom of the stack, balance current input for the cell1 from the bottom of stack, and return balance current for the cell2 from the bottom of stack.                                              |

| 35  | VC0   | AI  | Sense voltage input pin for the cell0 from the bottom of the stack, balance current input for the cell0 from the bottom of stack, and return balance current for the cell1 from the bottom of stack.                                              |

| 36  | SRP   | Al  | Analog input pin connected to the internal coulomb counter peripheral for integrating a small voltage between SRP and SRN, where SRN is the bottom of the sense resistor. A charging current generates a positive voltage at SRP relative to SRN. |

| 37  | SRN   | Al  | Analog input pin connected to the internal coulomb counter peripheral for integrating a small voltage between SRP and SRN, where SRN is the bottom of the sense resistor. A charging current generates a positive voltage at SRP relative to SRN. |

| 38  | ALERT | DIO | ALERT Output and Override Input.                                                                                                                                                                                                                  |

NOTE: AO = Analog Output, AI = Analog Input, DI = Digital Input, DO = Digital Output, DI/DO = Digital Input/Output.

## **ELECTRICAL CHARACTERISTICS**

( $V_{BAT}$  = 48V,  $T_A$  = -40°C to +85°C, typical values are at  $T_A$  = +25°C unless otherwise noted.)

| PARAMETER                                                                               | SYMBOL                  | CONDITIONS                                                               | MIN  | TYP    | MAX    | UNITS    |  |

|-----------------------------------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------|------|--------|--------|----------|--|

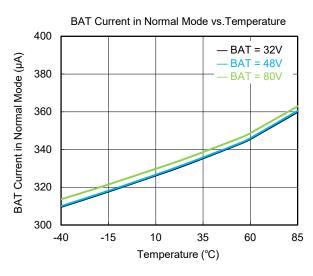

| Supply Current                                                                          |                         |                                                                          |      |        |        |          |  |

| Normal Mode: VADC Off, IADC/CC Off                                                      | I <sub>DD</sub>         | Into BAT pin                                                             |      | 90     | 185    |          |  |

| Normal Mode: VADC On, IADC/CC Off                                                       | I <sub>DD</sub>         | Into BAT pin                                                             |      | 300    | 370    |          |  |

| Normal Mode: VADC Off, IADC/CC On                                                       | I <sub>DD</sub>         | Into BAT pin                                                             |      | 120    | 235    | μA       |  |

| Normal Mode: VADC On, IADC/CC On                                                        | I <sub>DD</sub>         | Into BAT pin                                                             |      | 330    | 430    |          |  |

| Normal Mode                                                                             | I <sub>CC_REGSRC</sub>  | Into REGSRC pin                                                          |      | 2.2    | 11     | μΑ       |  |

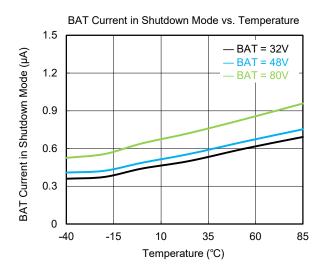

| Ship/Shutdown Mode                                                                      | I <sub>SHIP</sub>       | Device is fully shut down, only BG and BOOT detectors are on             |      | 1.1    | 1.9    | μA       |  |

| Leakage and Offset Currents                                                             |                         |                                                                          |      |        |        |          |  |

| Cell Measurement Input Current                                                          | d <sub>ICELL</sub>      | Measured into VC0 ~ VC15                                                 |      |        | 0.3    | μΑ       |  |

| Terminal Input Leakage                                                                  | I <sub>LKG</sub>        |                                                                          |      |        | 1.5    | μΑ       |  |

| Internal Power Control (Startup and                                                     | Shutdown)               |                                                                          |      |        |        |          |  |

| Power-On Reset Threshold (1)                                                            | $V_{POR}$               | V <sub>BAT</sub> rising                                                  |      | 4      | 4.7    | V        |  |

| Power-On Reset Hysteresis                                                               | V <sub>POR_HYS</sub>    | Device shuts down when $V_{BAT} < V_{POR} - V_{POR\_HYS}$                |      | 400    |        | mV       |  |

| Shutdown Voltage (1)                                                                    | V <sub>SHUT</sub>       | V <sub>BAT</sub> falling                                                 | 3.1  | 3.6    |        | V        |  |

| Time Delay after Boot Signal on TS1/WAKE before I <sup>2</sup> C Communications Allowed | t <sub>I2CSTARTUP</sub> | Delay after boot sequence when I <sup>2</sup> C communication is allowed |      | 0.4    |        | ms       |  |

| Device Boot Startup Delay                                                               | t <sub>BOOTREADY</sub>  | Delay after boot signal when device has completed full boot-up sequence  |      | 2.3    |        | ms       |  |

| Measurement Schedule                                                                    |                         | completed full boot-up sequence                                          |      |        |        |          |  |

|                                                                                         |                         | In normal mode, SETTLE[1:0] bits = 0                                     |      | 250.56 |        |          |  |

|                                                                                         |                         | In normal mode, SETTLE[1:0] bits = 1/2/3                                 |      | 332.74 |        |          |  |

|                                                                                         |                         | In fast mode, SETTLE[1:0] bits = 0                                       |      | 112.54 |        | ms       |  |

| Cell Voltage Measurement Interval                                                       | tvcell                  | In fast mode, SETTLE[1:0] bits = 1                                       |      | 202.59 |        |          |  |

|                                                                                         |                         | In fast mode, SETTLE[1:0] bits = 2                                       |      | 292.82 |        |          |  |

|                                                                                         |                         | In fast mode, SETTLE[1:0] bits = 3                                       |      | 360.13 |        |          |  |

|                                                                                         |                         | In normal mode, SETTLE[1:0] bits = 0                                     |      | 501.20 |        |          |  |

| Temperature Measurement Interval                                                        | t <sub>TEMP</sub>       | In normal mode, SETTLE[1:0] bits = 1/2/3                                 |      | 665.47 |        | ms       |  |

| 16-Bit ADC for Cell Voltage and Temp                                                    | erature Me              | easurement                                                               |      | 1      |        | <u>I</u> |  |

| ADC Measurement Recommend                                                               | 400                     | V <sub>CELL</sub> measurements                                           | 0    |        | 6.55   | V        |  |

| Operation Range                                                                         | ADC <sub>RANGE</sub>    | TS/Temperature measurements                                              | 0    |        | 1.8    | V        |  |

| ADC LSB Value                                                                           | ADC <sub>LSB</sub>      |                                                                          |      | 100    |        | μV       |  |

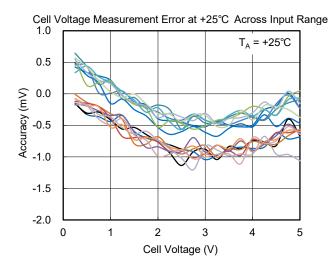

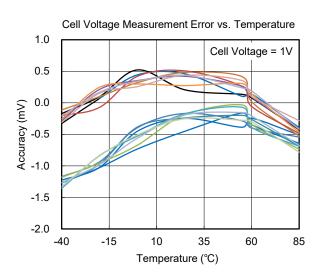

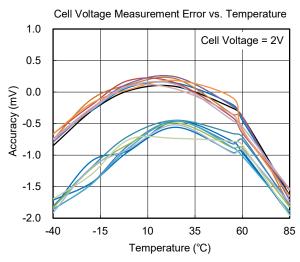

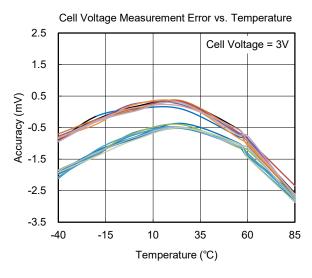

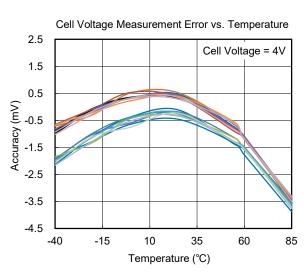

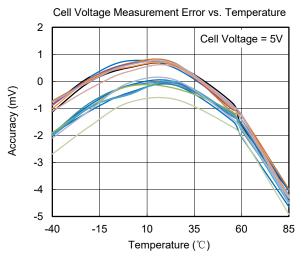

|                                                                                         |                         | T <sub>A</sub> = +25°C, V <sub>CELL</sub> = 1.0V to 5.0V                 |      | ±2.5   |        | mV       |  |

| ADC Cell Voltage Accuracy (2)                                                           | ADC                     | $T_A = -40^{\circ}C$ to +60°C, $V_{CELL} = 1.0V$ to 5.0V                 | -15  |        | 15     |          |  |

|                                                                                         |                         | T <sub>A</sub> = -40°C to +85°C, V <sub>CELL</sub> = 1.0V to 5.0V        | -20  |        | 20 mV  |          |  |

| 16-Bit CC for Pack Current Measurer                                                     | nent                    |                                                                          |      |        |        |          |  |

| CC Input Voltage Range                                                                  | CC <sub>RANGE</sub>     |                                                                          | -200 |        | 200    | mV       |  |

| CC LSB Value                                                                            | CC <sub>LSB</sub>       | CC running constantly                                                    |      | 9.3    |        | μV       |  |

| Conversion Time                                                                         | tCC <sub>READ</sub>     | Single conversion                                                        |      | 250.62 |        | ms       |  |

| Current Conversion Time (3)                                                             | tCUR <sub>READ</sub>    |                                                                          | 4.88 |        | 15.616 | ms       |  |

| Integral Nonlinearity                                                                   | CC <sub>INL</sub>       | 16-bit, best fit over input voltage range ±200mV                         | -15  |        | 15     | LSB      |  |

| Offset Error                                                                            | CC <sub>OFFSET</sub>    |                                                                          |      | ±2     |        | LSB      |  |

|                                                                                         | CC <sub>OFFSET</sub>    |                                                                          |      |        |        |          |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

(V<sub>BAT</sub> = 48V,  $T_A$  = -40°C to +85°C, typical values are at  $T_A$  = +25°C unless otherwise noted.)

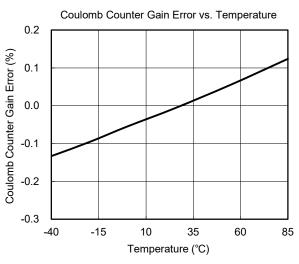

|                                                               | Over input voltage range                                   |        | +0.0E0/ |               |       |

|---------------------------------------------------------------|------------------------------------------------------------|--------|---------|---------------|-------|

| 0 1 5 5 5                                                     |                                                            |        | ±0.05%  |               | FSR   |

| Gain Error Drift CC <sub>GAIN_DRIFT</sub> C                   | Over input voltage range                                   | -0.8%  |         | 0.8%          | FSR   |

| Effective Input Resistance CC <sub>RIN</sub>                  |                                                            | 0.2    | 0.6     | 1.2           | ΜΩ    |

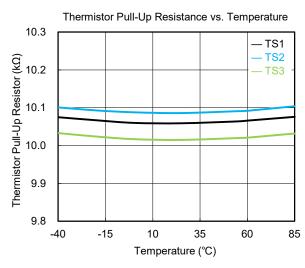

| Thermistor Bias                                               |                                                            |        |         |               |       |

| Pull-Up Resistance R <sub>TS</sub> 1                          | T <sub>A</sub> = +25°C                                     |        | 10      |               | kΩ    |

| Pull-Up Resistance across Temperature R <sub>TS_DRIFT</sub> 1 | $T_A = -40$ °C to +85°C                                    | 9.3    |         | 10.7          | kΩ    |

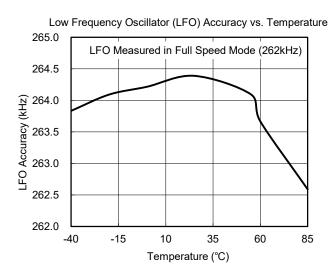

| osc                                                           |                                                            |        |         |               |       |

| Internal Clock Frequency f <sub>RC</sub>                      | T <sub>A</sub> = +25°C                                     |        | 262.144 |               | kHz   |

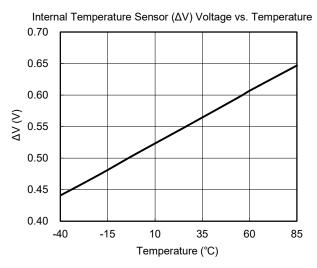

| Die Temperature                                               |                                                            |        |         |               |       |

| Die Temperature Voltage V <sub>DIE_TEMP25</sub> 7             | T <sub>A</sub> = +25°C                                     |        | 0.55    |               | V     |

| Die Temperature Voltage Drift V <sub>DIE_TEMP_DRIFT</sub>     |                                                            |        | 1.65    |               | mV/°C |

| OV Threshold Range OV <sub>RANGE</sub>                        |                                                            | 0x8020 | 0xAB20  | 0xBFEO        | ADC   |

| UV Threshold Range UV <sub>RANGE</sub>                        |                                                            | 0x4000 | 0x65C0  | 0x7FFC        | ADC   |

| OV and UV Threshold Step Size OV <sub>UVSTEP</sub>            |                                                            |        | 64      |               | LSB   |

| UV Minimum Value to Qualify UV <sub>MINQUAL</sub> E           | Below UV <sub>MINQUAL</sub> , the cell is shorted (unused) |        | 0x1380  |               | ADC   |

|                                                               | OV delay = 1s                                              |        | 0.6     |               |       |

| 0.45 1 - 5 0.4                                                | OV delay = 2s                                              |        | 1.8     |               |       |

| OV Delay Timer Options OV <sub>DELAY</sub>                    | OV delay = 4s                                              |        | 4.0     |               | S     |

|                                                               | OV delay = 8s                                              |        | 7.7     |               |       |

| Į.                                                            | UV delay = 1s                                              |        | 1.0     |               |       |

|                                                               | UV delay = 4s                                              |        | 3.8     |               | s     |

| UV Delay Timer Options UV <sub>DELAY</sub>                    | UV delay = 8s                                              |        | 7.8     |               |       |

| l l                                                           | UV delay = 16s                                             |        | 15.5    |               |       |

| SCD Threshold Options (4) SCD <sub>RANGE</sub> N              | Measured across (SRN - SRP)                                | 22     |         | 198           | mV    |

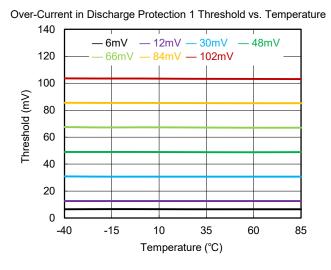

| OCD1 Threshold Options (4) OCD1 <sub>RANGE</sub> N            | Measured across (SRN - SRP)                                | 6      |         | 102           | mV    |

| OCD2 Threshold Options (4) OCD2 <sub>RANGE</sub> M            | Measured across (SRP - SRN)                                | 4      |         | 200           | mV    |

| OCC Threshold Options (4) OCC <sub>RANGE</sub> N              | Measured across (SRP - SRN)                                | 4      |         | 124           | mV    |

| COD Through and Other City                                    | RSNS = 0                                                   |        | 11      |               | mV    |

| SCD Threshold Step Size SCD <sub>STEP</sub> F                 | RSNS = 1                                                   |        | 22      |               | mV    |

| OCD1 Threshold Step Size OCD1 <sub>STEP</sub> F               | RSNS = 0                                                   |        | 3       |               | mV    |

| OCD1 Threshold Step Size OCD1 <sub>STEP</sub> F               | RSNS = 1                                                   |        | 6       |               | mV    |

| OCD2 Threshold Step Size OCD2 <sub>STEP</sub>                 |                                                            |        | 2       |               | mV    |

| OCC Threshold Step Size OCC <sub>STEP</sub>                   |                                                            |        | 2       |               | mV    |

|                                                               |                                                            |        | 173     |               | μs    |

| SCD Delay Options SCD <sub>DELAY</sub>                        |                                                            |        | 199     |               | μs    |

| SCD Delay Options SCD <sub>DELAY</sub>                        |                                                            |        | 297     |               | μs    |

|                                                               |                                                            |        | 482     |               | μs    |

| OCD1 Delay Options (4) OCD1 <sub>DELAY</sub>                  |                                                            | 18.84  |         | 1266          | ms    |

| OCD2 Delay Options OCD2 <sub>DELAY</sub>                      |                                                            | 4.88   |         | 374<br>(0x7F) | ms    |

| OCC Delay Options (4) OCC <sub>DELAY</sub>                    |                                                            | 3.856  |         | 375.53        | ms    |

| OCD1 Voltage Offset OCD1 <sub>OFFSET</sub>                    |                                                            | -3.5   | 2       | 7             | mV    |

## **ELECTRICAL CHARACTERISTICS (continued)**

(V<sub>BAT</sub> = 48V,  $T_A$  = -40°C to +85°C, typical values are at  $T_A$  = +25°C unless otherwise noted.)

| DADAMETED                                           | CVMBOL                  | CONDITIONS                                                                                                                              | MINI                       | TVD                       | MAX                        | UNITS |

|-----------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------|----------------------------|-------|

| PARAMETER                                           | SYMBOL                  | CONDITIONS                                                                                                                              | MIN                        | TYP                       |                            |       |

| OCD2 Voltage Offset                                 | OCD2 <sub>OFFSET</sub>  |                                                                                                                                         | -2                         | 2                         | 7                          | mV    |

| OCC Voltage Offset                                  | OCC <sub>OFFSET</sub>   |                                                                                                                                         | -6                         | 0.6                       | 6                          | mV    |

| OCD1 Scale Accuracy                                 | OCD1 <sub>SCALERR</sub> |                                                                                                                                         | -16                        | 1                         | 16                         | %     |

| OCD2 Scale Accuracy                                 | OCD2 <sub>SCALERR</sub> |                                                                                                                                         | -14                        | 1                         | 14                         | %     |

| OCC Scale Accuracy                                  | OCC <sub>SCALERR</sub>  |                                                                                                                                         | -14                        | 1.2                       | 14                         | %     |

| CCD Acquirect                                       | 8CD                     | 22mV                                                                                                                                    | -20                        | 10                        | 40                         | %     |

| SCD Accuracy                                        | SCD <sub>ACC</sub>      | > 22mV                                                                                                                                  | -15                        | 1.5                       | 15                         | %     |

| Charge and Discharge Drivers                        |                         |                                                                                                                                         |                            |                           |                            |       |

| 0110 12000                                          |                         | $V_{REGSRC}$ = 25V with load resistance of 10M $\Omega$                                                                                 | 11.2                       | 12.5                      | 13.6                       | V     |

| CHG and DSG On                                      | $V_{FETON}$             | $V_{REGSRC}$ < 12V with load resistance of 10M $\Omega$                                                                                 |                            | V <sub>REGSRC</sub> - 0.9 |                            | V     |

|                                                     |                         | $V_{\text{REGSRC}}$ = 12V, CHG driving an equivalent load capacitance of 10nF, measured from 10% to 90% of $V_{\text{FETON}}$           |                            | 90                        | 120                        |       |

| CHG and DSG On Rise Time                            | t <sub>FET ON</sub>     | $V_{REGSRC}$ = 12V, DSG driving an equivalent load capacitance of 10nF, measured from 10% to 90% of $V_{FETON}$                         |                            | 120                       | 150                        | μs    |

|                                                     | . = 1_4.11              | $V_{REGSRC}$ < 12V, CHG driving an equivalent load capacitance of 10nF, measured from 10% to 90% of $V_{FETON}$                         |                            | 100                       | 140                        | ·     |

|                                                     |                         | $V_{\rm REGSRC}$ < 12V, DSG driving an equivalent load capacitance of 10nF, measured from 10% to 90% of $V_{\rm FETON}$                 |                            | 125                       | 160                        |       |

| DSG Pull-Down OFF Fall Time                         | $t_{DSG\_OFF}$          | DSG driving an equivalent load capacitance of 10nF, measured from 90% to 10%                                                            |                            | 68                        |                            | μs    |

| CHG Pull-Down OFF Fall Time                         | t <sub>CHG_OFF</sub>    | CHG driving an equivalent load capacitance of 10nF, mesured from 90% to 10%                                                             |                            | 2500                      |                            | μs    |

| CHG Pull-Down Off-Resistance to VSS                 | R <sub>CHG_OFF</sub>    | CHG disabled, CHG held at 12V                                                                                                           | 828                        | 990                       | 1150                       | kΩ    |

| DSG Pull-Down Off-Resistance to VSS                 | $R_{DSG\_OFF}$          | DSG disabled, DSG held at 12V                                                                                                           | 2.1                        | 2.7                       | 3.2                        | kΩ    |

| Load Detection Threshold                            | $V_{LOAD\_DETECT}$      |                                                                                                                                         | 400                        | 750                       | 1100                       | mV    |

| Filter Time                                         | t <sub>FILTER</sub>     | Load detection signal filter time                                                                                                       | 3                          |                           | 6                          | μs    |

| CHG Clamp Voltage                                   | $V_{CHG\_CLAMP}$        | If the CHG pin externally pulled high (through PACK-, if load applied), 500µA (MAX) sink current into CHG pin. With CHG_ON bit cleared. | 19                         | 20                        | 22                         | V     |

| ALERT Pin                                           |                         |                                                                                                                                         |                            |                           |                            |       |

| ALERT Output Voltage High                           | $V_{ALERT\_OH}$         | I <sub>OL</sub> = 1mA                                                                                                                   | V <sub>REGOUT</sub> × 0.75 |                           |                            | V     |

| ALERT Output Voltage Low                            | $V_{ALERT\_OL}$         | Unloaded                                                                                                                                |                            |                           | V <sub>REGOUT</sub> × 0.25 | V     |

|                                                     |                         | V <sub>REGOUT</sub> = 1.8V                                                                                                              |                            | 1                         |                            |       |

| ALERT Input High                                    | $V_{ALERT\_IH}$         | V <sub>REGOUT</sub> = 3.0V                                                                                                              |                            | 1.7                       |                            | V     |

|                                                     |                         | V <sub>REGOUT</sub> = 5.0V                                                                                                              |                            | 2.7                       |                            |       |

| ALERT Pin Weak Pull-Down Resistance when Driven Low | R <sub>ALERT_PD</sub>   | V <sub>REGOUT</sub> = 3.3V                                                                                                              | 1.6                        | 2.3                       | 3.2                        | МΩ    |

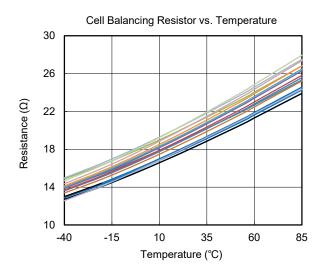

| Cell Balancing Driver                               |                         |                                                                                                                                         |                            |                           |                            |       |

| Internal Cell Balancing Driver Resistance           | R <sub>DSFET</sub>      | V <sub>CELL</sub> = 3.6V                                                                                                                | 5                          | 20                        | 40                         | Ω     |

| Cell Balancing Duty Cycle when<br>Enabled           | $X_{BAL}$               | Every cycle                                                                                                                             |                            | 86                        |                            | %     |

## **ELECTRICAL CHARACTERISTICS (continued)**

( $V_{BAT}$  = 48V,  $T_A$  = -40°C to +85°C, typical values are at  $T_A$  = +25°C unless otherwise noted.)

| PARAMETER                       | SYMBOL                    | OL CONDITIONS                                                                                                              |      | TYP   | MAX     | UNITS |

|---------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------|------|-------|---------|-------|

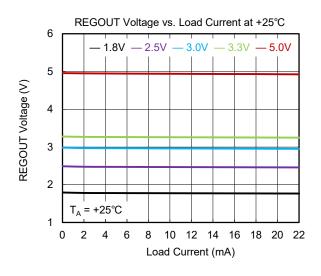

| External Regulator              |                           |                                                                                                                            |      |       |         |       |

|                                 |                           |                                                                                                                            | 1.3  | 1.8   | 1.9     |       |

|                                 |                           |                                                                                                                            | 2.2  | 2.5   | 2.6     |       |

| External LDO Voltage Options    | $V_{\text{EXTLDO}}$       | Nominal values, unloaded, across temp                                                                                      | 2.7  | 3.0   | 3.2     | V     |

|                                 |                           |                                                                                                                            | 2.9  | 3.3   | 3.3 3.5 |       |

|                                 |                           |                                                                                                                            | 4.5  | 5.0   | 5.2     |       |

| Line Regulation                 | V <sub>EXTLDO_LN</sub>    | REGSRC pin stepped from 6V to 25V, with 10mA load, in 100µs                                                                |      | 9.5   | 24      | mV    |

| Load Regulation                 | $V_{\text{EXTLDO\_LD}}$   | I <sub>REGOUT</sub> = 0mA to 10mA                                                                                          |      | -0.12 | 0.5     | %     |

| External LDO Current Limit      | I <sub>EXTLDO_LIMIT</sub> | V <sub>REGOUT</sub> = 0V                                                                                                   | 17   | 25.2  | 33      | mA    |

| Boot Detector                   |                           |                                                                                                                            |      |       |         |       |

| Boot Threshold Voltage          | $V_{\text{BOOT}}$         | Measured at TS1/WAKE pin with device in ship mode. Below MIN, the device does not boot up. Above MAX, the device boots up. | 1000 |       |         | mV    |

| Boot Threshold Application Time | t <sub>BOOT_MAX</sub>     | Measured at TS1/WAKE pin. Below MIN, the device does not boot up. Above MAX, the device boots up.                          | 1000 |       |         | μs    |

### NOTES:

- 1. Measured at each V<sub>BAT</sub>.

- 2. ADC values are measured when cell balancing is off.

- 3. Design simulation values for reference.

- 4. Values indicate nominal thresholds only. For minimum and maximum variation, apply OCOFFSET and OCSCALERR.

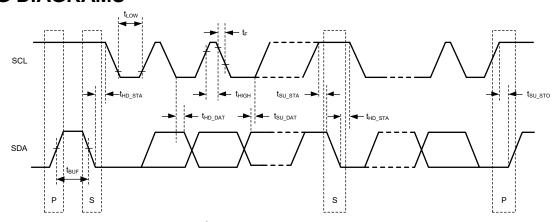

## **TIMING CHARACTERISTICS**

| PARAMETER                                                               | SYMBOL                | MIN                        | TYP | MAX                        | UNITS |

|-------------------------------------------------------------------------|-----------------------|----------------------------|-----|----------------------------|-------|

| Input Low Logic Threshold                                               | $V_{IL}$              |                            |     | V <sub>REGOUT</sub> × 0.25 | V     |

| Input High Logic Threshold                                              | $V_{\text{IH}}$       | V <sub>REGOUT</sub> × 0.75 |     |                            | V     |

| Output Low Logic Drive                                                  | $V_{OL}$              |                            |     | 0.2                        | V     |

| SCL, SDA Fall Time                                                      | t <sub>F</sub>        |                            |     | 0.4                        | μs    |

| SCL Pulse Width High                                                    | t <sub>HIGH</sub>     | 4                          |     |                            | μs    |

| SCL Pulse Width Low                                                     | t <sub>LOW</sub>      | 4.7                        |     |                            | μs    |

| Setup Time for START Condition                                          | t <sub>SU_STA</sub>   | 4.7                        |     |                            | μs    |

| START Condition Hold Time after which First Clock<br>Pulse is Generated | t <sub>HD_STA</sub>   | 4                          |     |                            | μs    |

| Data Setup Time                                                         | $t_{	extsf{SU\_DAT}}$ | 250                        |     |                            | ns    |

| Data Hold Time                                                          | $t_{\text{HD\_DAT}}$  | 0                          |     |                            | μs    |

| Setup Time for STOP Condition                                           | t <sub>su_sto</sub>   | 4                          |     |                            | μs    |

| Time the Bus Must be Free before New Transmission Can start             | t <sub>BUF</sub>      | 4.7                        |     |                            | μs    |

| Clock Low to Data Out Valid                                             | $t_{VD\_DAT}$         |                            |     | 900                        | ns    |

| Data Out Hold Time after Clock Low                                      | t <sub>HD_DAT</sub>   | 0                          |     |                            | ns    |

| Clock Frequency                                                         | f <sub>SCL</sub>      | 0                          |     | 100                        | kHz   |

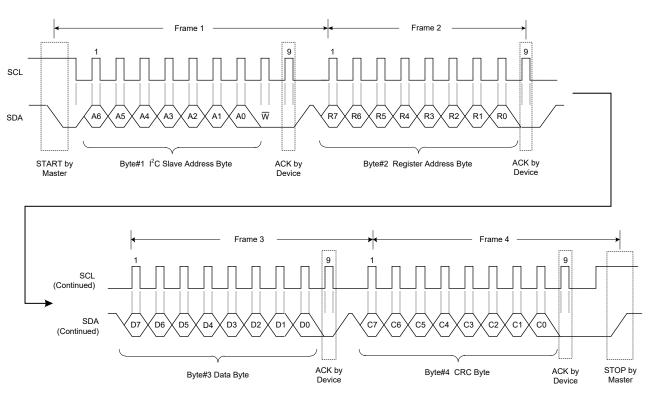

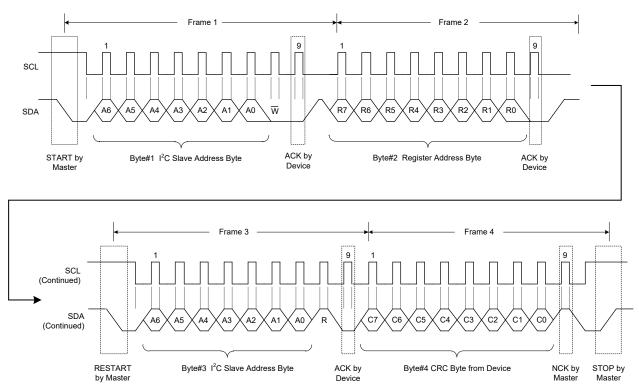

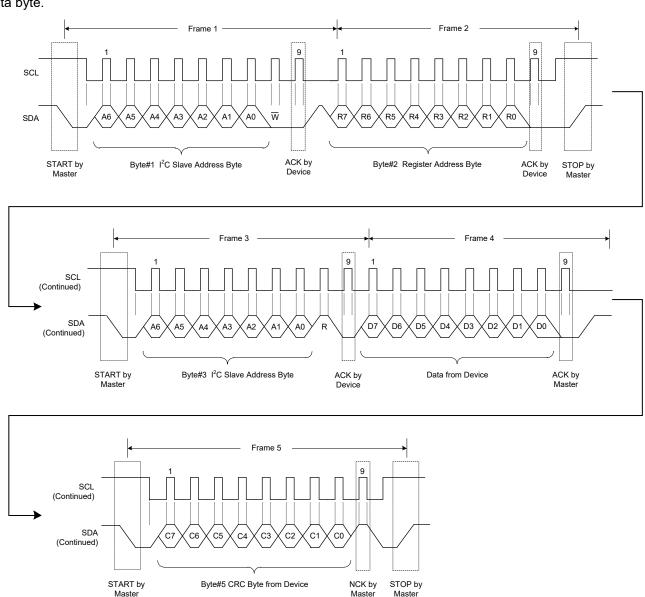

## **TIMING DIAGRAMS**

Figure 1. I<sup>2</sup>C Communications Interface Timing

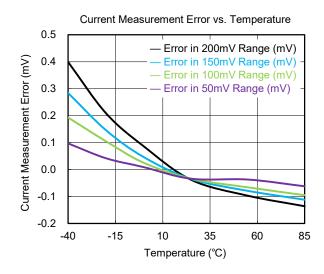

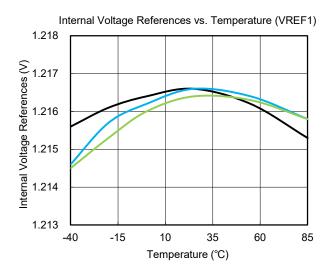

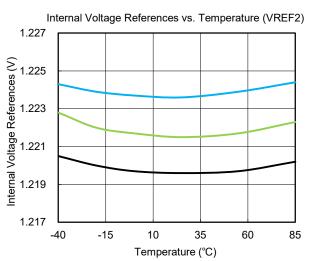

## TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = -40$ °C to +85°C, unless otherwise noted.

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_A = -40$ °C to +85°C, unless otherwise noted.

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_A = -40$ °C to +85°C, unless otherwise noted.

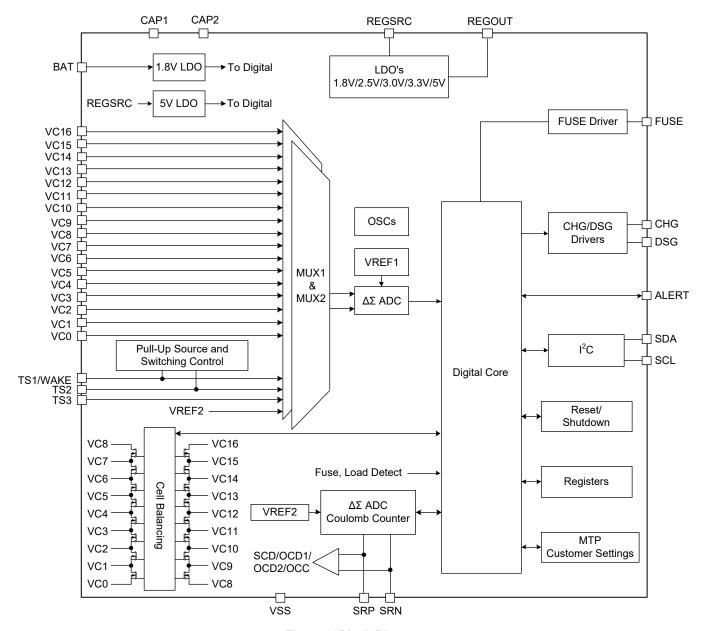

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. Block Diagram

### **DETAILED DESCRIPTION**

#### Overview

The SGM90116H is a multi-channel analog front end (AFE) IC targeting 3 to 16 series cells for applications such as LEV, UPS and power tools.

Two separate 16-bit ADCs provide accurate monitoring of voltage, current and temperature at both cell and pack level. The integrated post-ADC filters enable clean and stable readings to the host. Extensive protections such as over/under-voltage, over/under-current and over/under-temperature detections are readily available thanks to the precise sensing and monitoring. On-chip passive balancing up to 50mA is supported for each cell. Low-side drivers for charge/discharge FETs are also integrated to reduce BOM.

The device is programmable via on-chip I<sup>2</sup>C controller.

### **Measurement Subsystem**

The measurement subsystem enables the host to easily monitor cell voltages, temperatures, pack voltage, and pack current. All ADCs are trimmed by SGMICRO.

To ensure data completion a nd accuracy, the ADC and CC data are read using address auto-increment, which returns the complete value consisting of the high and low registers in the same transaction, without being interrupted or changed by other transactions.

**Table 1. Normal Mode**

| SETTLE[1:0]<br>Bits | Conversion<br>Time<br>(Per Channel) | Settle<br>Time | Frame<br>Time | Average |

|---------------------|-------------------------------------|----------------|---------------|---------|

| 0x00                | 11.72ms                             | 0.976ms        | 250ms         | 8       |

| 0x01                | 15.616ms                            | 4.883ms        | 332ms         | 8       |

| 0x02                | 15.616ms                            | 8.789ms        | 332ms         | 4       |

| 0x03                | 15.616ms                            | 11.712ms       | 332ms         | 1       |

In normal conversion mode, multi-time sample average scheme is adopted for each channel during a frame. A complete conversion frame with a total of 21 channels takes about 250ms or 332ms, depending on the different settling time.

Three thermistor voltages are updated every two frames at intervals of 500ms or 664ms. Specifically, during odd frame, thermistors 3 is measured, while during the even frame, thermistor 1 and 2 are updated.

The update of the three thermistor voltages occur the same as the normal cell voltage channels.

### **Voltage Measurement**

The SGM90116H uses a 16-bit ADC for measuring cell voltages and temperatures. This ADC measures all differential cell voltage, thermistors, die temperature, internal reference voltage, battery voltage and covers a nominal full-scale range of 0V to 6.55V with a least significant bit (LSB) value of 100µV/LSB.

To enable the ADC, set the VADC\_EN bit in the SYS\_CTRL1 register. This bit is auto-enabled in normal working mode, ensuring over-voltage (OV) and under-voltage (UV) protections are active.

### **Thermistor Temperature measurement**

The device can measure up to three NTC 103AT thermistors by applying a factory-trimmed internal  $10k\Omega$  pull-up resistance to an internal 1.8V nominal regulator. The results can be read from the TSx registers.

The thermistors impedance can be calculated based on the 16-bit ADC reading from the TS1, TS2, TS3 registers and  $10k\Omega$  internal pull-up resistance using the following formulas:

$$V_{TSX} = (ADC \text{ in Decimal}) \times 100 \mu V/LSB$$

(1)

$$R_{TS} = (10000 \times V_{TSX})/(1.8 - V_{TSX})$$

(2)

To convert the thermistor resistance to temperature value, please refer to the thermistor manufacturer's datasheet. When the TEMP\_SEL bit is set, TS1/WAKE stores the internal die temperature value.

If TS1, TS2 and TS3 are not used as thermistor inputs, the TSx pin should be connected to ground with a  $10k\Omega$  nominal resistor.

### Die Temperature measurement

The die temperature block produces a voltage which is proportional to the die temperature. This can reduce component count when pack thermistors are not used, and ensures the die power dissipation requirements are observed. The die temperature uses the same onboard 16-bit ADC that is used for measuring cell voltage.

To select internal die temperature measurement, set TEMP\_SEL bit to 0.

To convert a DIE TEMP reading into temperature value, refer to the equations below. For more precise temperature readings from DIE TEMP, store the DIE TEMP value at room temperature during production calibration.

The equations below shows how to use the 16-bit ADC readings in TS1/WAKE when TEMPSEL = 0 to calculate the internal die temperature.

$$V_{25} = 0.54 \text{ (nominal)}$$

(3)

$$V_{TS1} = (ADC \text{ in Decimal}) \times 100 \mu V/LSB$$

(4)

TEMP<sub>DIE</sub> =

$$25^{\circ}$$

C+ [(V<sub>TS1</sub> - V<sub>25</sub>)/0.00175] (5)

### **Stack Voltage Measurement (VC16 Pin)**

After digitization, each cell voltage is added up and the summation result is stored in the BAT registers. Use the BAT\_SEL bit to select either the direct stack voltage or the sum of 16 separate voltages. This sum is then divided by 16, resulting in a 16-bit value with a nominal LSB of 1.6mV. Due to direct stack voltage is measured by resistor divider connected to VC16 and the sum of 16 cells is measured by each cell, the final result has a little difference.

The following linear equation shows how to convert the 16-bit pack voltage ADC reading to an analog voltage.

$$V_{BAT}$$

= 16 × ADC(cell) × 100 $\mu$ V/LSB (6)

#### **Cell Balance**

The SGM90116H can support both internal and external passive cell balancing. The host controller decides the balancing algorithm. Internal cell balance drivers can balance up to 50mA per cell, while external options allow for higher currents.

To activate a cell balancing channel, set the corresponding bit in the CELL\_BAL1, CELL\_BAL2 or CELL\_BAL3 register.

While multiple cells are balanced simultaneously, avoid balancing adjacent cells concurrently. This can lead to exceeding their absolute maximum conditions and is also not recommended for external balancing implementations. When using internal balancing, care should be taken to avoid exceeding package power dissipation ratings.

The host controller must ensure that no two adjacent cells are balanced simultaneously.

During cell balancing, the protection logic remains active and will not miss any protection measures while cell balancing is enabled.

Balancing occupies approximately 86% of the frame-time (See Table 1) cycle during ADC cell voltage measurement.

### **Current Conversion**

The SGM90116H uses a low-side sense resistor to monitor pack current, which connects to the SRP and SRN pins via an external RC filter. Connect the filter so that a charging current will produce a positive voltage on SRP relative to SRN.

The device supports sense resistors of  $1m\Omega$  or less. The differential voltage between SRP and SRN is digitized by an integrated 16-bit sigma-delta ADC, which can digitize voltages over a  $\pm 200mV$  range.

The ADC uses multiple digital filters to optimize the measurement of instantaneous and integrated current. Two separate hardware digital filters, coulomb counting (CC) filter and current-to-voltage conversion (CUR) filter are used to get the digitized current value.

To enable one-shot mode, set CC\_EN bit to 0 and CC\_ONESHOT bit to 1. In one-shot mode, the CC performs a single 250ms reading and sets the CC\_READY bit at the end of each reading if CC\_SRC bit is set to 0. This mode is designed for non-gauging applications where the host's primary intention is to check the pack current.

The CUR filter generates a 16-bit current measurement used for current reporting. The CUR Filter output the current much faster than CC Filter. It will output the current results every 11.72/15.616ms in normal mode. Due to this feature, the current measurement can be synchronously measured with each cell voltage channel. If CC\_SRC bit is set to 1, the CC\_READY bit will represents CUR filter measurement is ready and the ALERT pin is triggered by CUR filter ready signal. CUR filter is enabled by IADC EN bit.

The CC and CUR has a full-scale range of  $\pm 300$  mV, with a recommended maximum input range of  $\pm 200$  mV, resulting in a least significant bit (LSB) of approximately  $9.3 \mu$ V.

The equation below shows how to convert the 16-bit CC/CUR reading into an analog voltage when no board-level calibration has been performed:

CC Reading (

$$\mu$$

V) = (16-bit 2's Complement Value) × 9.3 $\mu$ V/LSB (7)

When both IADC\_EN bit and CC\_EN bit are set to 0, the internal 16-bit sigma-delta ADC is disabled and ONE\_SHOT is not triggered.

### Synchronized Voltage and Current Measurement

During normal operation, when cell voltages are sequentially digitized using a single multiplexed ADC, the current is continuously digitized by the dedicated coulomb counter ADC. This current measurement is synchronized with each cell voltage measurement, enabling its use for individual cell impedance analysis. Periodic current measurements can be read out through digital communication interface. Additionally, measurements taken in sync with specific cell voltage readings are stored together with their associated voltage measurements for separate readout.

### **Protection Subsystem**

Integrated hardware protections are provided to enhance safety, acting as supplements to the standard protection features within the host controller firmware. They should not be the sole means of battery pack protection. They offer additional use for FMEA purpose when the host microcontroller may not respond to any of these below protection situations.

Over-current in discharge (OCD1/2), short-circuit in discharge (SCD), and over-current in charging (OCC), are implemented using analog comparators. These continuously monitor the voltage across (SRP - SRN) while the device is in normal operation mode. If a voltage exceeding the programmed threshold is detected for a programmable delay, the alert will be triggered if the protection enable bit is set, interrupting the host microcontroller.

Cell over-voltage (COV), cell under-voltage (CUV), over-temperature in charging (OTC), temperature in charging (UTC), over-temperature in discharging (OTD), under-temperature in discharging (UTD), die over-temperature (OTINT), and die under-temperature (UTINT) are digital comparators based on ADC measurements and corresponding thresholds. When a measured result exceeds the threshold, a trigger flag is generated, and an alert signal will be driven high if the protection enable bit is set. Users can configure corresponding bit in PROTEN register to enable the OTC/UTC/OTD/UTD/OTINT/ UTINT.

#### OCD1

Over-current in discharge protection (OCD1) uses a dedicated analog comparator to monitor voltage across SRN and SRP pins. When this voltage exceeds the programmable delay threshold, the OCD1 protection will be activated. The threshold can be set from 8mV to 50mV with 3mV per step (RSNS = 0) or from 17mV to 100mV with 6mV per step (RSNS = 1). The delay can be set to 8ms, 20ms, 40ms, 80ms, 160ms, 320ms, 640ms, or 1280ms. These settings are configurable through the PROTECT2 register.

If OCD1 protection is detected, the DSG FET will be automatically turned off. To turn on the DSG FET, users must clear the OCD1 flag, and set DSG\_ON bit to 1. If the OCD1 flag is not cleared, DSG\_ON bit will remain at 0.

### OCD2

Over-current in discharge protection (OCD2) uses a dedicated analog comparator to monitor voltage across SRN and SRP pins. When this voltage exceeds the programmable delay threshold, the OCD2 protection will be activated. The threshold can be set from 4mV to 200mV with 2mV per step. The delay can be set from 3ms to 381ms with 2.93ms per step. These settings are configurable through the OCD2\_THD and OCD2\_DLY registers.

OCD2 function is enabled when OCD\_THD[3:0] bits are not set to 0x0 and OCD2\_EN bit is set to 1, the alert function and DSG control will be enabled. Otherwise, they will be ignored.

OCD2\_DLY cannot be configured to 0. Otherwise, the abnormal flag will be triggered.

It is recommended to configure OCD2\_DLY and OCD2\_THD registers before OCD2 function is enabled.

If OCD2 protection is detected, the DSG FET will be automatically turned off. To turn on the DSG FET, users must clear the OCD2 flag, and set DSG\_ON bit to 1. If the OCD2 flag is not cleared, DSG\_ON bit will remain at 0.

#### SCD

Short-circuit discharge (SCD) protection uses a dedicated analog comparator to monitor voltage across SRN and SRP pins. When this voltage exceeds the programmable delay threshold, the SCD protection will be activated. The threshold can be set from 22mV to 100mV with 11mV per step (RSNS = 0), or from 44mV to 200mV with 22mV per step (RSNS = 1). Additionally, the delay can be set to  $80\mu s$ ,  $105\mu s$ ,  $200\mu s$  or  $400\mu s$ . These settings are configurable through the PROTECT1 register.

If SCD protection is detected, the DSG FET will be automatically turned off. To turn on the DSG FET, users must clear the SCD flag and set DSG\_ON bit to 1. If the SCD flag is not cleared, DSG\_ON bit will remain at 0.

#### OCC

Over-current charge protection (OCC) uses a dedicated analog comparator to monitor the voltage across SRN and SRP pins. When this voltage exceeds the programmable delay threshold, the OCC protection will be activated. The threshold can be set from 4mV to 124mV with 2mV per step. And the delay can be set from 3ms to 381ms with 2.93ms per step. OCC\_THD

and OCC\_DLY registers are used to configure these parameters.

OCC function is enabled when OCC\_THD[5:0] bits are not set to 0x0 and OCC\_EN bit is set to 1, the alert function and CHG control will be enabled. Otherwise, they will be ignored.

If OCC protection is detected, the CHG FET will be automatically turned off. To turn on the CHG FET, users must clear the OCC flag, and set CHG\_ON bit to 1. If the OCC flag is not cleared, CHG\_ON bit will remain at 0

#### COV

Cell over-voltage protection (COV) is digitally managed by comparing cell voltage readings against the 8-bit programmed threshold stored in the OV TRIP register.

The OV threshold is direct mapping of 8 bits of the 16-bit ADC reading, with the upper 2 MSB preset to 10 and lower 6LSB preset to 100000. This corresponds to the 10-XXXX-XXXX-100000 OV trip level. The programmable OV threshold ranges approximately from 3.28V to 4.91V, but the exact value may change due to the linear equation used for ADC value mapping.

The COV triggers an alert signal if the over-voltage condition persists for a programmable delay, selectable as 1s, 2s, 4s or 8s through the DLY[1:0] bits of PROTECT3 register.

To calculate the accurate OV\_TRIP register value, use the following steps:

- Determine the desired OV

- Calculate the full 16-bit ADC value required to meet the desired OV trip threshold

- Remove the upper 2 MSB and Lower 6LSB from the full 16-bit value, retaining only the remaining 8 bits.

Achieve this by shifting the OV\_TRIP\_FULL binary value 6bits to the right and removing the 2MSB.

- Write OV TRIP to the corresponding register.

OV protection is enabled when VADC is enabled. Make sure that the VADC\_EN bit is set to 1 when OV protections are needed.

If OV protection is detected, the CHG FET will be automatically turned off. To turn on the CHG FET, users must clear the COV flag, and set CHG\_ON bit to 1. If the COV flag is not cleared, CHG\_ON bit will remain at 0.

The cell that triggered the COV flag can be checked by the SYS STAT6 and SYS STAT6 registers.

### CUV

Cell under-voltage protection (CUV) is digitally managed by comparing cell voltage readings against an 8-bit programmed threshold in the UV\_TRIP register.

The UV threshold is a direct mapping of 8 bits of the 16-bit ADC reading, with upper 2 MSB are set to 01, and lower 6LSB are set to 000000. This corresponds to the 01-XXXX-XXXX-000000 UV trip level. The programmable UV threshold ranges approximately from 1.64V to 3.27V, while the exact value may change due to the linear equation used for ADC value mapping.

The CUV triggers an alert signal if the under-voltage condition persists for a programmable delay, selectable as 1s, 4s, 8s or 16s through the UV\_DLY[1:0] bits of PROTECT3 register.

To short the cell pins when the cells are not required,  $UV_{MINQUAL}$  is preset in the factory, with a default value of 0x1380, corresponding to 499mV.

- Determine the desired UV

- Calculate the full 16-bit ADC value required to meet the desired UV trip threshold

- Remove the upper 2 MSB and Lower 6LSB from the full 16-bit value, retaining only the remaining 8 bits.

Achieve this by shifting the UV\_TRIP\_FULL binary value 6 bits to the right and removing the 2 MSB.

- Write UV\_TRIP to the corresponding register.

UV protection is enabled when VADC is enabled. Make sure that the VADC\_EN bit is set to 1 when UV protection is needed.

If UV protection is detected, the DSG FET will be automatically turned off. To turn on the DSG FET, users must clear the CUV flag, and set DSG\_ON bit to 1. If the CUV flag is not cleared, DSG\_ON bit will remain at 0.

The cell that triggered the CUV flag can be checked by the SYS CTRL4 and SYS CTRL5 registers.

#### **OTC**

Over-temperature charge protection (OTC) is initiated by comparing the measured die temperature voltage with a threshold while in charge mode. If the voltage on any of the TS1/TS2/TS3 pins exceeds the threshold within a programmable delay, the OTC protection will be triggered. The threshold can be set by OTC\_THD\_HI/OTC\_THD\_LO registers, while the OTC\_DLY is used to set the programmable delay.

OTC threshold high 8 bits are stored in a temporary register after OTC\_THD\_HI register is configured, and the threshold value is updated after OTC\_THD\_LO register is configured. OTC\_DLY cannot be configured to 0 or abnormal flag will be triggered. It is recommended to configure OTC\_DLY and OTC threshold register before OTC function is enabled.

Default protection thresholds and delays are loaded from the NVM preset area during chip regular power-up.

OTC function is enabled when [OTC\_THD] bit is not set to 0x0 and [OTC\_EN] bit is set to 1. The alert function and CHG control will be enabled. Otherwise, they will be ignored.

If OTC protection is detected, the CHG FET will be automatically turned off. To turn on the CHG FET, users must clear the OTC flag, and set CHG\_ON bit to 1. If the OTC flag is not cleared, CHG\_ON bit will remain at 0

#### UTC

Under-temperature charge protection (UTC) is initiated by comparing the measured die temperature voltage with a threshold while in charge mode. If the voltage on any of the TS1/TS2/TS3 pins is lower than the threshold within a programmable delay, the UTC protection will be triggered. The threshold can be set by UTC\_THD\_HI/UTC\_THD\_LO register, while the UTC\_DLY register is used to set the programmable delay.

UTC threshold high 8 bits are stored in a temporary register after UTC\_THD\_HI register is configured, and the threshold value is updated after UTC\_THD\_LO register is configured. UTC\_DLY cannot be configured to 0 or abnormal flag will be triggered. It is recommended to configure UTC\_DLY and UTC threshold registers before UTC function is enabled.

Default protection thresholds and delays are loaded from the NVM preset area during chip regular power-up.

UTC function is enabled when UTC\_THD bits are not set to 0x0 and UTC\_EN bit is set to 1, the alert function and CHG control will be enabled. Otherwise, they will be ignored.

If UTC protection is detected, the CHG FET will be automatically turned off. To turn on the CHG FET, users must clear the UTC flag, and set CHG\_ON bit to 1. If UTC flag is not cleared, CHG ON bit will remain at 0.

#### **OTD**

Over-temperature discharge protection (OTD) is initiated by comparing the measured die temperature voltage with a threshold while in discharge mode. If the voltage on any of the TS1/TS2/TS3 pins exceeds the threshold within a programmable delay, the OTD protection will be triggered. The threshold can be set by OTD\_THD\_HI/OTD\_THD\_LO register, while the OTD\_DLY register is used to set the programmable delay.

OTD threshold high 8 bits are stored in a temporary register after OTD\_THD\_HI configured, and the threshold value is updated after OTD\_THD\_LO register is configured. OTD\_DLY cannot be configured to 0 or abnormal flag will be triggered. It is recommended to configure OTD\_DLY and OTD threshold register before OTD function is enabled.

Default protection thresholds and delays are loaded from the NVM preset area during chip regular power-up.

OTD function is enabled when OTD\_THD[15:0] bits are not set to 0x0 and OTD\_EN bit is set to 1, the alert function and DSG control will be enabled. Otherwise, they will be ignored.

If OTD protection is detected, the DSG FET will be automatically turned off. To turn on the DSG FET, users must clear the OTD flag, and set DSG\_ON bit to 1. If OTD flag is not cleared, DSG\_ON bit will remain at 0.

#### UTD

Under-temperature discharge protection (UTD) is initiated by comparing the measured die temperature voltage with a threshold while in discharge mode. If the voltage on any of the TS1/TS2/TS3 pins is lower than the threshold within a programmable delay, the UTD protection will be triggered. The threshold can be set by UTD\_THD\_HI/UTD\_THD\_LO register, while the

UTD\_DLY register is used to set the programmable delay.

UTD threshold high 8 bits are stored in a temporary register after UTD\_THD\_HI register is configured, and the threshold value is updated after UTD\_THD\_LO register is configured. UTD\_DLY cannot be configured to 0 or abnormal flag will be triggered. It is recommended to configure UTD\_DLY and UTD threshold register before UTD function is enabled.

Default protection thresholds and delays are loaded from the NVM preset area during chip regular power-up.

UTD function is enabled when UTD\_THD[15:0] bits are not set to 0x0 and UTD\_EN bit is set to 1, the alert function and DSG control will be enabled. Otherwise, they will be ignored.

If UTD protection is detected, the DSG FET will be automatically turned off. To turn on the DSG FET, users must clear the UTD flag, and set DSG\_ON bit to 1. If UTD flag is not cleared, DSG\_ON bit will remain at 0.

#### **OTINT**

Die temperature over-temperature protection is initiated by comparing the measured die temperature voltage with threshold. If the voltage exceeds the threshold within a programmable delay, the OTINT protection will be triggered. The threshold can be set by OTINT\_THD\_HI/OTINT\_THD\_LO register, while the OTINT\_DLY register is used to set the programmable delay.

OTINT threshold high 8 bits are stored in a temporary register after OTINT\_THD\_HI configured, and the threshold value is updated after OTINT\_THD\_LO register is configured. OTINT\_DLY cannot be configured to 0 or abnormal flag will be triggered. It is recommended to configure OTINT\_DLY and OTINT threshold register before OTINT function is enabled.

Default protection thresholds and delays are loaded from the NVM preset area during chip regular power-up.

OTINT function is enabled when OTINT\_THD[15:0] bits are not set to 0x0 and OTINT\_EN bit is set to 1, the alert function and DSG/CHG control will be enabled; otherwise, they will be ignored.

If OTINT protection is detected, the DSG/CHG FET will be automatically turned off. To turn on the DSG/CHG FET, users must clear the OTINT flag, and set DSG\_ON/CHG\_ON bit to 1. If OTINT flag is not cleared, DSG\_ON/CHG\_ON bit will remain at 0.

#### **UTINT**

Die temperature under-temperature protection is initiated by comparing the measured die temperature voltage with threshold. If the voltage is lower than the threshold within a programmable delay, the UTINT protection will be triggered. The threshold can be set by UTINT\_THD\_HI/UTINT\_THD\_LO register, while the UTINT\_DLY register is used to set the programmable delay.

UTINT threshold high 8 bits are stored in a temporary register after UTINT\_THD\_HI configured, and the threshold value is updated after UTINT\_THD\_LO register is configured. UTINT\_DLY cannot be configured to 0 or abnormal flag will be triggered. It is recommended to configure UTINT\_DLY and UTINT threshold register before UTINT function is enabled.

Default protection thresholds and delays are loaded from the NVM preset area during chip regular power-up.

UTINT function is enabled when UTINT\_THD[15:0] bits are not set to 0x0 and UTINT\_EN bit is set to 1, the alert function and DSG/CHG control will be enabled. Otherwise, they will be ignored.