### SGM6620/SGM6620A 25V, 20A Synchronous Boost Converter with Stackable Multi-Phase Function

### **GENERAL DESCRIPTION**

The SGM6620 family is a 20A valley switch current limit synchronous Boost converter designed for high power applications. The device integrates a  $9.8 m\Omega$  (TYP) high-side MOSFET to maximize the efficiency and reduce overall solution size for portable applications. To further maximize the power density, the SGM6620 family supports daisy chain operation.

The device supports a wide input voltage range from 2.05V to 23V, which is suitable for various input source such as single-cell or multi-cell Lithium batteries, or USB PD3.0 input voltage range up to 20V. The SGM6620 family supports a wide programmable output voltage range from 4.5V to 25V.

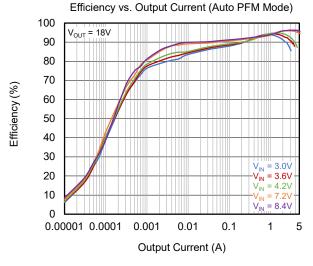

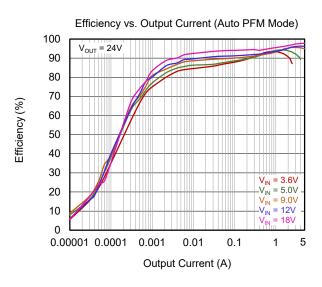

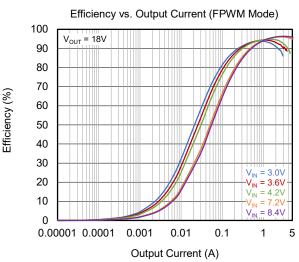

The SGM6620 family uses adaptive constant on-time valley current control topology to regulate the output voltage. The device offers operation mode selection via the MODE pin. Configuring to auto PFM mode, the device consumes minimal current at light load, and automatically switches to pulse width modulation (PWM) mode in moderate to heavy load condition. Configuring to forced PWM (FPWM) mode, the device operates in PWM mode across the entire load range to maintain consistent output voltage ripple for noise sensitive applications. The switching frequency in the PWM mode is 290kHz (TYP) for SGM6620 family. The SGM6620A offers light load ultrasonic mode to clamp the PFM frequency above 30kHz (TYP). The SGM6620 family offers the flexibility to select the main low-side power FET. The device integrates an internal gate driver with 500mA sourcing current and 1A sinking current capability.

The device also integrates various protection features, such as output over-voltage protection (OVP), cycle-by-cycle over-current protection (OCP), and thermal shutdown.

The SGM6620 family is available in a Green TQFN-2.5×3-14AL package.

### **FEATURES**

- Wide Input Voltage Range: 2.05V to 23V

- Wide Output Voltage Range: 4.5V to 25V

- 2.35V Minimum Input Voltage for Start-up

- 10A to 20A (TYP) Programmable Valley Current Limit

- Device Variant:

- SGM6620: 290kHz (TYP) Switching Frequency

- SGM6620A: 30kHz (TYP) Switching Frequency with Ultrasonic Mode

- 9.8mΩ (TYP) Integrated High-side FET

- Stackable Multi-Phase for High Output Current

- Synchronize to External Clock

- Precise EN/UVLO Threshold

- External Loop Compensation

- Protection Features:

- Output Over-Voltage Protection

- Cycle-by-Cycle Over-Current Protection

- Thermal Shutdown

- Available in a Green TQFN-2.5×3-14AL Package

### **APPLICATIONS**

USB Type-C Power Supply Smart Speakers

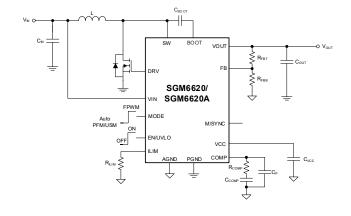

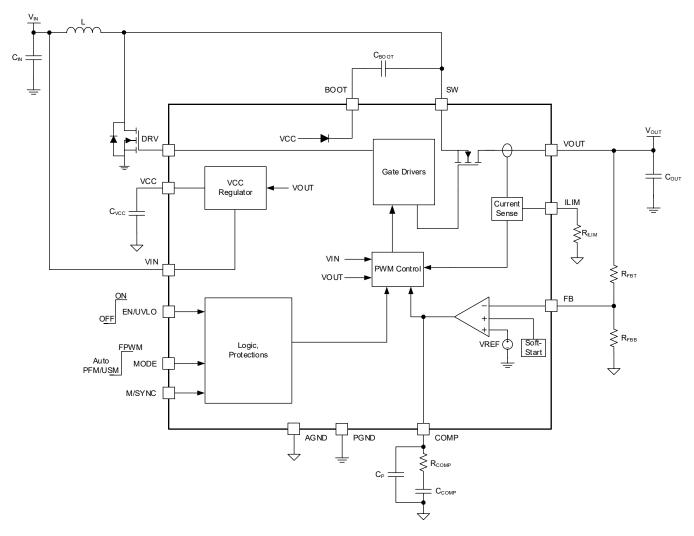

### SIMPLIFIED SCHEMATIC

Figure 1. Simplified Schematic

### PACKAGE/ORDERING INFORMATION

| MODEL    | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ERATURE ORDERING NUMBER |                        | PACKING<br>OPTION   |

|----------|------------------------|-----------------------------------|-------------------------|------------------------|---------------------|

| SGM6620  | TQFN-2.5×3-14AL        | -40°C to +125°C                   | SGM6620XTWP14G/TR       | 6620<br>TWP14<br>XXXXX | Tape and Reel, 5000 |

| SGM6620A | TQFN-2.5×3-14AL        | -40°C to +125°C                   | SGM6620AXTWP14G/TR      | 1WJ<br>TWP14<br>XXXXX  | Tape and Reel, 5000 |

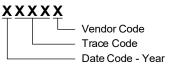

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

| ADOULD IE MANIMOM NATHY           | <b>-</b>                       |

|-----------------------------------|--------------------------------|

| VIN                               | 0.3V to 30V                    |

| EN/UVLO                           | 0.3V to 27V                    |

| SW, VOUT                          | 0.3V to 32V                    |

| BOOTV <sub>SW</sub>               | - 0.3V to $V_{\text{SW}}$ + 6V |

| M/SYNC, MODE, VCC, COMP, FB, DRV, | ILIM0.3V to 6V                 |

| Package Thermal Resistance        |                                |

| TQFN-2.5×3-14AL, $\theta_{JA}$    | 56.1°C/W                       |

| TQFN-2.5×3-14AL, θ <sub>JB</sub>  | 5.6°C/W                        |

| TQFN-2.5×3-14AL, θ <sub>JC</sub>  | 39.7°C/W                       |

| Junction Temperature              | +150°C                         |

| Storage Temperature Range         | 65°C to +150°C                 |

| Lead Temperature (Soldering, 10s) | +260°C                         |

| ESD Susceptibility (1) (2)        |                                |

| HBM                               | ±4000V                         |

| CDM                               | ±1000V                         |

|                                   |                                |

#### NOTES:

- 1. For human body model (HBM), all pins comply with ANSI/ESDA/JEDEC JS-001 specifications.

- 2. For charged device model (CDM), all pins comply with ANSI/ESDA/JEDEC JS-002 specifications.

#### RECOMMENDED OPERATING CONDITIONS

| Input Voltage Range, V <sub>IN</sub> 2.05V to 23V       |

|---------------------------------------------------------|

| Output Voltage Range, V <sub>OUT</sub> 4.5V to 25V      |

| Effective Inductance Range, L 1μH to 4.7μH, 2.2μH (TYP) |

| Effective Input Capacitance Range, C <sub>IN</sub>      |

| 4.7µF to 22µF (TYP)                                     |

| Effective Output Capacitance Range, C <sub>OUT</sub>    |

| 10µF to 1000µF, 100µF (TYP)                             |

| Operating Junction Temperature Range40°C to +125°C      |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

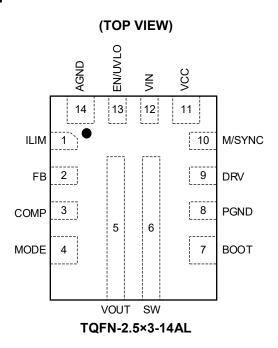

### **PIN CONFIGURATION**

### **PIN DESCRIPTION**

| PIN | NAME    | TYPE | FUNCTION                                                                                                                                                                                                                                                                                   |

|-----|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | ILIM    | I    | Inductor Valley Current Limit Setting Pin. Connect an external resistor between this pin and the AGND pin.                                                                                                                                                                                 |

| 2   | FB      | I    | Voltage Feedback Pin. Use a resistor divider to set the desired output voltage.                                                                                                                                                                                                            |

| 3   | COMP    | 0    | Output of the Internal Trans-Conductance Error Amplifier. An external RC network is connected to this pin to optimize the loop stability and response time.                                                                                                                                |

| 4   | MODE    | 1    | Mode Selection Pin.  MODE = high, forced PWM.  MODE = low, auto PFM, ultrasonic mode (SGM6620A), this pin must not leave floating.                                                                                                                                                         |

| 5   | VOUT    | Р    | Boost Converter Output. VOUT pin is connected to the drain of the high-side MOSFET.                                                                                                                                                                                                        |

| 6   | SW      | Р    | Switch Node Pin. Connect to the drain of external low-side MOSFET and the source of the internal high-side MOSFET.                                                                                                                                                                         |

| 7   | воот    | 0    | Power Supply for the High-side MOSFET Gate Driver. A ceramic capacitor with a capacitance ranging from $0.1\mu F$ to $1\mu F$ must be connected between the BOOT pin and the SW pin.                                                                                                       |

| 8   | PGND    | G    | Power Ground. Ground of low-side MOSFET.                                                                                                                                                                                                                                                   |

| 9   | DRV     | 0    | Driver Pin. Gate driver output for low-side MOSFET.                                                                                                                                                                                                                                        |

| 10  | M/SYNC  | I    | Internal or External Clock. When this pin is grounded, the device will operate at the switching frequency set internally. The switching frequency of the device is forced to set to the frequency of the external clock, when an effective clock signal is applied to this pin.            |

| 11  | VCC     | 0    | Output of the Internal Regulator. Connect a ceramic capacitor (> 2.2µF) between this pin and ground.                                                                                                                                                                                       |

| 12  | VIN     | Р    | Power Supply Pin.                                                                                                                                                                                                                                                                          |

| 13  | EN/UVLO | I    | Enable Input and Under-Voltage Lockout Pin. When sets to logic high, the device is enabled. When sets to logic low, the device is disabled and turns into shutdown mode. Connecting this pin to VIN through a resistor divider can program the start-up and shutdown levels of the device. |

| 14  | AGND    | G    | Analog Ground.                                                                                                                                                                                                                                                                             |

NOTE: I = input, O = output, P = power, G = ground.

### **ELECTRICAL CHARACTERISTICS**

$(T_J = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, V_{IN} = 3.6\text{V} \text{ and } V_{OUT} = 24\text{V}. \text{ All typical values are measured at } T_J = +25^{\circ}\text{C}, \text{ unless otherwise noted.})$

| PARAMETER                                       | SYMBOL                | CONDITIONS                                                                                                                         |                                                                   | MIN   | TYP  | MAX   | UNITS |

|-------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------|------|-------|-------|

| Power Supply                                    | •                     |                                                                                                                                    |                                                                   |       |      |       |       |

| Input Voltage Range                             | V <sub>IN</sub>       |                                                                                                                                    |                                                                   | 2.05  |      | 23    | V     |

| VIN UVLO Threshold                              | V                     | V <sub>IN</sub> rising                                                                                                             |                                                                   |       | 2.2  | 2.35  | V     |

| VIN OVLO Trileshold                             | $V_{IN\_UVLO}$        | V <sub>IN</sub> falling                                                                                                            |                                                                   |       | 1.9  | 2.05  | V     |

| VIN UVLO Hysteresis                             | V <sub>IN_HYS</sub>   |                                                                                                                                    |                                                                   |       | 0.3  |       | V     |

| Output Voltage Range                            | V <sub>OUT</sub>      |                                                                                                                                    |                                                                   | 4.5   |      | 25    | V     |

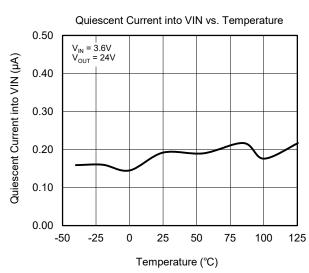

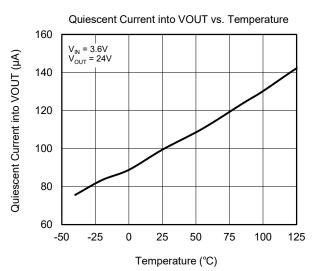

| 0 : 10 1                                        |                       | $T_J = -40^{\circ}C \text{ to } +85^{\circ}C,$                                                                                     | VIN Pin                                                           |       | 0.2  | 2.1   |       |

| Quiescent Current                               | lα                    | EN = high, no switching,<br>$2.35V < V_{IN} < 23V, V_{OUT} > 1.1V_{IN}$                                                            | VOUT Pin                                                          |       | 100  | 180   | μA    |

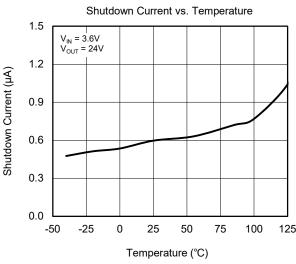

| Shutdown Current into VIN Pin                   | I <sub>SD</sub>       | T <sub>J</sub> = -40°C to +85°C,<br>EN = low, no switching, 2.35V < V <sub>IN</sub> < 23V                                          |                                                                   |       | 0.6  | 8     | μА    |

| VCC Regulated Voltage                           | V <sub>CC</sub>       | $I_{VCC} = 30 \text{mA}, V_{IN} = 6 \text{V}, V_{OUT} = 20 \text{V}$                                                               | <sub>C</sub> = 30mA, V <sub>IN</sub> = 6V, V <sub>OUT</sub> = 20V |       | 5    |       | V     |

| VCC UVLO Threshold                              | V                     | V <sub>CC</sub> rising                                                                                                             | <sub>C</sub> rising                                               |       | 1.95 |       | V     |

| VCC OVEO Tillesiloid                            | V <sub>CC_UVLO</sub>  | V <sub>CC</sub> falling                                                                                                            | afalling                                                          |       |      |       | V     |

| EN/UVLO                                         |                       |                                                                                                                                    |                                                                   |       |      |       |       |

| EN Logic High Threshold                         | $V_{EN_{-}H}$         | V <sub>CC</sub> = 5.0V                                                                                                             | V <sub>CC</sub> = 5.0V                                            |       |      |       | V     |

| EN Logic Low Threshold (Falling)                | $V_{EN\_L}$           | V <sub>CC</sub> = 5.0V                                                                                                             | V <sub>CC</sub> = 5.0V                                            |       |      |       | V     |

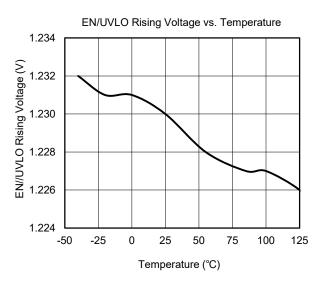

| UVLO Rising Threshold at the EN/UVLO Pin        | V <sub>UVLO</sub>     | V <sub>CC</sub> = 5.0V                                                                                                             |                                                                   |       | 1.23 | 1.29  | V     |

| Sourcing Current at the EN/UVLO Pin             | I <sub>UVLO_HYS</sub> | V <sub>EN/UVLO</sub> = 1.3V                                                                                                        |                                                                   |       | 5.1  |       | μA    |

| Output                                          |                       |                                                                                                                                    |                                                                   |       |      |       |       |

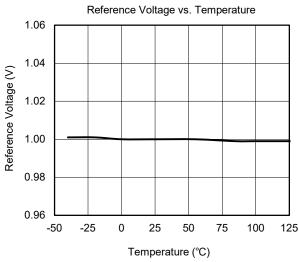

| Reference Voltage at the FB Pin                 | $V_{REF}$             | PWM mode                                                                                                                           |                                                                   | 0.985 | 1.0  | 1.015 | V     |

| Output Over-Voltage Protection<br>Threshold     | V <sub>OVP</sub>      | V <sub>OVP</sub> rising                                                                                                            |                                                                   | 25.3  | 26.5 | 27.7  | V     |

| Output Over-Voltage Protection<br>Hysteresis    | V <sub>OVP_HYS</sub>  |                                                                                                                                    |                                                                   |       | 1    |       | V     |

| Leakage Current into FB Pin                     | I <sub>FB_LKG</sub>   |                                                                                                                                    |                                                                   |       |      | 50    | nA    |

| Shutdown Current into VOUT Pin                  | I <sub>OUT_SD</sub>   | $T_J = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C},$ IC disabled, $V_{\text{OUT}} = 2.35\text{V to } 25\text{V}, \text{V}$ | / <sub>IN</sub> = 0V                                              |       | 7.6  | 12.7  | μΑ    |

| Power Switch                                    | •                     | ,                                                                                                                                  |                                                                   |       | •    | •     | •     |

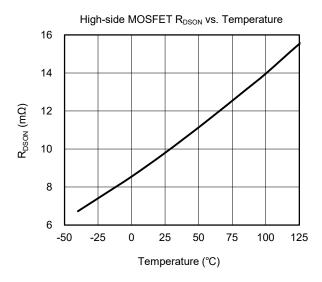

| High-side MOSFET On-Resistance                  | R <sub>DSON</sub>     | V <sub>CC</sub> = 5.0V                                                                                                             |                                                                   |       | 9.8  |       | mΩ    |

| Switching Frequency                             | f <sub>SW</sub>       | SGM6620 PWM mode,<br>V <sub>IN</sub> = 3.6V, V <sub>OUT</sub> = 18V                                                                |                                                                   |       | 290  |       | kHz   |

| Ultrasonic Mode Switching Frequency             | f <sub>USM</sub>      | SGM6620A                                                                                                                           |                                                                   |       | 30   |       | kHz   |

| Minimum Off-Time in Boost Mode                  | t <sub>OFF_MIN</sub>  |                                                                                                                                    |                                                                   |       | 170  |       | ns    |

| Minimum On-Time in Boost Mode                   | t <sub>ON_MIN</sub>   |                                                                                                                                    |                                                                   |       | 180  |       | ns    |

| Low-side Gate off to High-side Gate on Deadtime | t <sub>DLH</sub>      |                                                                                                                                    |                                                                   |       | 30   |       | ns    |

| High-side Gate off to Low-side Gate on Deadtime | t <sub>DHL</sub>      |                                                                                                                                    |                                                                   |       | 11   |       | ns    |

| Valley Current Limit                            | I <sub>LIM</sub>      | $R_{ILIM} = 20k\Omega$ , auto PFM mode                                                                                             |                                                                   | 17    | 20   | 23.5  | Α     |

### SGM6620/SGM6620A

### **ELECTRICAL CHARACTERISTICS (continued)**

$(T_J = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, V_{IN} = 3.6\text{V} \text{ and } V_{OUT} = 24\text{V}. \text{ All typical values are measured at } T_J = +25^{\circ}\text{C}, \text{ unless otherwise noted.})$

| • •                                                                              |                       | * *                                                                                |     |     |     | ,     |

|----------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------|-----|-----|-----|-------|

| PARAMETER                                                                        | SYMBOL                | CONDITIONS                                                                         | MIN | TYP | MAX | UNITS |

| Error Amplifier                                                                  |                       |                                                                                    |     |     |     |       |

| Sink Current into COMP Pin                                                       | I <sub>SINK</sub>     | $V_{FB} = V_{REF} + 400 \text{mV}, V_{COMP} = 1.5 \text{V}, V_{CC} = 5.0 \text{V}$ |     | 20  |     | μA    |

| Source Current into COMP Pin                                                     | I <sub>SOURCE</sub>   | $V_{FB} = V_{REF} - 400 \text{mV}, V_{COMP} = 1.5 \text{V}, V_{CC} = 5.0 \text{V}$ |     | 20  |     | μA    |

| High Clamp Voltage at the COMP Pin                                               | V <sub>CCLP_H</sub>   |                                                                                    |     | 1.8 |     | V     |

| Low Clamp Voltage at the COMP Pin                                                | V <sub>CCLP_L</sub>   |                                                                                    |     | 0.6 |     | V     |

| Error Amplifier Transconductance                                                 | G <sub>EA</sub>       | V <sub>CC</sub> = 5.0V                                                             |     | 190 |     | μA/V  |

| Soft-Start                                                                       |                       |                                                                                    |     |     |     |       |

| Soft-Start Time of Internal Reference Voltage Ramping from 0 to V <sub>REF</sub> | t <sub>SS</sub>       |                                                                                    |     | 7.5 |     | ms    |

| Synchronous Clock                                                                |                       |                                                                                    |     |     |     |       |

| M/SYNC Logic High Threshold                                                      | V <sub>M/SYNC_H</sub> | V <sub>CC</sub> = 5.0V                                                             |     |     | 1.2 | V     |

| M/SYNC Logic Low Threshold (Falling)                                             | V <sub>M/SYNC_L</sub> | V <sub>CC</sub> = 5.0V                                                             | 0.4 |     |     | V     |

| Minimum Sync Clock Pulse Width                                                   | t <sub>SYNC_MIN</sub> |                                                                                    | 50  |     |     | ns    |

| Logic Interface                                                                  |                       |                                                                                    |     |     |     |       |

| MODE Logic High Threshold                                                        | V <sub>MODE_H</sub>   | V <sub>CC</sub> = 5.0V                                                             |     |     | 1.2 | V     |

| MODE Logic Low Threshold                                                         | V <sub>MODE_L</sub>   | V <sub>CC</sub> = 5.0V                                                             | 0.4 |     |     | V     |

| Thermal Shutdown                                                                 | T <sub>SD</sub>       | $T_J$ rising                                                                       |     | 160 |     | °C    |

| Thermal Shutdown Hysteresis                                                      | T <sub>SD_HYS</sub>   |                                                                                    |     | 20  |     | °C    |

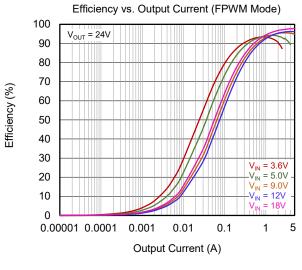

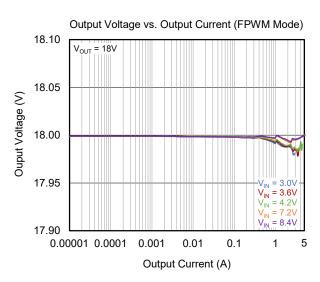

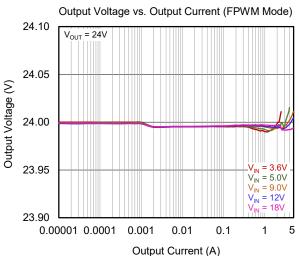

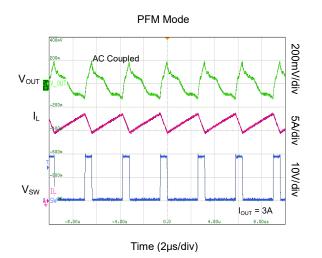

### TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = +25$ °C,  $f_{SW} = 290$ kHz, unless otherwise noted.

$T_A = +25$ °C,  $f_{SW} = 290$ kHz, unless otherwise noted.

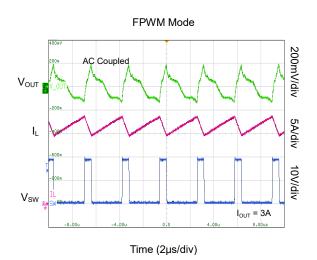

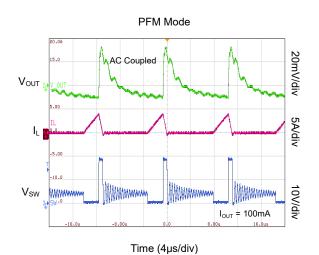

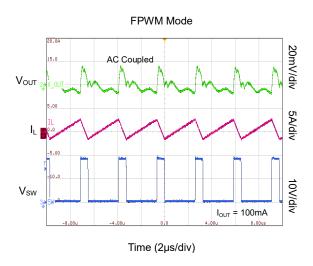

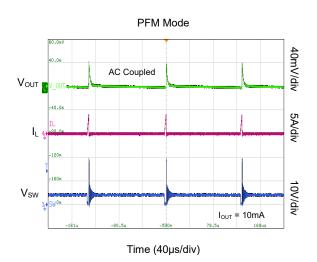

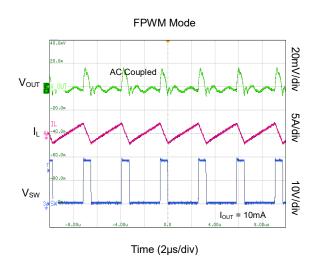

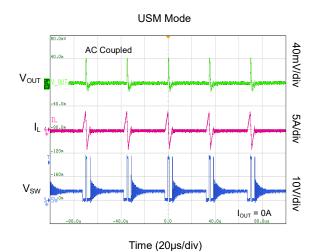

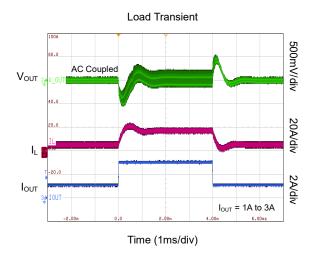

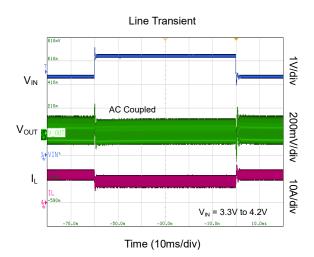

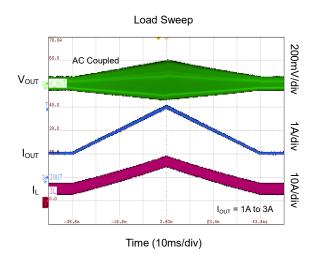

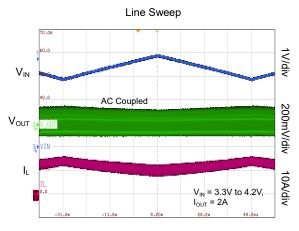

$T_A$  = +25°C,  $V_{IN}$  = 3.6V,  $V_{OUT}$  = 18V, unless otherwise noted.

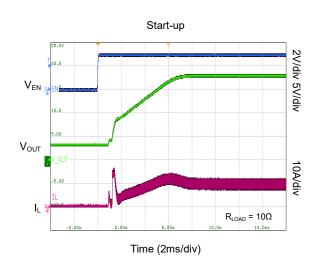

$T_A$  = +25°C,  $V_{IN}$  = 3.6V,  $V_{OUT}$  = 18V, unless otherwise noted.

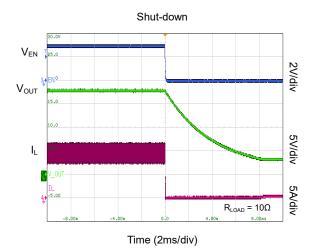

$T_A$  = +25°C,  $V_{IN}$  = 3.6V,  $V_{OUT}$  = 18V, unless otherwise noted.

Time (10ms/div)

### **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. Block Diagram

### **DETAILED DESCRIPTION**

#### Overview

The SGM6620 family is a high-power density, synchronous Boost converter with a  $9.8 m\Omega$  (TYP) high-side MOSFET integrated to provide a high efficiency and small size solution in portable systems. The device is capable of providing an output voltage up to 25V and delivering up to 60W power from a single cell Lithium battery and 100W power from two cells Lithium batteries.

The SGM6620 family uses adaptive constant on-time valley current control topology to regulate the output voltage. In the moderate-to-heavy load condition, the SGM6620 family operates in the quasi-constant frequency pulse width modulation (PWM) mode. As conventional adaptive on-time converters, SGM6620 family varies the on-time as a function of input and output voltage to maintain a nearly constant frequency of 290kHz (TYP). In light load condition, the device has two operation modes selected by the MODE pin. One is the pulse frequency modulation (PFM) mode, which is used to enhance efficiency under light load conditions. The other is the forced pulse width modulation (FPWM) mode, which is employed to avoid application issues arising from low switching frequency. SGM6620A offers ultrasonic mode by pulling MODE pin to logic low. Ultrasonic mode clamps the light load frequency above 30kHz (TYP), as the load increases, the load requires switching frequency above 30kHz, and the device automatically increases the PFM switching frequency. The SGM6620 family implements the cycle-by-cycle current limit to protect the device from overload conditions during Boost switching. The switch valley current limit is up to 20A (TYP). The SGM6620 family uses external loop compensation, which provides flexibility to use different inductors and output capacitors. This adaptive constant on-time valley current control scheme can achieve outstanding transient line response and load response with the requirements of small output capacitance.

To further maximize the power density, the SGM6620 family can support stackable multi-phase operation. A stackable dual-phase converter can be achieved by two SGM6620/A devices. Up to 4 pcs, SGM6620/A can be connected in parallel to meet higher power requirements. The multi-phase operation significantly reduces the peak value of the inductor current and capacitor ripple current, and increases the effective switching frequency, thereby minimizing the size of the inductor and capacitor to the greatest extent.

### **Feature Description**

#### **Under-Voltage Lockout (UVLO)**

The SGM6620 family integrates UVLO feature to protect the device from malfunction when the input voltage is insufficient and prevent the battery from over-discharging. The SGM6620 has two functions:  $V_{\text{IN\_UVLO}}$  and  $V_{\text{CC\_UVLO}}$ . This lockout function causes the device to stop operating when the voltage at the VIN pin drops below the falling UVLO threshold, which is 1.9V (TYP). When the voltage of the VIN pin rises over the rising UVLO threshold 2.2V (TYP), the device starts to operate. The VCC pin also implements UVLO function. The device is disabled when  $V_{\text{CC}}$  drops below the UVLO threshold ( $V_{\text{CC}}$  UVLO), which is 1.8V (TYP).

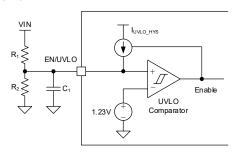

#### **Enable and Programmable UVLO**

The SGM6620/A has a dual-function enable and under-voltage lockout (UVLO) circuit. When the voltage at the VIN pin is higher than the input UVLO rising threshold of 2.2V (TYP) and the voltage at the EN/UVLO pin is higher than 1.15V (MAX) but lower than the enable UVLO threshold of 1.23V (TYP), the device will be enabled but remains in standby mode.

A precise UVLO voltage threshold is implemented at the EN/UVLO pin, so it can support programmable input under-voltage lockout with hysteresis. When the voltage at the EN/UVLO pin is above the UVLO threshold of 1.23V (TYP), the device is enabled. A hysteresis current (I<sub>UVLO\_HYS</sub>) which is sourced from the EN/UVLO pin can provide hysteresis function. It can prevent on/off chattering when the input voltage changes slowly with noise.

As shown in Figure 3, when using a resistor divider circuit, the turn-on threshold can be calculated by Equation 1.

$$V_{IN\_UVLO\_ON} = V_{UVLO} \times \left(1 + \frac{R_1}{R_2}\right)$$

(1)

where,  $V_{\text{UVLO}}$  is the UVLO threshold at the EN/UVLO pin.

The hysteresis of UVLO is set by the resistor between the EN/UVLO pin and VIN pin, which is given by the Equation 2.

$$\Delta V_{\text{IN\_UVLO}} = I_{\text{UVLO\_HYS}} \times R_1$$

(2)

where,  $I_{UVLO\_HYS}$  (5.1 $\mu$ A, TYP) is the current sourced out of the EN/UVLO pin when the EN/UVLO voltage is above  $V_{UVLO}$ .

Figure 3. Programmable UVLO with Resistor Divider Circuit

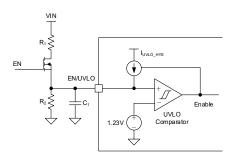

By combining NMOSFET with a resistor divider, the logic enable and programmable UVLO functions can be achieved, as shown in Figure 4. The logic high-level of EN pin must exceed the sum of the enable threshold and the  $V_{\text{TH}}$  of the NMOSFET Q1. The Q1 brings about a benefit which can eliminate the leakage current from VIN to ground through the UVLO resistor divider circuit during the shutdown mode.

When EN voltage is below 0.4V, the device is disabled.

Figure 4. Logic Enable and Programmable UVLO

#### **Enable and Start-up**

The SGM6620 family has a 7.5ms (TYP) soft-start function, which can reduce inrush current during start-up. When the input voltage is valid, pulling the EN input to logic high, a constant current will charge the internal soft-start capacitor. During this period, the voltage of the capacitor will be compared with the internal reference (1.0V, TYP). The lower voltage will be input to the positive input terminal of the internal error amplifier. The output of the error amplifier (which determines the inductor valley current value) will gradually increase as the voltage of the soft-start capacitor rises. The soft-start stage is finished when the voltage of the soft-start capacitor exceeds the internal reference voltage. Pulling the EN input to logic low, the soft-start capacitor voltage will be discharged to around.

## Switching Frequency and External Clock Synchronization

The SGM6620 switches at a quasi-constant 290kHz (TYP) frequency. The SGM6620 family can synchronize with an external clock signal, which is input through the M/SYNC pin. It is suitable for applications that are sensitive to noise or involved in multiple phases. The operating switching frequency will be forced to the external clock when an external clock signal is applied to the M/SYNC pin. The external clock frequency must be within ±20% of default switching frequency, otherwise, the synchronization will fail. The external clock applied to the M/SYNC pin must meet the following requirements: the low-level voltage must be lower than 0.4V, and the high-level voltage must be higher than 1.15V. A clock signal over 50ns wide can be valid and before synchronization, the signal must have a minimum of 4 consecutive clocks.

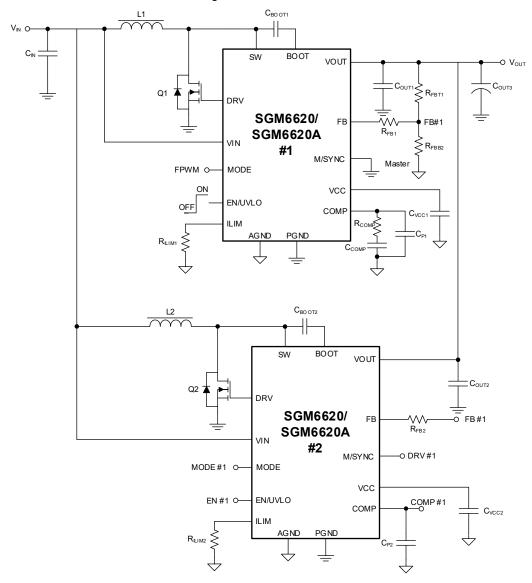

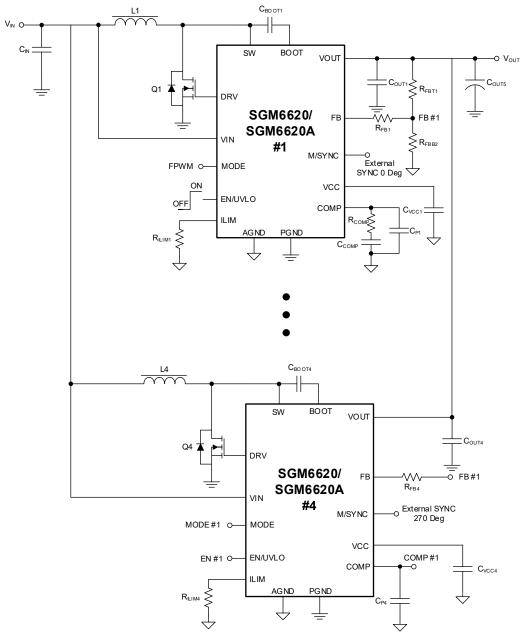

### **Stackable Multi-Phase Operation**

The stackable multi-phase operation can be supported by SGM6620 family. Two devices can realize a master/slave stackable converter. The master device M/SYNC pin should be grounded. The slave device M/SYNC pin should be connected to the drive signal of

the external low-side MOSFET of the master device. Figure 5 shows the 2 pcs SGM6620/A stackable configuration. Considering for current balance and reliable phase shifting, forced PWM mode is recommended.

Figure 5. Dual-Phase Operation for High Power Application

Moreover, up to 4 pcs SGM6620/A can be connected in parallel for multi-phase operation at same switching frequency to meet higher power requirements. The multi-phase operation can significantly reduce the peak inductor current and capacitor ripple current, and

increases the effective switching frequency, thereby minimizing the size of the inductor and capacitor to the greatest extent. Figure 6 shows the 4 pcs SGM6620/A stackable configuration.

Figure 6. Multi-Phase Operation for High Power Application

#### **Device Functional Modes**

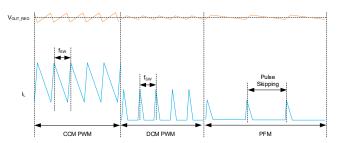

In the moderate to heavy load conditions, the SGM6620 family runs at 290kHz (TYP) frequency PWM mode. Under light load conditions, this device has two selectable working modes: auto PFM mode and forced PWM mode, which are designed to accommodate different application scenarios. SGM6620A offers ultrasonic mode to avoid audible noise.

The operating mode is determined by the configuration of MODE pin. The device works in auto PFM mode when the MODE pin voltage is less than logic low threshold. The device works in forced PWM mode, when the MODE pin voltage is above logic high threshold.

### Forced PWM (FPWM) Mode

For FPWM option, SGM6620 family is locked in PWM mode from full load to no load. Negative inductor currents are allowed at light load to continue PWM operation. It is a tradeoff that sacrifices light load efficiency for lower output ripple, better output regulation, no audible noise and keeping switching frequency fixed. To avoid fatal negative current in the low-side switch, this current is limited at -5A. Synchronization is available over the full load range in the FPWM mode.

#### **Auto PFM Mode**

The SGM6620 family provides auto PFM operation to improve the efficiency at light loads. As the load current decreases in PWM mode, the output of the error amplifier decreases accordingly to reduce the valley inductor current, and thus it delivers less current to the load. As the load decreases further, the inductor current reaches 0A during the high-side FET on-time, the internal zero cross detect comparator triggers to turn off the high-side FET to prevent negative current flow, and waits for the next clock pulse to turn on the low-side FET. As the load current continues decreasing, the output of the error amplifier drops to the PFM threshold voltage and is clamped at this voltage, then the device operates in PFM mode. In PFM operation, the device skips pulses to deliver just enough power to the load and to maintain the output voltage in regulation.

The output voltage remains constant across various operation modes, as shown in Figure 7.

Figure 7. Auto PFM Mode Diagram

#### **Switching Valley Current Limit**

The SGM6620 family implements a cycle-by-cycle inductor valley current limit in case of over-current situation. When the internal high-side MOSFET is turned on, the inductor current is sensed by the voltage drop across the MOSFET. If the valley current limit threshold is triggered, the high-side MOSFET will turn off at once. The limit threshold can be set by an external resistor between the ILIM pin and the AGND pin, which can be calculated by Equation 3.

$$I_{VALLEY}(A) = \frac{400k\Omega}{R_{ILIM}(k\Omega)}$$

(3)

where,  $R_{\text{ILIM}}$  is the external resistor set between the ILIM pin and the AGND pin.  $I_{\text{VALLEY}}$  is the threshold of inductor valley current limit.

#### **Ultrasonic Mode**

The SGM6620A provides ultrasonic mode operation at light load. Pulling the MODE pin to logic low configures ultrasonic mode, and pulling the MODE pin to logic high configures FPWM mode. The SGM6620A clamps the switching frequency to 30kHz (TYP) at light load to avoid audible noise, and as the load increases, the device automatically increases the switching frequency to meet the load demand.

#### **Over-Voltage Protection**

SGM6620 family integrates over-voltage protection (OVP) to protect the device in the event of feedback resistor short-to-ground or incorrect feedback resistor value being populated. The SGM6620/A stops switching when the OVP threshold of 26.5V (TYP) is reached. When the output voltage is 1V lower than the OVP threshold, the device resumes switching.

### **Thermal Shutdown**

To protect the device from overheating damage, thermal protection is included in the device. If the junction temperature exceeds 160°C (TYP), the switching will stop. The device operation will resume when the junction temperature is cooled down by 20°C (TYP).

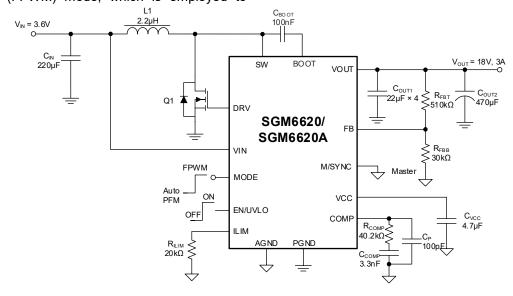

### APPLICATION INFORMATION

The SGM6620 family is capable of providing an output voltage up to 25V with the 20A valley switch current. In the moderate-to-heavy load condition, the SGM6620 family operates in the quasi-constant frequency pulse width modulation (PWM) mode. Under light load condition, the device can support two working modes. One is the pulse frequency modulation (PFM) mode, which is used to enhance efficiency; the other is the forced PWM (FPWM) mode, which is employed to

avoid application issues arising from low switching frequency. This adaptive constant on-time valley current control scheme can achieve outstanding transient line response and load response with the requirements of small output capacitance. The SGM6620 family uses external loop compensation, which provides flexibility to use different inductors and output capacitors.

Figure 8. 3.6V V<sub>IN</sub> to 18V V<sub>OUT</sub> 3A Output Converter

### Design Requirements

**Table 1. Design Parameters**

| DESIGN PARAMETERS     | EXAMPLE VALUES     |

|-----------------------|--------------------|

| Input Voltage Range   | 3.3V to 4.2V       |

| Output Voltage        | 18V                |

| Output Voltage Ripple | 350mV Peak-to-Peak |

| Output Current Rating | 3A                 |

# **Detailed Design Procedure Setting Output Voltage**

A resistor divider connected between VOUT and FB pins programs the output voltage. In order to achieve the best output voltage accuracy, the recommended value for  $R_2$  should ensure that the current flowing through  $R_2$  is 100 times larger than the leakage current flowing into the FB pin. Lower  $R_2$  resistance also improves the device noise immunity.

The R<sub>1</sub> resistance can be calculated via Equation 4:

$$R_1 = \frac{\left(V_{\text{OUT}} - V_{\text{REF}}\right) \times R_2}{V_{\text{REF}}} \tag{4}$$

### **APPLICATION INFORMATION (continued)**

#### **Input Capacitor Selection**

Boost converter's input capacitor has continuous current throughout the entire switching cycle and a  $22\mu F$  ceramic capacitor is recommended to place as close as possible between the VIN pin and GND pin. For applications where the SGM6620/A is located far away from the input source, a higher capacitance capacitor or additional "Bulk" capacitor (electrolytic or tantalum) is recommended to damp the wiring harness inductance.

#### **Inductor Selection**

Inductor is an essential element for current DC/DC switch mode power supplies regardless of topology. Inductor serves as the energy storage element for power conversion. Inductance, DC resistance and saturation current of inductor are three most important criterions for inductor selection. For general design guidance, the selected inductance should provide a peak-to-peak ripple current that is around 30% of the average inductor current at full load and nominal input voltage. The average inductor current for a Boost converter is the input current. Equation 5 shows the calculation of inductance selection.

$$L_{\text{MIN}} = \frac{V_{\text{IN\_MIN}} \times \left(V_{\text{OUT\_MAX}} - V_{\text{IN\_MIN}}\right)}{\Delta I_{\text{I}} \times f_{\text{SW}} \times V_{\text{OUT\_MAX}}}$$

(5)

where,

- $\bullet$   $V_{\text{IN\_MIN}}$  is the minimum input voltage of Boost converter.

- $\bullet$   $V_{\text{OUT\_MAX}}$  is the maximum output voltage of Boost converter.

- ΔI<sub>L</sub> is the inductor current ripple.

- f<sub>SW</sub> is the converter switching frequency.

- L<sub>MIN</sub> is the minimum inductance needed.

The SGM6620 family is optimized to operate with inductance ranges from 2.2 $\mu$ H and 4.7 $\mu$ H. For a single cell Lithium battery application, which input voltage is below 5V and the output voltage is less than 16V, a 2.2 $\mu$ H inductor can meet the requirement. For multi-cell Lithium batteries application or the output voltage is over 16V, considering the inductor ripple current and negative current limit (-5A, MAX) in FPWM mode, a 3.3 $\mu$ H or 4.7 $\mu$ H inductor is recommended.

The minimal saturation current rating of the selector inductor should be higher than the worst-case peak current of the application.

Lower DCR inductor is recommended to improve the conversion efficiency of the device, especially for large

load current applications. As shown in Equation 5, smaller inductance increases the peak-to-peak current, which results in higher AC core loss of the inductor. However, the tradeoff of smaller inductance parts comes with smaller footprint and larger inductance parts with same saturation current rating generally comes with larger footprint.

#### **Bootstrap and VCC Capacitors Selection**

An internal regulator provides the bias voltage for gate driver using a  $0.1\mu F$  ceramic capacitor. A ceramic capacitor with good quality, low ESR is recommended. The capacitor must have a 10V or higher voltage rating. The BOOT capacitor is refreshed when the high-side MOSFET is off and the external low-side diode conducts.

The internal LDO in the SGM6620 family outputs a regulated voltage of 5V. A ceramic capacitor is connected between the VCC pin and GND pin to stabilize the VCC voltage and also decouple the noise on the VCC pin. The value of this ceramic capacitor must be above 2.2µF. A ceramic capacitor with an X7R or X5R grade dielectric with a voltage rating higher than 10V is recommended.

#### **MOSFET Selection**

The external low-side power MOSFET must choose whose  $V_{DS}$  rating can be capable of withstanding the maximum output voltage plus a transient spike. In this application, a MOSFET with 40V rated voltage is selected.

Once the operating voltage level is determined, the MOSFET can be selected by balancing the conduction loss and switching loss that are associated with MOSFET conduction resistor and total gate charge (Qg).

Please note the limitation of the dead time and confirm that the MOSFETs on the low-side and high-side will not turn on synchronously. For this high switching frequency design, a leadless package is better, as it can minimize the parasitic inductance in the driver circuit. Be careful when connecting a resistor in series to the gate, as this may shorten the actual dead time.

The gate driver current of the MOSFET in this device is powered by VCC. Please confirm that the value of the gate threshold voltage ( $V_{TH}$ ) must be lower than the minimum input voltage to ensure the MOSFET is fully turned on.

### **APPLICATION INFORMATION (continued)**

### **Output Capacitor Selection**

The output capacitors of Boost converter dictate the output voltage ripple and load transient response. Equation 6 are used to estimate the necessary capacitance to achieve desired output voltage ripple. The DC bias effect of the ceramic capacitor should be considered when selecting the capacitors. The voltage rating of the selected capacitor should be higher than the maximum operation output voltage with > 30% margin. When using tantalum or aluminum electrolytic capacitors, the ESR must be considered to calculate the output voltage ripple.

$$C_{MIN} = \frac{I_{OUT} \times (V_{OUT} - V_{IN\_MIN})}{f_{SW} \times \Delta V \times V_{OLIT}}$$

(6)

where,

- $V_{\text{IN\_MIN}}$  is the minimum input voltage of the Boost converter.

- V<sub>OUT</sub> is the output voltage.

- $\bullet$   $\quad \Delta V$  is the maximum acceptable output voltage ripple.

- I<sub>OUT</sub> is the output current.

- f<sub>SW</sub> is the converter switching frequency.

- C<sub>MIN</sub> is the minimum capacitance needed.

#### **Loop Stability**

The compensation network of SGM6620 family is implemented externally to improve design flexibility. The SGM6620 family implements a trans-conductance error amplifier, where the COMP pin is the output of the internal error amplifier. A type-II compensation network consisting of  $R_{\text{COMP}},\,C_{\text{COMP}}$  and  $C_{\text{P}}$  connected to the COMP pin is used to configure the loop response of SGM6620 family.

The power stage small signal loop response of peak current control can be modeled by Equation 7.

$$G_{PS}(S) = K_{COMP} \times \frac{R_{OUT} \times (1-D)}{2} \times \frac{\left(1 + \frac{S}{2\pi f_{ESRZ}}\right) \times \left(1 - \frac{S}{2\pi f_{RHPZ}}\right)}{1 + \frac{S}{2\pi f_{P}}} \times \frac{I_{COMP1}, I_{COMP2} \text{ are compensation network.}}{I_{COMP2} \times I_{COMP2} \times I_{C$$

where,

• D is the switching duty cycle.

- R<sub>OUT</sub> is the output load resistance.

- K<sub>COMP</sub> is power stage trans-conductance (inductor peak current / comp voltage), which is 25A/V.

- f<sub>P</sub> is the pole's frequency.

- f<sub>ESRZ</sub> is the zero's frequency.

- f<sub>RHPZ</sub> is the right-half-plane-zero's frequency.

$$f_{p} = \frac{2}{2\pi \times R_{OUT} \times C_{OUT}}$$

(8)

where,

${}^{\bullet}$   $C_{\text{OUT}}$  is effective capacitance of the output capacitor.

$$f_{ESRZ} = \frac{1}{2\pi \times R_{ESR} \times C_{OUT}}$$

(9)

where,

$\bullet$   $\;$   $R_{\text{ESR}}$  is the equivalent series resistance of the output capacitor.

$$f_{RHPZ} = \frac{R_{OUT} \times (1-D)^2}{2\pi \times L}$$

(10)

Equation 11 shows the small signal transfer function of compensation network.

$$G_{\text{C}}(S) = \frac{G_{\text{EA}} \times R_{\text{EA}} \times V_{\text{REF}}}{V_{\text{OUT}}} \times \frac{\left(1 + \frac{S}{2\pi f_{\text{COMZ}}}\right)}{\left(1 + \frac{S}{2\pi f_{\text{COMP1}}}\right) \times \left(1 + \frac{S}{2\pi f_{\text{COMP2}}}\right)}$$

(11)

where

- G<sub>EA</sub> is the amplifier trans-conductance.

- R<sub>EA</sub> is the amplifier's output resistance.

- V<sub>REF</sub> is the FB reference voltage.

- V<sub>OUT</sub> is the output voltage.

- $f_{\text{COMP1}}$ ,  $f_{\text{COMP2}}$  are the pole's frequency of the compensation network.

- $\bullet \quad f_{\text{COMZ}}$  is the zero's frequency of the compensation network.

### **APPLICATION INFORMATION (continued)**

Once the error amplifier and power stage's poles and zeros are determined, the component value of compensation network can be designed. The designed loop crossover frequency ( $f_C$ ) should be within 1/5 of the RHPZ frequency ( $f_{RHPZ}$ ) or 1/10 of the switching frequency. Higher crossover frequency could improve the transient response. However, the crossover frequency could be designed to avoid instability.

With a selected  $f_C$ , use Equation12 to calculate the required  $R_{COMP}$ .

$$R_{\text{COMP}} = \frac{2\pi \times V_{\text{OUT}} \times C_{\text{OUT}} \times f_{\text{C}}}{(1-D) \times V_{\text{REF}} \times G_{\text{EA}} \times K_{\text{COMP}}}$$

(12)

where.

•  $f_C$  is the selected crossover frequency. The value of  $C_{COMP}$  can be calculated by Equation 13.

$$C_{COMP} = \frac{R_{OUT} \times C_{OUT}}{2R_{COMP}}$$

(13)

The value of C<sub>P</sub> can be calculated by Equation 14.

$$C_{P} = \frac{R_{ESR} \times C_{OUT}}{R_{COMP}}$$

(14)

$C_{\text{P}}$  is not needed, when applications only use ceramic capacitor or the calculated value of  $C_{\text{P}}$  is less than 10pF.

To measure good loop compensation design, greater than 45° of phase margin and greater than 10dB gain margin could provide good loop stability and avoid output voltage ringing during load and line transient.

Table 2. Recommended L,  $R_{COMP}$  and  $C_{COMP}$  for Different Input and Output Voltages

|                     | ilpat and Catpat Voltagoo |        |                     |                        |  |  |  |  |  |  |

|---------------------|---------------------------|--------|---------------------|------------------------|--|--|--|--|--|--|

| V <sub>IN</sub> (V) | V <sub>OUT</sub> (V)      | L (µH) | $R_{COMP}(k\Omega)$ | C <sub>COMP</sub> (nF) |  |  |  |  |  |  |

| 3.6                 | 5                         | 2.2    | 6.2                 | 3.3                    |  |  |  |  |  |  |

| 3.6                 | 18                        | 3.3    | 40.2                | 3.3                    |  |  |  |  |  |  |

| 3.6                 | 25                        | 4.7    | 40.2                | 6.8                    |  |  |  |  |  |  |

| 7.2                 | 18                        | 3.3    | 40.2                | 3.3                    |  |  |  |  |  |  |

| 7.2                 | 25                        | 4.7    | 40.2                | 3.3                    |  |  |  |  |  |  |

| 10.8                | 18                        | 3.3    | 34                  | 3.3                    |  |  |  |  |  |  |

| 10.8                | 25                        | 4.7    | 30                  | 3.3                    |  |  |  |  |  |  |

### **Power Supply Recommendations**

The SGM6620 family operates from a wide 2.05V to 23V input voltage. If the input power supply is located far away from the device, apart from the ceramic capacitors, additional Bulk capacitor may also be needed.

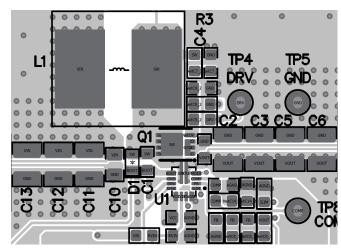

### **Layout Guidelines**

Layout is a critical step to ensure the performance of any switch mode power supplies, in addition to component selection. Poor layout could result in system instability, EMI failure, and device damage. Thus, place the inductor, input capacitors and output capacitors as close to the IC as possible, and use wide and short traces for current carrying traces to minimize PCB parasitic inductance.

For Boost converter, the current loop of the output capacitor from VOUT pin back to the GND pin of the device should be as small as possible. The traces connected to SW node should be as short as possible. A ground plane underneath the SGM6620/A is recommended to minimize inter-plane coupling.

Due to the high power density of SGM6620/A, the current-carrying SW, VOUT, VIN and PGND pins should be connected with large copper polygon pour to ensure good thermal performance, and thermal vias on these nodes are recommended.

Figure 9. PCB Layout

#### REVISION HISTORY

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Original to REV.A (NOVEMBER 2025)

Page

Changed from product preview to production data.......All

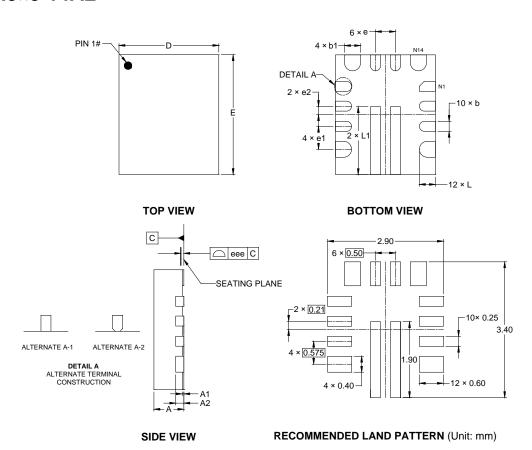

# PACKAGE OUTLINE DIMENSIONS TQFN-2.5×3-14AL

| Cumbal | Dimensions In Millimeters |           |       |  |  |  |  |

|--------|---------------------------|-----------|-------|--|--|--|--|

| Symbol | MIN                       | NOM       | MAX   |  |  |  |  |

| А      | 0.700                     | -         | 0.800 |  |  |  |  |

| A1     | 0.000                     | -         | 0.050 |  |  |  |  |

| A2     |                           | 0.203 REF |       |  |  |  |  |

| b      | 0.200                     | -         | 0.300 |  |  |  |  |

| b1     | 0.350                     | -         | 0.450 |  |  |  |  |

| D      | 2.400                     | -         | 2.600 |  |  |  |  |

| Е      | 2.900                     | -         | 3.100 |  |  |  |  |

| е      | 0.500 BSC                 |           |       |  |  |  |  |

| e1     |                           | 0.575 BSC |       |  |  |  |  |

| e2     | 0.210 BSC                 |           |       |  |  |  |  |

| L      | 0.300                     | 0.300 -   |       |  |  |  |  |

| L1     | 1.600                     | 1.600 -   |       |  |  |  |  |

| eee    |                           | 0.080     |       |  |  |  |  |

NOTE: This drawing is subject to change without notice.

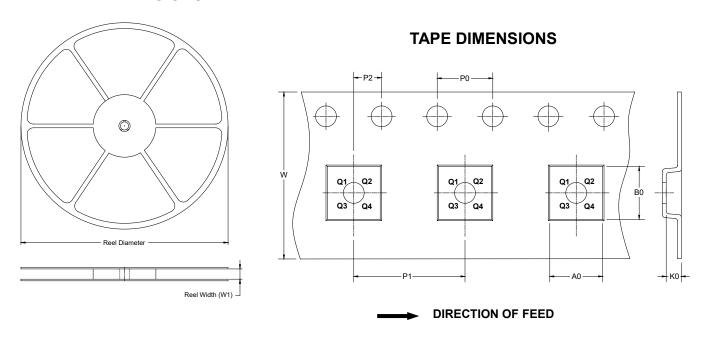

### TAPE AND REEL INFORMATION

### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

### **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type    | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |        |

|-----------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|--------|

| TQFN-2.5×3-14AL | 13"              | 12.4                     | 2.80       | 3.30       | 1.10       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               | DD0001 |

### **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

### **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |        |

|-----------|----------------|---------------|----------------|--------------|--------|

| 13″       | 386            | 280           | 370            | 5            | DD0002 |