# SGM795 Programmable USB Type-C Port Controller

#### GENERAL DESCRIPTION

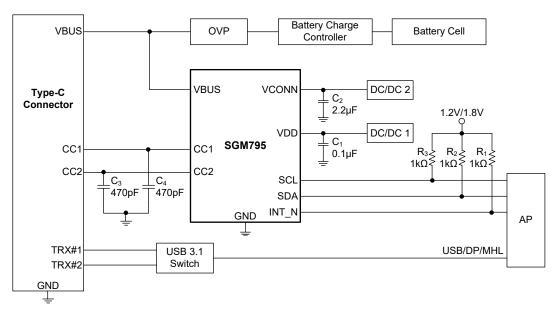

The SGM795 is a USB Type-C Port Controller (TCPC) designed in compliance with the latest USB Type-C and PD 3.2 standards. It encapsulates VBUS and VCONN power control, USB Type-C CC logic, the USB PD BMC physical layer, and a portion of the USB PD protocol layer. The SGM795 has programmable Rp and Rd settings for each CC line and performs USB Type-C detection, including attachment and orientation. The SGM795 incorporates a complete BMC encoding system, including a receiver and a transmitter. This enables the SGM795 to send and receive USB PD messages on the configuration channel (CC) connection, support a VBUS voltage level up to 20V, and execute role swaps as needed. BMC PD module fully accommodates alternative interfaces in Type-C specification. For communication with the USB Type-C Port Manager (TCPM), the SGM795 utilizes I<sup>2</sup>C and employs an INT signal to request attention.

The SGM795 is available in a Green WLCSP-1.17×1.17-9B package.

#### **FEATURES**

- Dual-Role PD Compatible

- Attach/Detach Detection as Host, Device or DRP

- Active Cable Recognition

- Current Capability Advertisement and Detection

- Integrated VBUS Bleed/Force Discharge

- VCONN Switch with Programmable OCP

- VCONN Over-Temperature Protection

- VCONN to CC Dual Side OVP

- Dead Battery Support

- Ultra-Low Power Mode for Attach Detection

- Support TCPCI over I<sup>2</sup>C Communication at 1.2V and 1.8V Level

- BIST Mode Supported

- USB PD PHY Supports PD 3.2 Except Fast Role Swap Function

- Available in a Green WLCSP-1.17×1.17-9B Package

#### **APPLICATIONS**

Smart Phones

Tablets and Laptops

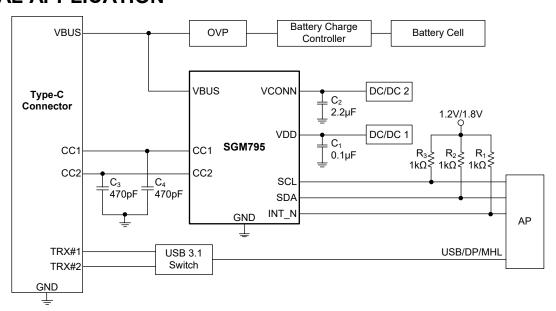

#### TYPICAL APPLICATION

**Figure 1. Typical Application Circuit**

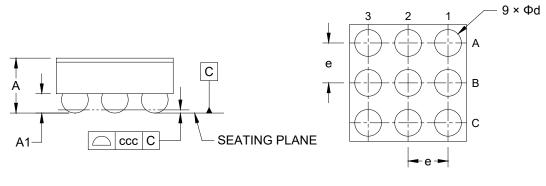

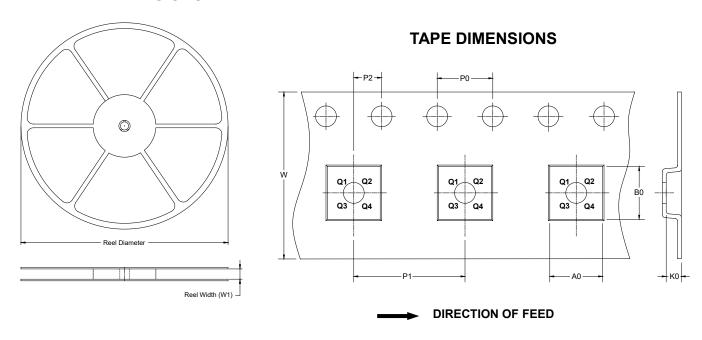

#### PACKAGE/ORDERING INFORMATION

| MODEL  | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | TEMPERATURE ORDERING |             | PACKING<br>OPTION   |  |

|--------|------------------------|-----------------------------------|----------------------|-------------|---------------------|--|

| SGM795 | WLCSP-1.17×1.17-9B     | -40°C to +85°C                    | SGM795YG/TR          | 795<br>XXXX | Tape and Teel, 3000 |  |

#### MARKING INFORMATION

NOTE: XXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### ABSOLUTE MAXIMUM RATINGS

| VDD/VCONN Voltage0.3V to 6V                   |

|-----------------------------------------------|

| CC1/CC2 Voltage0.3V to 24V                    |

| VBUS Voltage0.3V to 28V                       |

| SDA, SCL, INT_N Voltage0.3V to 6V             |

| Package Thermal Resistance                    |

| WLCSP-1.17×1.17-9B, θ <sub>JA</sub> 146.4°C/W |

| WLCSP-1.17×1.17-9B, θ <sub>JB</sub>           |

| WLCSP-1.17×1.17-9B, θ <sub>JC</sub>           |

| Junction Temperature+150°C                    |

| Storage Temperature Range65°C to +150°C       |

| Lead Temperature (Soldering, 10s)+260°C       |

| ESD Susceptibility (1)(2)                     |

| HBM±3000V                                     |

| CDM±1000V                                     |

| NOTES:                                        |

- 1. For human body model (HBM), all pins comply with ANSI/ESDA/JEDEC JS-001 specifications.

- 2. For charged device model (CDM), all pins comply with ANSI/ESDA/JEDEC JS-002 specifications.

#### RECOMMENDED OPERATING CONDITIONS

| VDD Input Voltage                    | 3.0V to 5.5V   |

|--------------------------------------|----------------|

| VCONN Input Voltage                  | 3.3V to 5.5V   |

| VCONN Supply Current                 | 200mA to 600mA |

| Operating Junction Temperature Range | 40°C to +125°C |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

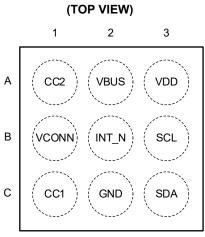

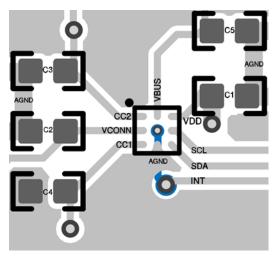

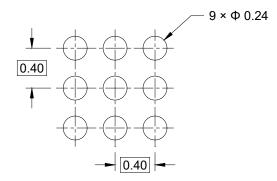

#### **PIN CONFIGURATION**

WLCSP-1.17×1.17-9B

#### **PIN DESCRIPTION**

| PIN | NAME         | TYPE  | FUNCTION                                                                                                                                                                                                                                                                             |

|-----|--------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1  | CC2          | AI/AO | Configuration Channel Pins. It is used to detect when an attachment is connected and its orientation. Connect to CC1/CC2 of Type-C connector. For stable communication, place a minimum of 470pF ceramic capacitor between the CC2 and GND pins, as close to the device as possible. |

| A2  | VBUS         | Al    | VBUS Input Pin. It is used to attach and detach detection. Connect to VBUS pin of Type-C Connector.                                                                                                                                                                                  |

| А3  | VDD          | Р     | Input Supply Voltage Pin. Use a 0.1µF or larger ceramic capacitor between VDD and GND pins close to the device.                                                                                                                                                                      |

| B1  | VCONN        | Р     | VCONN Power Input Pin. It can be switched to the selected CC pin. Short VCONN to GND if not used. Use a 2.2µF or larger ceramic capacitor between VCONN and GND pins close to the device.                                                                                            |

| B2  | INT_N        | DO    | Open-Drain Interrupt Output Pin. Low signal asserted to notify TCPM of alert register updates. Use a $1k\Omega$ pull-up to the logic high rail.                                                                                                                                      |

| В3  | SCL          | DI/DO | I <sup>2</sup> C Clock Signal Pin. Connect it to the I <sup>2</sup> C master. The device I <sup>2</sup> C controller block is forced to reset when receiving 9 clock pulses on the SCL line.                                                                                         |

| C1  | C1 CC1 Al/AO |       | Configuration Channel Pins. It is used to detect when an attachment is connected and its orientation. Connect to CC1/CC2 of Type-C connector. For stable communication, place a minimum of 470pF ceramic capacitor between the CC1 and GND pins, as close to the device as possible. |

| C2  | GND          | Р     | Ground.                                                                                                                                                                                                                                                                              |

| С3  | SDA          | DI/DO | $I^2C$ Data Signal Pin. Connect it to the $I^2C$ master. The SDA line is forced to release when the 25ms $I^2C$ timeout fault occurs.                                                                                                                                                |

NOTE: Al = analog input, Al/AO = analog input/output, DO = digital output, DI/DO = digital input/output, P = power.

### **ELECTRICAL CHARACTERISTICS**

( $V_{DD}$  = 3V to 5.5V,  $T_J$  = +25°C, unless otherwise noted.)

| PARAMETER                                                                                                               | SYMBOL                | CONDITIONS                                                                                                                             | MIN  | TYP   | MAX  | UNIT |

|-------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|------|

| VDD Supply                                                                                                              |                       |                                                                                                                                        |      |       |      |      |

| VDD Voltage Range                                                                                                       | $V_{DD}$              |                                                                                                                                        | 3    |       | 5.5  | V    |

| VCONN Voltage Range                                                                                                     | V <sub>CONN</sub>     |                                                                                                                                        | 3.3  |       | 5.5  | V    |

| UVLO Rising Voltage                                                                                                     | V <sub>UVLO_H</sub>   |                                                                                                                                        | 2.3  | 2.44  | 2.6  | V    |

| UVLO Falling Voltage                                                                                                    | V <sub>UVLO_L</sub>   |                                                                                                                                        | 2.0  | 2.20  | 2.3  | V    |

| UVLO Hysteresis                                                                                                         | V <sub>UVLO_HYS</sub> |                                                                                                                                        |      | 240   |      | mV   |

| Common Normative Signaling Requirem                                                                                     | ents                  |                                                                                                                                        |      | I.    |      |      |

| Bit Rate                                                                                                                | $f_{BR}$              |                                                                                                                                        | 270  | 300   | 330  | Kbps |

| Common Normative Signaling Requirem                                                                                     | ents for Tra          | ansmitter                                                                                                                              |      | ·     |      |      |

| Maximum Difference between the Bit-Rate during the Part of the Packet Following the Preamble and the Reference Bit-Rate | p <sub>BR</sub>       |                                                                                                                                        |      |       | 0.25 | %    |

| Time from the End of Last Bit of a Frame until the Start of the First Bit of the Next Preamble                          | t <sub>IFG</sub>      |                                                                                                                                        | 25   |       |      | μs   |

| Time before the Start of the First Bit of the Preamble when the Transmitter Shall Start Driving the Line                | t <sub>SD</sub>       |                                                                                                                                        | -1   |       | 1    | μs   |

| <b>BMC Common Normative Requirements</b>                                                                                |                       |                                                                                                                                        |      |       |      |      |

| Time to Cease Driving the Line after the End of the Last Bit of the Frame                                               | t <sub>ED_BMC</sub>   |                                                                                                                                        |      |       | 23   | μs   |

| Fall Time                                                                                                               | t <sub>F</sub>        |                                                                                                                                        | 300  |       |      | ns   |

| Time to Cease Driving the Line after the Final High-to-Low Transition                                                   | t <sub>HL_BMC</sub>   |                                                                                                                                        | 1    |       |      | μs   |

| Rise Time                                                                                                               | t <sub>R</sub>        |                                                                                                                                        | 300  |       |      | ns   |

| Voltage Swing                                                                                                           | $V_{SWING}$           |                                                                                                                                        | 1.05 | 1.125 | 1.2  | V    |

| Transmitter Output Impedance                                                                                            | Z <sub>DRIVER</sub>   |                                                                                                                                        | 33   |       | 75   | Ω    |

| <b>BMC Receiver Normative Requirements</b>                                                                              |                       |                                                                                                                                        |      |       |      |      |

| Time Window for Detecting Non-Idle                                                                                      | t <sub>TW</sub>       |                                                                                                                                        | 12   |       | 20   | μs   |

| Receiver Input Impedance                                                                                                | Z <sub>BMC_RX</sub>   |                                                                                                                                        | 1    |       |      | ΜΩ   |

| Power Consumption                                                                                                       |                       |                                                                                                                                        |      |       |      |      |

| Stand-by Mode                                                                                                           | I <sub>SB_SINK</sub>  | Sink current consumption in cable attached,<br>$V_{DD} = V_{DD 12C} = 3.8V (TYP)$                                                      | 80   | 105   | 130  | μΑ   |

| Low Power Mode                                                                                                          | I <sub>LP_DRP</sub>   | CC toggle at DRP mode when port is unconnected and waiting for connection, $V_{DD} = V_{DD}$ $_{I2C} = 3.8V$ (TYP)                     | 12   | 18    | 25   | μΑ   |

| Stand-by BMC-TX Current                                                                                                 | I <sub>SB_BMC</sub>   | Stand-by sink attached current when transmitting BIST carrier mode 2, V <sub>DD</sub> = V <sub>DD 12C</sub> = 3.8V (TYP)               | 0.9  | 1.2   | 1.4  | mA   |

| Shutdown Mode                                                                                                           | I <sub>SD</sub>       | The CC pin exposes RD and disables all functions except I <sup>2</sup> C functions, V <sub>DD</sub> = V <sub>DD_I2C</sub> = 3.8V (TYP) | 2    | 3     | 5    | μΑ   |

| Shutdown Mode When $V_{\text{DD}}$ unequal $V_{\text{DDI2C}}$                                                           | I <sub>SD_I2C</sub>   | The CC pin exposes RD and disables all functions except $I^2$ C functions, $V_{DD} = 3.8V$ (TYP), $V_{DD\_12C} = 1.2V$ to $5.5V$       |      |       | 20   | μΑ   |

| VCONN Power                                                                                                             | I <sub>VCONN</sub>    | VCONN current consumption when VCONN without supply to CC, $V_{CONN} = 3V$ to 5.5V, $V_{DD} = 5V$ (TYP)                                | 0    | 1     | 2    | μΑ   |

### **ELECTRICAL CHARACTERISTICS (continued)**

( $V_{DD}$  = 3V to 5.5V,  $T_J$  = +25°C, unless otherwise noted.)

| PARAMETER                                                                 | SYMBOL                   | CONDITIONS                                              | MIN      | TYP  | MAX  | UNIT |

|---------------------------------------------------------------------------|--------------------------|---------------------------------------------------------|----------|------|------|------|

| Type-C Port Control                                                       |                          |                                                         | •        |      |      |      |

| R <sub>ON</sub> for VCONN Switch                                          | Ron                      | V <sub>CONN</sub> = 3V to 5.5V                          |          | 0.7  | 1    | Ω    |

| VCONN OCP Setting Range                                                   | I <sub>OCP</sub>         | V <sub>CONN</sub> = 3.3V to 5.5V                        | 200      |      | 600  | mA   |

|                                                                           |                          | $V_{DD}$ = 3.3V, $V_{CONN}$ = 5V, OCP setting = 200mA   | 126      | 200  | 269  |      |

|                                                                           |                          | $V_{DD} = 3.3V$ , $V_{CONN} = 5V$ , OCP setting = 300mA | 228      | 300  | 365  | 1    |

| VCONN OCP Range                                                           | I <sub>OCP_RANGE</sub>   | $V_{DD} = 3.3V$ , $V_{CONN} = 5V$ , OCP setting = 400mA | 339      | 400  | 454  | mA   |

|                                                                           |                          | $V_{DD}$ = 3.3V, $V_{CONN}$ = 5V, OCP setting = 500mA   | 437      | 500  | 557  | 1    |

|                                                                           |                          | $V_{DD}$ = 3.3V, $V_{CONN}$ = 5V, OCP setting = 600mA   | 548      | 600  | 651  |      |

| Time for VCONN Switch to Turn-On                                          | t                        | $V_{DD} = 3.3V, V_{CONN} = 3.3V$                        |          | 320  |      | 116  |

| State                                                                     | t <sub>SOFT_VCCON</sub>  | $V_{DD} = 3.3V$ , $V_{CONN} = 5V$                       |          | 350  |      | μs   |

| SRC 80µA CC Current                                                       | ICC <sub>80µ</sub>       |                                                         | 64       | 80   | 96   | μΑ   |

| SRC 180µA CC Current                                                      | ICC <sub>180µ</sub>      |                                                         | 166      | 180  | 194  | μA   |

| SRC 330µA CC Current                                                      | ICC <sub>330µ</sub>      |                                                         | 304      | 330  | 356  | μA   |

| SNK Rd                                                                    | Rd                       |                                                         | 4.59     | 5.10 | 5.61 | kΩ   |

| Ra                                                                        | Ra                       |                                                         |          | 1.1  |      | kΩ   |

| UFP Pull-Down Voltage in Dead Battery under SRC 80µA                      | V <sub>DEAD_DEFF</sub>   | V <sub>DD</sub> = 0V dead battery                       | 0.25     |      | 1.5  | V    |

| UFP Pull-Down Voltage in Dead Battery under SRC 180µA                     | V <sub>DEAD_1.5A</sub>   | V <sub>DD</sub> = 0V dead battery                       | 0.45     |      | 1.5  | V    |

| UFP Pull-Down Voltage in Dead Battery under SRC 330µA                     | $V_{DEAD\_3A}$           | V <sub>DD</sub> = 0V dead battery                       | 0.85     |      | 2.45 | V    |

| VBUS                                                                      |                          |                                                         |          |      |      |      |

| VBUS Voltage Detection Level                                              | V <sub>BUSIN</sub>       |                                                         |          |      | 20   | ٧    |

| Source Bulk Capacitance when a Port is Powered from a Dedicated Supply    | C <sub>SRC_BULK</sub>    |                                                         | 10       |      | 150  | μF   |

| Bulk Capacitance on VBUS a Sink is Allowed after a Successful Negotiation | C <sub>SNK_BULK_PD</sub> |                                                         | 1        |      | 100  | μF   |

| VBUS Bleed Discharge                                                      | I <sub>VBUS_BLEED</sub>  | V <sub>BUS</sub> = 5V                                   | 610      | 660  | 725  | μΑ   |

| VBUS Force Discharge                                                      | I <sub>VBUS_FORCE</sub>  | $V_{BUS} = 5V$ , $V_{DD} = 3.8V$                        | 84       | 100  | 115  | mA   |

| VBUS Present Rising Threshold                                             |                          |                                                         |          | 4    |      | V    |

| VBUS Present Falling Threshold                                            |                          |                                                         |          | 3.5  |      | V    |

| VBUS vsafe0V Threshold                                                    |                          |                                                         |          |      | 0.8  | V    |

| VBUS vsafe5V Low Threshold                                                |                          |                                                         |          |      | 4.75 | V    |

| VBUS vsafe5V High Threshold                                               |                          |                                                         | 5.5      |      |      | V    |

| OTSD                                                                      |                          | 1                                                       | <u> </u> |      | 1    | -    |

| VCONN Thermal Protection Shutdown                                         | T <sub>VCONN_OTSDH</sub> |                                                         |          | 145  |      | °C   |

| VCONN Thermal Protection Release                                          | T <sub>VCONN_OTSDL</sub> |                                                         |          | 135  |      | °C   |

|                                                                           |                          | I                                                       | l        |      | 1    |      |

### **ELECTRICAL CHARACTERISTICS (continued)**

( $V_{DD}$  = 3V to 5.5V,  $T_J$  = +25°C, unless otherwise noted.)

| PARAMETER                                                         | SYMBOL             | CONDITIONS                                                                        | MIN  | TYP | MAX  | UNIT |

|-------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------|------|-----|------|------|

| I <sup>2</sup> C Electrical Characteristics                       |                    |                                                                                   |      |     |      |      |

| I <sup>2</sup> C Bus Supply Voltage                               | $V_{DD\_I2C}$      |                                                                                   | 1.2  |     | 2.0  | V    |

| Low-Level Input Voltage                                           | V <sub>IL</sub>    |                                                                                   |      |     | 0.4  | V    |

| High-Level Input Voltage                                          | $V_{IH}$           |                                                                                   | 0.86 |     |      | ٧    |

| Low-Level Output Voltage                                          | V <sub>OL</sub>    | Open-drain, I <sub>OL</sub> = 20mA                                                |      |     | 0.4  | V    |

| Input Current Each I/O Pin                                        | I <sub>IN</sub>    | $V_{DD} = 3V \text{ to } 5.5V,$<br>0.1 × $V_{DD}$ < $V_{IN}$ < 0.9 × $V_{DD MAX}$ | -1   |     | 1    | μA   |

| SCL Clock Frequency                                               | f <sub>SCL</sub>   |                                                                                   | 0    |     | 1000 | kHz  |

| Pulse Width of Spikes that Must Be Suppressed by the Input Filter | t <sub>SP</sub>    |                                                                                   |      |     | 50   | ns   |

| Data Hold Time                                                    | t <sub>HDDAT</sub> |                                                                                   | 0    |     |      | ns   |

| Data Set-Up Time                                                  | t <sub>SUDAT</sub> |                                                                                   | 50   |     |      | ns   |

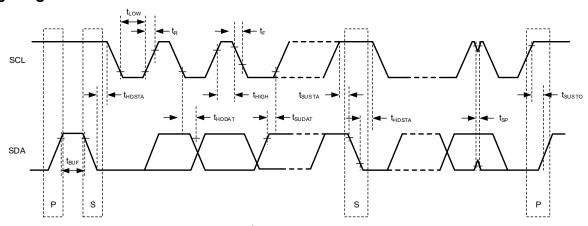

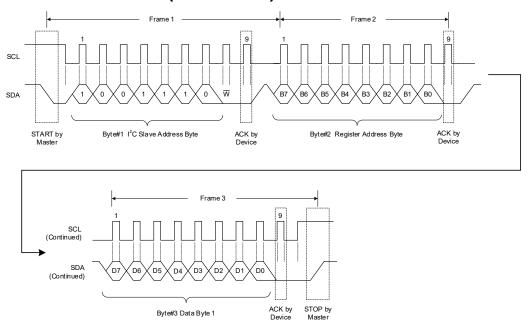

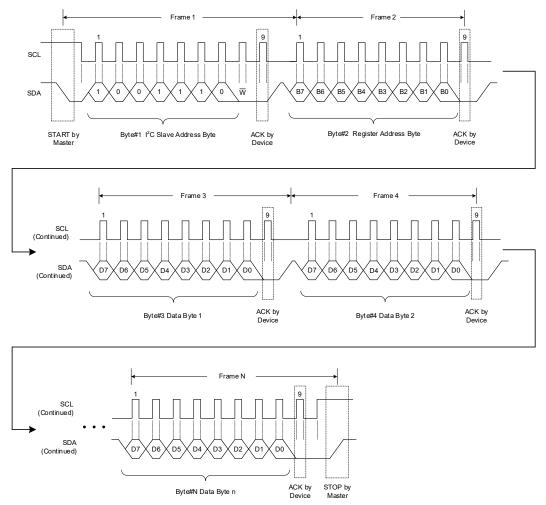

### **Timing Diagram**

Figure 2. I<sup>2</sup>C Waveform Information

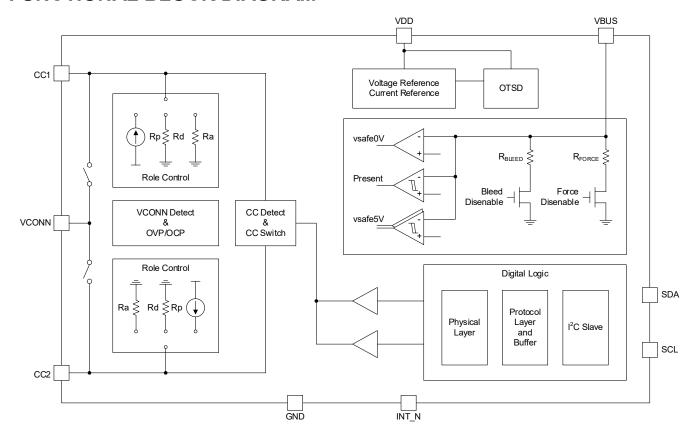

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 3. Block Diagram

#### **DETAILED DESCRIPTION**

The SGM795 acts as a USB Type-C Port Controller (TCPC), operating at the PD PHY level to oversee USB Type-C connectivity and Power Delivery (PD). It fulfills three primary functions pivotal to USB Type-C port functionality: power control of VBUS and VCONN, CC logic and detection, and USB PD message delivery.

Featuring a USB Type-C Port Controller Interface (TCPCI), the SGM795 seamlessly interfaces with the USB Type-C Port Manager (TCPM) within an Application Processor (AP) via the I<sup>2</sup>C interface. Utilizing the INT\_N signal, the SGM795 requests attention when necessary.

Integrated with CC logic and programmable Rp and Rd settings for each CC line, the SGM795 facilitates USB port attachment and detachment detection, role identification, cable orientation determination, and Type-C current detection/advertisement.

Equipped with a USB PD BMC physical layer and a portion of the protocol layer, the SGM795 manages the transmission and reception of USB PD messages, enabling diverse functionalities such as power negotiations and data role negotiations over the Type-C port. Operationally, the SGM795 receives messages from the TCPM, performs a 32-bit CRC calculation, encodes the message, and transmits it over the CC wire. Conversely, it detects SOP\* and validates packet integrity upon receiving data from the CC wire, automatically responds with a GoodCRC indication, and notifies the TCPM of received data by activating the interrupt signal (INT N).

Furthermore, the SGM795 implements VBUS detection and internal VBUS discharge to comply with USB Type-C port standards. It integrates a VCONN power switch for active cable management, detecting VCONN over-voltage, over-current and over-temperature conditions. Additionally, it provides mechanisms for handling Built-In Self Test (BIST) mode in accordance with defined standards.

#### **Configuration Channel (CC) Detection**

In the USB Type-C solution, the CC1 and CC2 pins on the connector play a crucial role in establishing and managing the source-to-sink connection. These pins are utilized for a variety of functions including attachment and detachment detection, role identification, cable orientation determination, Type-C

current detection/advertisement, and discovery of alternate and accessory modes.

The SGM795 incorporates multiple comparators designed to ascertain the voltage values present on the CC1 and CC2 pins corresponding to different source (SRC) or sink (SNK) roles. Upon detecting a change on the CC1 or CC2 wires, the SGM795 promptly updates the CC\_STATUS register, signaling the connection result and the current CC state. To ensure accurate reporting of CC line states, the SGM795 employs debounce filtering for a duration of  $t_{TCPC}$  filter. Subsequently, the assertion of the interrupt signal INT\_N indicates a state change to the TCPM.

This status information furnishes the TCPM with all necessary data to determine the attachment and detachment status of the cable, empowering seamless management of the USB Type-C connection.

#### **DRP Toggle**

The SGM795 offers the flexibility to perform autonomous or manual DRP toggles, catering to diverse operational requirements. In autonomous DRP toggles, the SGM795 seamlessly executes DRP toggling between SRC and SNK roles. This autonomous toggling involves dynamic switching between Rd and Rp configurations, with programmable DRP period and duty cycle settings.

To enable autonomous DRP toggling, the ROLE\_CONTROL register must be programmed with either 0x4A or 0x45, indicating DRP autonomous toggling mode, and the starting value of DRP. Notably, the SGM795 initiates DRP toggling only upon receiving the Look4Connection command from the TCPM via the COMMAND register.

On the other hand, manual DRP control grants complete authority to the TCPM, enabling direct manipulation of the Rp/Rd configurations as per specific requirements. To exercise manual control, the TCPM toggles between writing 0x0A and 0x05 to the ROLE\_CONTROL register, signaling changes in the CC1/CC2 values. This control mechanism is utilized when the SGM795 is operating solely as SRC or SNK, or when a connection has been detected via DRP toggling, but the TCPM intends to initiate Try.SRC or Try.SNK operations.

#### **USB PD BMC PHY**

The SGM795 sends and receives messages constructed in the TCPM and places them on the CC connections. It should be noted that the SGM795 incorporates the entire USB PD Physical Layer, utilizing BMC encoding, and also a portion of the protocol layer. Specifically, the USB PD Physical Layer comprises a pair of transmitters and receivers that communicate via a single signal wire (CC), operating exclusively in a half-duplex mode. This configuration ensures efficient and reliable data transmission across the channel. The SGM795 implements the following portions of the USB PD protocol layer:

- CRC Receive Timer.

- Retry Counter.

- Message ID is not checked in the SGM795 when a non-GoodCRC message is received. Retried messages that are received are passed to the TCPM via I<sup>2</sup>C.

- A message transmission is considered successful after receiving a GoodCRC response with the matching Message ID and SOP type.

- Way of discard message when asynchronous message is received.

- BIST handing as follows: Each incoming BIST message is responded to with GoodCRC without passing to the policy engine. The SGM795 provides the mechanism to send BIST continuous carrier mode 2 message for t<sub>BistContMode</sub>.

#### **VBUS Detection**

The SGM795 boasts the capability to monitor the VBUS voltage level for various states including VBUS present, vsafe5V, or vsafe0V. When VBUS rises above 4V, the SGM795 promptly reports VBUS present, whereas indicating VBUS absent when the voltage falls below 3.5V. Furthermore, when VBUS drops below 0.8V, the SGM795 reports that VBUS is at vsafe0V.

For precise vsafe5V detection, the SGM795 incorporates 4.75V and 5.5V detection thresholds in a vendor-defined register. This enables the TCPM to read the register and determine whether the VBUS voltage falls within the vsafe5V range as specified in the PD

specification. In accordance with this detection, the SGM795 generates an interrupt when the VBUS voltage deviates from the vsafe5V threshold, whether lower or higher.

It's important to note that the VBUS detection circuit is enabled by default but can be disabled by the TCPM as needed, allowing for flexible management of VBUS monitoring functionalities.

#### **VBUS Discharge**

The SGM795 incorporates an internal force discharge circuit and a bleed discharge circuit, both controllable by the TCPM, to facilitate VBUS discharge, eliminating the need for external VBUS discharge if the PD standard requirements are met. The force discharge feature employs a higher current discharge to swiftly bring VBUS below vsafe0V upon detecting a disconnection event as signaled by the TCPM. If the TCPM requires confirmation of VBUS discharge completion, it can access the EXTENDED\_STATUS register for this information.

In addition to force discharge, the SGM795 also integrates a bleed discharge mechanism, which utilizes a lower current discharge to efficiently deplete the bulk capacitance present on VBUS. This combination of force and bleed discharge circuits offers comprehensive VBUS discharge functionality, ensuring compliance with PD standard requirements while optimizing system performance.

#### **VCONN Switch and Protections**

VCONN is an essential requirement for active cables and e-markers in the USB Type-C ecosystem. To fulfill this requirement, the SGM795 integrates a 3W VCONN switch, which is under the control of the TCPM. This switch applies voltage to the VCONN pin connected to the selected CC pin, as indicated by the value of the PLUG\_ORIENT bit in the TCPC\_CONTROL register. By default, the switch is disabled and can be activated by setting the ENABLE\_VCONN bit in the POWER\_CONTROL register. Subsequently, the TCPM can verify the application of VCONN voltage on the CC line by querying the VCONN\_PRESENT status.

Before enabling the VCONN switch, it is imperative that the TCPM verifies the voltage on the VCONN pin to ensure that it is within a valid range. Premature removal of voltage from the VCONN pin before disabling the VCONN switch can trigger a VCONN fault condition, resulting in the clearing of the ENABLE\_VCONN bit.

To maintain safety standards, the SGM795 incorporates VCONN over-voltage protection and programmable over-current protection mechanisms to prevent false operation conditions. Furthermore, the SGM795 detects over-temperature conditions to prevent damage. In the event of any fault, the protection mechanisms promptly respond by setting the FAULT STATUS bit and disabling the VCONN switch.

#### Interrupts

The INT\_N pin of the SGM795 is utilized to communicate events to software running on the TCPM.

After an event occurs, the SGM795 sets the corresponding bit in the ALERT registers and activates the INT\_N pin low to notify the TCPM that an unmasked status change has occurred. These bits remain asserted until the TCPM writes a logical 1 to clear them.

In the event that the FAULT flag is triggered in the ALERT register, the TCPM is required to initially access the FAULT\_STATUS register to determine the reason for the fault. Following this determination, the TCPM clears the FAULT bit by writing a logical 1 to the

respective FAULT bit position. Subsequently, the TCPM writes a logical 1 to the FAULT bit of ALERT register after clearing all bits in the FAULT STATUS register.

#### **Dead Battery Mode**

The SGM795 provides support for dead battery mode, activated when conditions such as low battery power or the absence of VDD occurs, resulting in the inability to sustain communication over USB Type-C. In dead battery mode, the SGM795 applies Rd to both CC1 and CC2 pins and adheres to all sink rules.

When the SGM795 is connected to a source, it operates as a sink, facilitating the provision of vbus power from the source. This enables the recharging of the battery to restore it to an operational level, ensuring continuous functionality and operational continuity even in challenging power conditions.

## Type-C Port Controller (TCPC) Interface uses I<sup>2</sup>C Protocol

The TCPC Interface (TCPCI) is the interface between a Type-C port manager and a Type-C port controller. SGM795 communicates with TCPM via I<sup>2</sup>C bus.

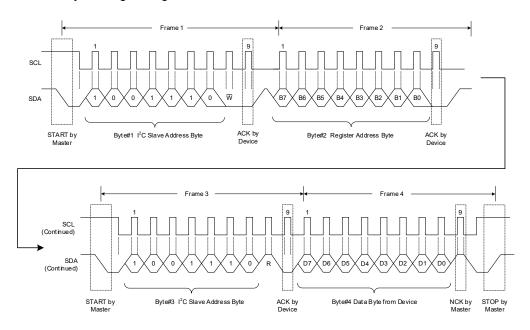

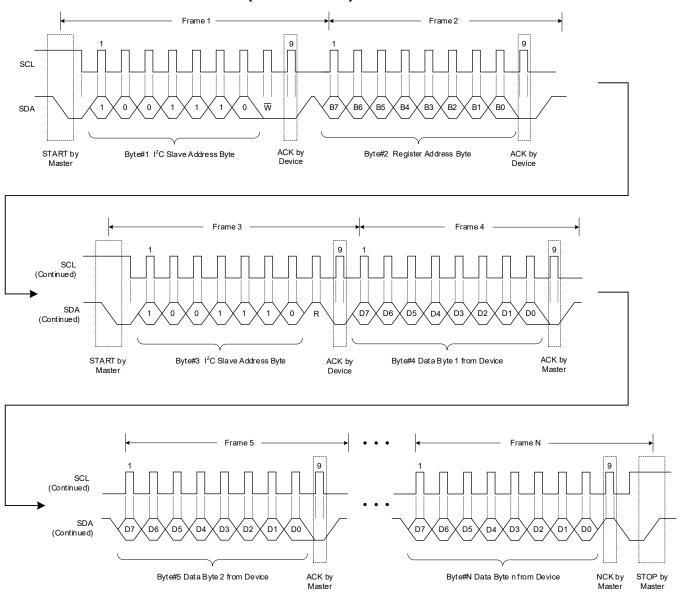

#### **Read and Write Function**

The I<sup>2</sup>C interface bus provides TCPM access to both read and write operations on the SGM795 and necessitates an external pull-up resistor. Below are the I<sup>2</sup>C timing diagrams.

Figure 4. Read Single Byte of Data from Register

Figure 5. Read N Bytes of Data from Registers

Figure 6. Write Single Byte of Data to Register

Figure 7. Write N Bytes of Data to Registers

#### **REGISTER MAPS**

#### **Summary Register Map**

Table 1 lists the SGM795 registers.

Table 1. SGM795 Registers

| ADDRESS | REGISTER NAME                        | DEFAULT | TYPE     |

|---------|--------------------------------------|---------|----------|

| 0x00h   | VENDOR_ID Register                   | 0x7E    | R        |

| 0x01h   | VENDOR_ID Register                   | 0x37    | R        |

| 0x02h   | PRODUCT_ID Register                  | 0x95    | R        |

| 0x03h   | PRODUCT_ID Register                  | 0x07    | R        |

| 0x04h   | DEVICE_ID Register                   | 0x20    | R        |

| 0x05h   | DEVICE_ID Register                   | 0x10    | R        |

| 0x06h   | USBTYPEC_REV Register                | 0x23    | R        |

| 0x08h   | USBPD_VER Register                   | 0x10    | R        |

| 0x09h   | USBPD_REV Register                   | 0x32    | R        |

| 0x0A    | PDIF_VER Register                    | 0x13    | R        |

| 0x0B    | PDIF_REV Register                    | 0x20    | R        |

| 0x10    | ALERT_L Register                     | 0x02    | R, R/W1C |

| 0x11    | ALERT_H Register                     | 0x02    | R, R/W1C |

| 0x12    | ALERT_L_MASK Register                | 0x7F    | R, R/W   |

| 0x13    | ALERT_H_MASK Register                | 0x26    | R, R/W   |

| 0x14    | POWER_STATUS_MASK Register           | 0x4E    | R, R/W   |

| 0x15    | FAULT_STATUS_MASK Register           | 0xFF    | R/W      |

| 0x16    | EXTENDED_STATUS_MASK Register        | 0x01    | R, R/W   |

| 0x19    | TCPC_CONTROL Register                | 0x00    | R, R/W   |

| 0x1A    | ROLE_CONTROL Register                | 0x0A    | R, R/W   |

| 0x1B    | FAULT_CONTROL Register               | 0x00    | R, R/W   |

| 0x1C    | POWER_CONTROL Register               | 0x00    | R, R/W   |

| 0x1D    | CC_STATUS Register                   | 0x00    | R        |

| 0x1E    | POWER_STATUS Register                | 0x00    | R        |

| 0x1F    | FAULT_STATUS Register                | 0x80    | R, R/W1C |

| 0x20    | EXTENDED_STATUS Register             | 0x00    | R, R/W   |

| 0x23    | COMMAND Register                     | 0x00    | R/W      |

| 0x24    | DEVICE_CAPABILITIES_1L Register      | 0xB8    | R        |

| 0x25    | DEVICE_CAPABILITIES_1H Register      | 0x1A    | R        |

| 0x26    | DEVICE_CAPABILITIES_2L Register      | 0x35    | R        |

| 0x27    | DEVICE_CAPABILITIES_2H Register      | 0x00    | R        |

| 0x28    | STANDARD_INPUT_CAPABILITIES Register | 0x00    | R        |

| 0x29    |                                      |         | R        |

| 0x2E    | MESSAGE_HEADER_INFO Register         | 0x02    | R, R/W   |

| 0x2F    | RECETVE_DETECT Register              | 0x00    | R, R/W   |

| 0x30    | RX_BYTE_COUNT Register               | 0x00    | R        |

| 0x31    | RX_BUF_FRAME_TYPE Register           | 0x00    | R        |

| 0x32    | RX_BUF_HEADER_BYTE_0 Register        | 0x00    | R        |

| 0x33    | RX_BUF_HEADER_BYTE_1 Register        | 0x00    | R        |

| ADDRESS              | REGISTER NAME                             | DEFAULT | TYPE     |

|----------------------|-------------------------------------------|---------|----------|

| 0x34 ~ 0x4F          | RX_BUF_OBJx(1 ~ 7)_BYTE_x(0 ~ 3) Register | 0x00    | R        |

| 0x50                 | TX_BUF_FRAME_TYPE Register                | 0x00    | R, R/W   |

| 0x51                 | TX_BYTE_COUNT Register                    | 0x00    | R/W      |

| 0x52                 | 0x52 TX_BUF_HEADER_BYTE_0 Register 0x00   |         | R/W      |

| 0x53                 | TX_BUF_HEADER_BYTE_1 Register             | 0x00    | R/W      |

| 0x54 ~ 0x6F          | TX_BUF_OBJx(1 ~ 7)_BYTE_x(0 ~ 3) Register | 0x00    | R/W      |

| 0x90 SG_CTL Register |                                           | 0x40    | R, R/W   |

| 0x93                 | VCONOCP Register                          | 0x80    | R, R/W   |

| 0x97                 | SG_ST Register                            | 0x00    | R        |

| 0x98                 | 0x98 SG_INT Register                      |         | R, R/W1C |

| 0x99                 | 0x99 SG_INT_MASK Register                 |         | R, R/W   |

| 0x9B                 | SG_SHUTDOWN Register                      | 0x00    | R, R/W   |

| 0x9F                 | WAKE_UP Register                          | 0x80    | R, R/W   |

| 0xA0                 | 0xA0 SOFT_RESET Register                  |         | R, W     |

| 0xA2                 | 0xA2 TDRP Register 0x03                   |         | R, R/W   |

| 0xA3                 | DRP_DUTY_CTRL0 Register                   | 0x47    | R/W      |

| 0xA4                 | DRP_DUTY_CTRL1 Register                   | 0x01    | R/W      |

#### **Detailed Register Maps**

Bit Types: R: Read only R/W: Read/Write

R/W1C: Read/Write. Writing a '1' clears the bit. Writing a '0' has no effect.

7-bit I<sup>2</sup>C Slave Device Address: 0b1001 110 + R/W

**REG0x00: VENDOR\_ID Register [Reset = 0x7E]**

| BITS   | BIT NAME | DEFAULT   | TYPE | DESCRIPTION                                                             | RESET BY |

|--------|----------|-----------|------|-------------------------------------------------------------------------|----------|

| D[7:0] | VID[7:0] | 0111 1110 | R    | A unique 16-bit unsigned integer, representing the Vendor ID. Low byte. | N/A      |

REG0x01: VENDOR\_ID Register [Reset = 0x37]

| BITS   | BIT NAME  | DEFAULT   | TYPE | DESCRIPTION                                                              | RESET BY |

|--------|-----------|-----------|------|--------------------------------------------------------------------------|----------|

| D[7:0] | VID[15:8] | 0011 0111 | R    | A unique 16-bit unsigned integer, representing the Vendor ID. High byte. | N/A      |

REG0x02: PRODUCT\_ID Register [Reset = 0x95]

| BITS   | BIT NAME | DEFAULT   | TYPE | DESCRIPTION                                                                                       | RESET BY |

|--------|----------|-----------|------|---------------------------------------------------------------------------------------------------|----------|

| D[7:0] | PID[7:0] | 1001 0101 | R    | A unique 16-bit unsigned integer. Assigned uniquely by the Vendor to identify the TCPC. Low byte. | N/A      |

REG0x03: PRODUCT\_ID Register [Reset = 0x07]

| BITS   | BIT NAME  | DEFAULT   | TYPE | DESCRIPTION                                                                                        | RESET BY |

|--------|-----------|-----------|------|----------------------------------------------------------------------------------------------------|----------|

| D[7:0] | PID[15:8] | 0000 0111 | R    | A unique 16-bit unsigned integer. Assigned uniquely by the Vendor to identify the TCPC. High byte. | N/A      |

REG0x04: DEVICE\_ID Register [Reset = 0x20]

| BITS   | BIT NAME | DEFAULT   | TYPE | DESCRIPTION                                                                                               | RESET BY |

|--------|----------|-----------|------|-----------------------------------------------------------------------------------------------------------|----------|

| D[7:0] | DID[7:0] | 0010 0000 | R    | A unique 16-bit unsigned integer. Assigned by the Vendor to identify the version of the SGM795. Low byte. | N/A      |

**REG0x05: DEVICE\_ID Register [Reset = 0x10]**

| BITS   | BIT NAME  | DEFAULT   | TYPE | DESCRIPTION                                                                                                | RESET BY |

|--------|-----------|-----------|------|------------------------------------------------------------------------------------------------------------|----------|

| D[7:0] | DID[15:8] | 0001 0000 | R    | A unique 16-bit unsigned integer. Assigned by the Vendor to identify the version of the SGM795. High byte. | N/A      |

REG0x06: USBTYPEC\_REV Register [Reset = 0x23]

| BITS   | BIT NAME          | DEFAULT   | TYPE | DESCRIPTION                                          | RESET BY |

|--------|-------------------|-----------|------|------------------------------------------------------|----------|

| D[7:0] | USBTYPEC_REV[7:0] | 0010 0011 | R    | Byte 0 of a 16-bit USB Type-C Revision. Revision 2.3 | N/A      |

REG0x08: USBPD\_VER Register [Reset = 0x10]

| BITS   | BIT NAME       | DEFAULT   | TYPE | DESCRIPTION                                     | RESET BY |

|--------|----------------|-----------|------|-------------------------------------------------|----------|

| D[7:0] | USBPD_VER[7:0] | 0001 0000 | R    | Byte 0 of a 16-bit USB PD Version. Version 1.0. | N/A      |

REG0x09: USBPD REV Register [Reset = 0x32]

| BITS   | BIT NAME       | DEFAULT   | TYPE | DESCRIPTION                                       | RESET BY |

|--------|----------------|-----------|------|---------------------------------------------------|----------|

| D[7:0] | USBPD_REV[7:0] | 0011 0010 | R    | Byte 1 of a 16-bit USB PD Revision. Revision 3.2. | N/A      |

REG0x0A: PDIF\_VER Register [Reset = 0x13]

| BITS   | BIT NAME      | DEFAULT   | TYPE | DESCRIPTION                                                 | RESET BY |

|--------|---------------|-----------|------|-------------------------------------------------------------|----------|

| D[7:0] | PDIF_VER[7:0] | 0001 0011 | R    | Byte 0 of a 16-bit PD Interface (TCPC) Version. Version 1.3 | N/A      |

REG0x0B: PDIF\_REV Register [Reset = 0x20]

| BITS   | BIT NAME      | DEFAULT   | TYPE | DESCRIPTION                                                    | RESET BY |

|--------|---------------|-----------|------|----------------------------------------------------------------|----------|

| D[7:0] | PDIF_REV[7:0] | 0010 0000 | R    | Byte 1 of a 16-bit PD Interface (TCPC). Revision. Revision 2.0 | N/A      |

REG0x10: ALERT\_L Register [Reset = 0x02]

| BITS | BIT NAME             | DEFAULT | TYPE  | DESCRIPTION                                                                                                                                                                                              | RESET BY   |

|------|----------------------|---------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| D[7] | ALARM_VBUS_VOLTAGE_H | 0       | R     | Not support.                                                                                                                                                                                             | N/A        |

| D[6] | TX_SUCCESS           | 0       | R/W1C | 0 = Cleared R/W1C 1 = Reset or the SOP* message is successfully transmistted.                                                                                                                            |            |

| D[5] | TX_DISCARD           | 0       | R/W1C | 0 = Cleared 1 = Reset or SOP* message transmission is not sent due to an incoming receive message.                                                                                                       |            |

| D[4] | TX_FAIL              | 0       | R/W1C | 0 = Cleared<br>1 = the SOP* message is successfully transmistted. No<br>GoodCRC response is received on SOP* message<br>transmission.                                                                    | SOFT_RESET |

| D[3] | RX_HARD_RESET        | 0       | R/W1C | 0 = Cleared<br>1 = Received Hard Reset message                                                                                                                                                           | SOFT_RESET |

| D[2] | RX_SOP_MSG_STATUS    | 0       | R/W1C | 0 = Cleared<br>1 = Receive buffer register changed<br>Note that RX_BYTE_COUNT being zero does not set<br>this bit.                                                                                       | SOFT_RESET |

| D[1] | POWER_STATUS         | 1       | R/W1C | 0 = Cleared<br>1 = Port status changed<br>The SGM795 will assert this bit after power-up due to a<br>previous change of the TCPC_INITIAL bit in the<br>POWER_STATUS register                             | SOFT_RESET |

| D[0] | CC_STATUS            | 0       | R/W1C | 0 = Cleared 1 = CC status changed SGM795 shall not assert this bit when the LOOKING4CONNECTION bit of CC_STATUS register changes state if EN_LOOKING4CON_ALERT bit of TCPC_CONTROL register is set to 0. | SOFT_RESET |

**REG0x11: ALERT\_H Register [Reset = 0x02]**

| BITS | BIT NAME             | DEFAULT | TYPE  | DESCRIPTION                                                                                                                                                                                                           | RESET BY   |  |  |  |

|------|----------------------|---------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|

| D[7] | VENDOR_DEFINED_ALERT | 0       | R/W1C | 0 = Cleared<br>1 = A vendor defined alert that is unmasked has<br>been detected. Defined in the SG_INT registers.<br>TCPM SW should first clear the appropriate bit in<br>SG_INT register before clearing this field. | SOFT_RESET |  |  |  |

| D[6] | ALERT_EXTENDED       | 0       | R     | Not support.                                                                                                                                                                                                          | N/A        |  |  |  |

| D[5] | EXTENDED_STATUS      | 0       | R/W1C | 0 = Cleared<br>1 = Extended status changed                                                                                                                                                                            | SOFT_RESET |  |  |  |

| D[4] | BEGIN_SOP_MSG_STATUS | 0       | R     | Not support.                                                                                                                                                                                                          | N/A        |  |  |  |

| D[3] | VBUS_SINK_DISCNT     | 0       | R     | Not support.                                                                                                                                                                                                          | N/A        |  |  |  |

| D[2] | RXBUF_OVFLOW         | 0       | R/W1C | 0 = SGM795 Rx buffer is functioning properly.<br>1 = SGM795 Rx buffer has overflowed.                                                                                                                                 | SOFT_RESET |  |  |  |

| D[1] | FAULT                | 1       | R/W1C | 0 = No Fault. 1 = A Fault has occurred. Read the FAULT_STATUS register.                                                                                                                                               | SOFT_RESET |  |  |  |

| D[0] | ALARM_VBUS_VOLTAGE_L | 0       | R     | Not support.                                                                                                                                                                                                          | N/A        |  |  |  |

REG0x12: ALERT\_L\_MASK Register [Reset = 0x7F]

| ILCOX | IZ. ALLINI_L_MAON NOGIS | tei lixeaet |      |                                                |            |

|-------|-------------------------|-------------|------|------------------------------------------------|------------|

| BITS  | BIT NAME                | DEFAULT     | TYPE | DESCRIPTION                                    | RESET BY   |

| D[7]  | M_ALARM_VBUS_VOLTAGE_H  | 0           | R    | Not support.                                   | N/A        |

| D[6]  | M_TX_SUCCESS            | 1           | R/W  | 0 = Interrupt masked<br>1 = Interrupt unmasked | SOFT_RESET |

| D[5]  | M_TX_DISCARD            | 1           | R/W  | 0 = Interrupt masked<br>1 = Interrupt unmasked | SOFT_RESET |

| D[4]  | M_TX_FAIL               | 1           | R/W  | 0 = Interrupt masked<br>1 = Interrupt unmasked | SOFT_RESET |

| D[3]  | M_RX_HARD_RESET         | 1           | R/W  | 0 = Interrupt masked<br>1 = Interrupt unmasked | SOFT_RESET |

| D[2]  | M_RX_SOP_MSG_STATUS     | 1           | R/W  | 0 = Interrupt masked<br>1 = Interrupt unmasked | SOFT_RESET |

| D[1]  | M_POWER_STATUS          | 1           | R/W  | 0 = Interrupt masked<br>1 = Interrupt unmasked | SOFT_RESET |

| D[0]  | M_CC_STATUS             | 1           | R/W  | 0 = Interrupt masked<br>1 = Interrupt unmasked | SOFT_RESET |

REG0x13: ALERT\_H\_MASK Register [Reset = 0x26]

| - 1 - 0 - 7 - | 1017122111_11_111/1011 110glo | to. L. tooot |      |                                                |            |

|---------------|-------------------------------|--------------|------|------------------------------------------------|------------|

| BITS          | BIT NAME                      | DEFAULT      | TYPE | DESCRIPTION                                    | RESET BY   |

| D[7]          | M_VENDOR_INT_STATUS           | 0            | R/W  | 0 = Interrupt masked<br>1 = Interrupt unmasked | SOFT_RESET |

| D[6]          | ALERT_EXTENDED_MASK           | 0            | R    | Not support.                                   | N/A        |

| D[5]          | M_EXTENDED_STATUS             | 1            | R/W  | 0 = Interrupt masked<br>1 = Interrupt unmasked | SOFT_RESET |

| D[4]          | BEGIN_SOP_MSG_STATUS_MASK     | 0            | R    | Not support.                                   | N/A        |

| D[3]          | M_VBUS_SINK_DISCNT            | 0            | R    | Not support.                                   | N/A        |

| D[2]          | M_RXBUF_OVFLOW                | 1            | R/W  | 0 = Interrupt masked<br>1 = Interrupt unmasked | SOFT_RESET |

| D[1]          | M_FAULT                       | 1            | R/W  | 0 = Interrupt masked<br>1 = Interrupt unmasked | SOFT_RESET |

| D[0]          | M_ALARM_VBUS_VOLTAGE_L        | 0            | R    | Not support.                                   | N/A        |

REG0x14: POWER\_STATUS\_MASK Register [Reset = 0x4E]

| BITS | BIT NAME             | DEFAULT | TYPE | DESCRIPTION                                    | RESET BY   |

|------|----------------------|---------|------|------------------------------------------------|------------|

| D[7] | DBG_ACC_CONNECT_MASK | 0       | R/W  | 0 = Interrupt masked<br>1 = Interrupt unmasked | SOFT_RESET |

| D[6] | M_TCPC_INITIAL       | 1       | R/W  | 0 = Interrupt masked<br>1 = Interrupt unmasked | SOFT_RESET |

| D[5] | M_SRC_HV             | 0       | R    | Not support.                                   | N/A        |

| D[4] | M_SRC_VBUS           | 0       | R    | Not support.                                   | N/A        |

| D[3] | M_VBUS_DET_EN        | 1       | R/W  | 0 = Interrupt masked<br>1 = Interrupt unmasked | SOFT_RESET |

| D[2] | M_VBUS_PRESENT       | 1       | R/W  | 0 = Interrupt masked<br>1 = Interrupt unmasked | SOFT_RESET |

| D[1] | M_VCONN_PRESENT      | 1       | R/W  | 0 = Interrupt masked<br>1 = Interrupt unmasked | SOFT_RESET |

| D[0] | M_SINK_VBUS          | 0       | R    | Not support.                                   | N/A        |

REG0x15: FAULT\_STATUS\_MASK Register [Reset = 0xFF]

| BITS | BIT NAME              | DEFAULT | TYPE | DESCRIPTION                                                                             | RESET BY   |

|------|-----------------------|---------|------|-----------------------------------------------------------------------------------------|------------|

| D[7] | M_ALL_REGISTERS_RESET | 1       | R/W  | 0 = Interrupt masked<br>1 = Interrupt unmasked                                          | SOFT_RESET |

| D[6] | M_FORCE_OFF_VBUS      | 1       | R/W  | 0 = Interrupt masked<br>1 = Interrupt unmasked<br>This field has no meaning for SGM795. | SOFT_RESET |

| D[5] | M_AUTO_DISC_FAIL      | 1       | R/W  | 0 = Interrupt masked<br>1 = Interrupt unmasked<br>This field has no meaning for SGM795. | SOFT_RESET |

| D[4] | M_FORCE_DISC_FAIL     | 1       | R/W  | 0 = Interrupt masked<br>1 = Interrupt unmasked                                          | SOFT_RESET |

| D[3] | M_VBUS_OC             | 1       | R/W  | 0 = Interrupt masked<br>1 = Interrupt unmasked<br>This field has no meaning for SGM795. | SOFT_RESET |

| D[2] | M_VBUS_OV             | 1       | R/W  | 0 = Interrupt masked<br>1 = Interrupt unmasked<br>This field has no meaning for SGM795. | SOFT_RESET |

| D[1] | M_VCON_OC             | 1       | R/W  | 0 = Interrupt masked<br>1 = Interrupt unmasked                                          | SOFT_RESET |

| D[0] | M_I2C_ERROR           | 1       | R/W  | 0 = Interrupt masked<br>1 = Interrupt unmasked                                          | SOFT_RESET |

REG0x16: EXTENDED\_STATUS\_MASK Register [Reset = 0x01]

|        | _          | _       |      |                                                |            |

|--------|------------|---------|------|------------------------------------------------|------------|

| BITS   | BIT NAME   | DEFAULT | TYPE | DESCRIPTION                                    | RESET BY   |

| D[7:1] | RESERVED   | 0       | R    | Reserved                                       | N/A        |

| D[0]   | M_VSAFE_0V | 1       | R/W  | 0 = Interrupt masked<br>1 = Interrupt unmasked | SOFT_RESET |

**REG0x19: TCPC\_CONTROL Register [Reset = 0x00]**

| - 1    | 13. 101 0_00N11K0E K | egiotoi [i |      | 021001                                                                                                                                                                                                                                             |            |

|--------|----------------------|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| BITS   | BIT NAME             | DEFAULT    | TYPE | DESCRIPTION                                                                                                                                                                                                                                        | RESET BY   |

| D[7]   | EN_SMBUS_PEC         | 0          | R    | Not support.                                                                                                                                                                                                                                       | N/A        |

| D[6]   | EN_LOOKING4CON_ALERT | 0          | R/W  | 0 = Disable the CC_STATUS bit assertion of ALERT_L register when LOOKING4CONNECTION bit of CC_STATUS register changes. 1 = Enable the CC_STATUS bit assertion of ALERT_L register when LOOKING4CONNECTION bit of CC_STATUS register changes.       | SOFT_RESET |

| D[5]   | EN_WD_TIMER          | 0          | R    | Not support.                                                                                                                                                                                                                                       | N/A        |

| D[4]   | DEBUG_ACC_CTRL       | 0          | R    | Not support.                                                                                                                                                                                                                                       | N/A        |

| D[3:2] | I2C_CK_STRETCH[1:0]  | 00         | R    | Not support.                                                                                                                                                                                                                                       | N/A        |

| D[1]   | BIST_TEST_MODE       | 0          | R/W  | 0 = Normal Operation. RECEIVE_DETECT-enabled messages passed to TCPM via alert. 1 = BIST Test Mode. RECEIVE_DETECT-triggered messages generate GoodCRC response but not reach TCPM via alert.                                                      | SOFT_RESET |

| D[0]   | PLUG_ORIENT          | 0          | R/W  | 0 = If VCONN is enabled, apply it to the CC2 pin. If PD messaging is enabled, monitor the CC1 pin for BMC communications. 1 = If VCONN is enabled, apply it to the CC1 pin. If PD messaging is enabled, monitor the CC2 pin for BMC communications | SOFT_RESET |

REG0x1A: ROLE\_CONTROL Register [Reset = 0x0A]

| IVECOX | NEGOX IA. NOEE_CONTNOE Neglister [Neset - 0X0A] |         |      |                                                                                 |            |  |  |  |  |

|--------|-------------------------------------------------|---------|------|---------------------------------------------------------------------------------|------------|--|--|--|--|

| BITS   | BIT NAME                                        | DEFAULT | TYPE | DESCRIPTION                                                                     | RESET BY   |  |  |  |  |

| D[7]   | RESERVED                                        | 0       | R    | Reserved                                                                        | N/A        |  |  |  |  |

| D[6]   | EN_DRP                                          | 0       | R/W  | 0 = No DRP. Bits [3:0] determine the settings of Rp, Rd and Ra.<br>1 = DRP      | SOFT_RESET |  |  |  |  |

| D[5:4] | RP_VALUE[1:0]                                   | 00      | R/W  | 00 = Rp<br>01 = Rp 1.5A<br>10 = Rp 3.0A<br>11 = Reserved                        | SOFT_RESET |  |  |  |  |

| D[3:2] | CC2[1:0]                                        | 10      | R/W  | 00 = Ra<br>01 = Rp (Use Rp definition in RP_VALUE[1:0])<br>10 = Rd<br>11 = Open | SOFT_RESET |  |  |  |  |

| D[1:0] | CC1[1:0]                                        | 10      | R/W  | 00 = Ra<br>01 = Rp (Use Rp definition in RP_VALUE[1:0])<br>10 = Rd<br>11 = Open | SOFT_RESET |  |  |  |  |

**REG0x1B: FAULT\_CONTROL Register [Reset = 0x00]**

|        | the optimization of the state o |         |      |                                                                                                                                                                                       |            |  |  |  |  |  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|--|--|

| BITS   | BIT NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DEFAULT | TYPE | DESCRIPTION                                                                                                                                                                           | RESET BY   |  |  |  |  |  |

| D[7:5] | RESERVED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 000     | R    | Reserved                                                                                                                                                                              | N/A        |  |  |  |  |  |

| D[4]   | DIS_FORCE_OFF_VBUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0       | R    | Not support.                                                                                                                                                                          | N/A        |  |  |  |  |  |

| D[3]   | DIS_VBUS_DISC_FAULT_TIMER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0       | R/W  | 0 = VBUS discharge fault detection timer enabled<br>1 = VBUS discharge fault detection timer disabled<br>This enables the timers for FORCE_DISC_FAIL bit of<br>FAULT_STATUS register. | SOFT_RESET |  |  |  |  |  |