# SGM41544/SGM41544D High Input Voltage, 5A Single-Cell Battery Charger with NVDC Power Path Management

### **FEATURES**

- 3.9V to 14V Operating Input Voltage Range

- Up to 22V Sustainable Voltage

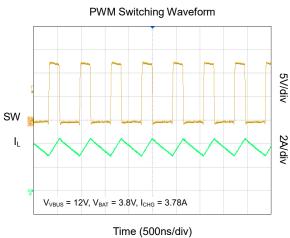

- High Efficiency, 1.5MHz, Synchronous Buck Charger

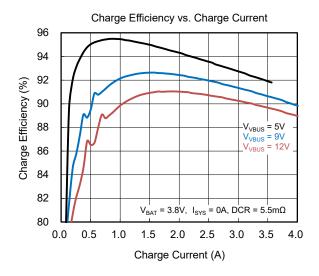

- 95.4% Charge Efficiency at 1A from 5V Input

- 92.6% Charge Efficiency at 1.5A from 9V Input

- Optimized for USB Voltage Input (9V/12V)

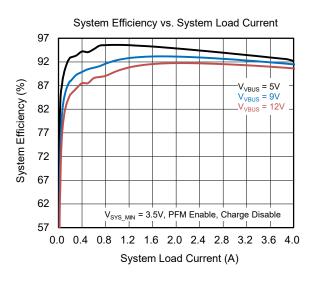

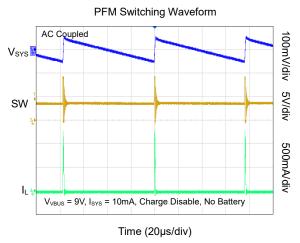

- Selectable PFM Mode for Light Load Efficiency

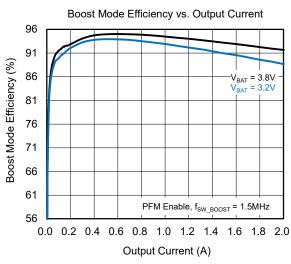

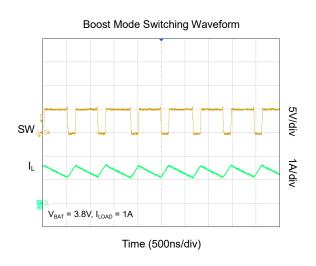

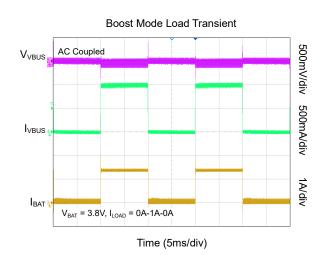

- USB On-The-Go (OTG) Support (Boost Mode)

- Boost Converter with up to 2.45A Output

- Boost Efficiency of 94.8% at 0.5A and 94.5% at 1A

- Accurate Hiccup Mode Over-Current Protection

- Output Short-Circuit Protection

- Selectable PFM Mode for Light Load Operations

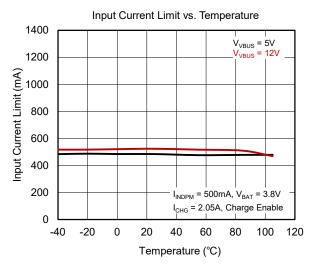

- Programmable Input Current Limit and Dynamic Power Management (IINDPM, 100mA to 3.25A with 50mA Resolution) to Support USB 2.0 and USB 3.0 Standards and High Voltage Adaptors

- Maximum Power Tracking by Programmable Input Voltage Limit (VINDPM) with Selectable Offset

- VINDPM Tracking of Battery Voltage

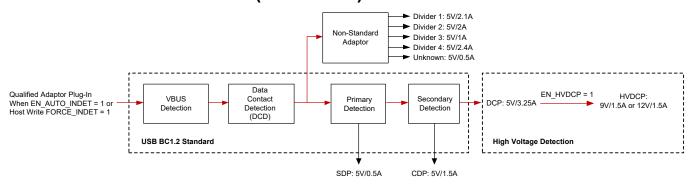

- Auto Detect USB BC1.2, SDP, CDP, DCP and Non-Standard Adaptors

- High Battery Discharge Efficiency with 17mΩ Switch,

Battery Discharge MOSFET up to 12A

- Input Current Optimizer (ICO) to Maximize Adaptor

Output Current without Overloading

- Integrated ADC for System Monitor

- Narrow Voltage DC (NVDC) Power Path Management

- Instant-On with No or Highly Depleted Battery

- Ideal Diode Operation in Battery Supplement Mode

- Ship Mode, Wake-Up and Full System Reset Capability by Battery FET Control

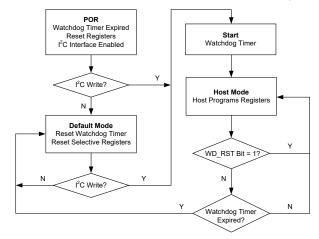

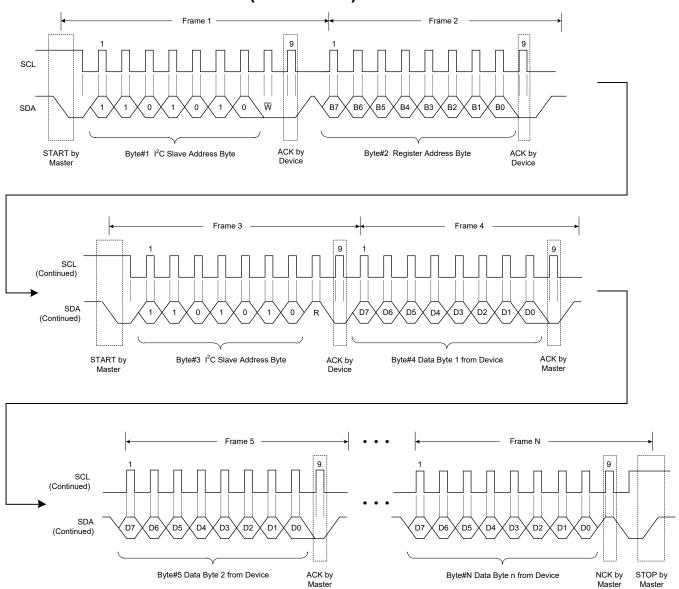

- Flexible Autonomous and I<sup>2</sup>C Operation Modes for Optimal System Performance

- Fully Integrated Switches, Current Sense and IR Compensation

- 4µA Ship Mode Low Battery Leakage Current

- High Accuracy

- ±0.5% Charge Voltage Regulation

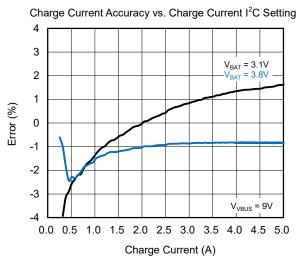

- ±3% Charge Current Regulation at 1.792A

- ±5% Input Current Regulation at 0.9A

- Safety

- Battery Temperature Sensing (Charge/Boost Modes)

- Thermal Regulation and Thermal Shutdown

- Input Under-Voltage Lockout (UVLO)

- Input Over-Voltage (ACOV) Protection

### **APPLICATIONS**

Smart Phones, EPOS

Portable Internet Devices and Accessory

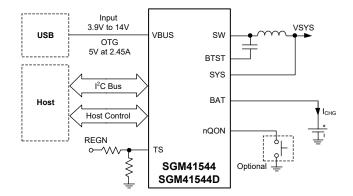

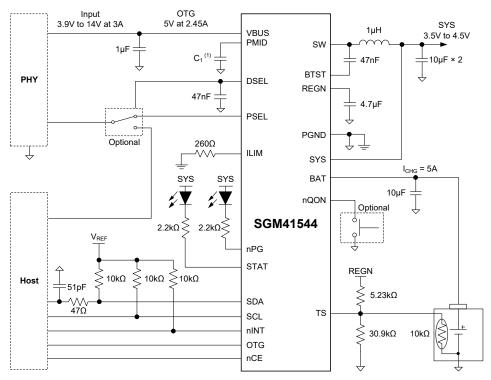

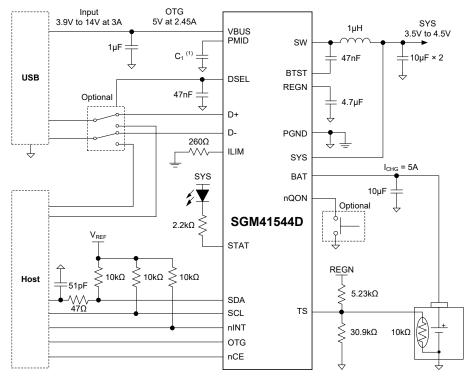

### SIMPLIFIED SCHEMATIC

### **GENERAL DESCRIPTION**

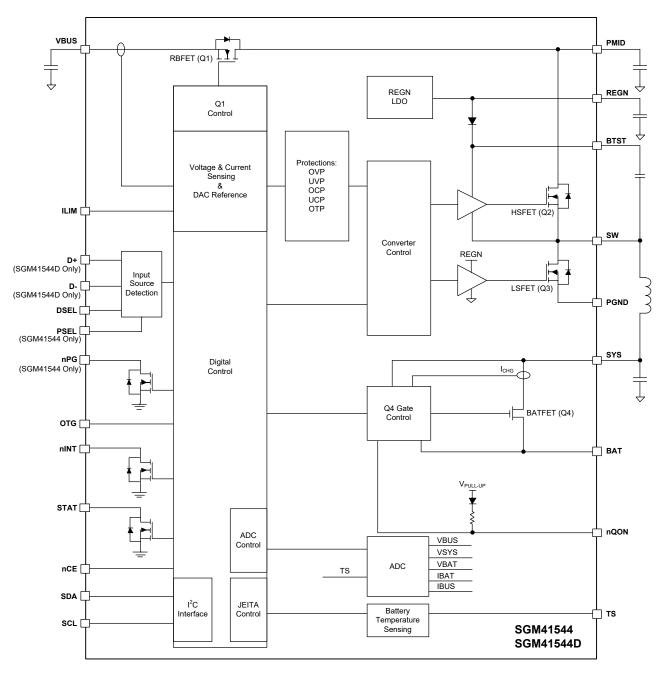

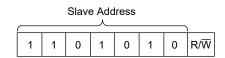

The SGM41544/SGM41544D are battery chargers and system power path management devices with integrated converter and power switches for using with single-cell Li-lon or Li-polymer batteries. This highly integrated 5A device is capable of fast charging and supports a wide input voltage range suitable for smart phones, tablets and portable systems. I<sup>2</sup>C programming makes it a very flexible powering and charger design solution.

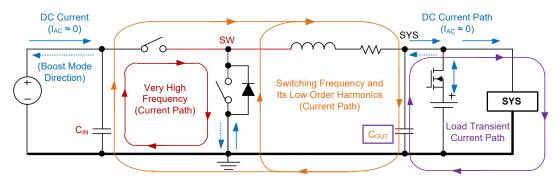

The devices include four main power switches: input reverse blocking FET (RBFET, Q1), high-side switching FET for Buck or Boost mode (HSFET, Q2), low-side switching FET for Buck or Boost mode (LSFET, Q3) and battery FET that controls the interconnection of the system and battery (BATFET, Q4). The bootstrap diode for the high-side gate driving is also integrated. The internal power path has a very low impedance that reduces the charging time and maximizes the battery discharge efficiency. Moreover, the input voltage and current regulations provide maximum charging power delivery to the battery with various types of input sources.

A wide range of input sources are supported, including standard USB hosts, charging ports and USB compliant high voltage adaptors. The default input current limit is automatically selected based on the built-in USB interface. This limit is determined by the detection circuit in the system (e.g. USB PHY). The SGM41544/SGM41544D are USB 2.0 and USB 3.0 power specifications compliant with input current and voltage regulation. It also meets USB On-The-Go (OTG) power rating specification and is capable of boosting the battery voltage to supply 5V on VBUS with 2.45A (MAX) current limit.

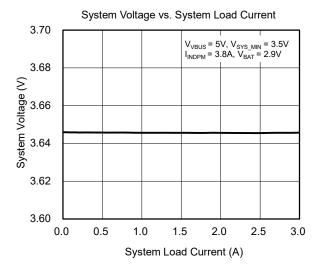

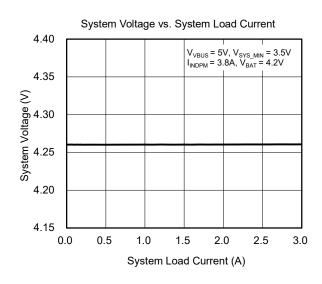

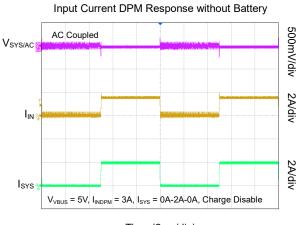

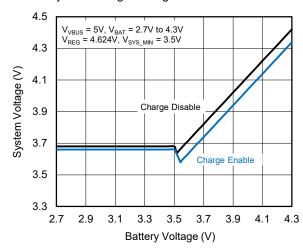

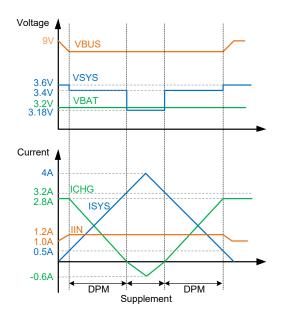

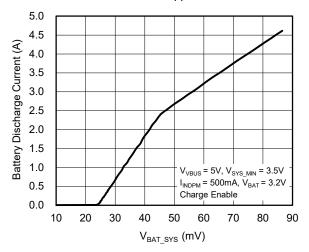

The system voltage is regulated slightly above the battery voltage by the power path management circuit and is kept above the programmable minimum system voltage (3.5V by default). Therefore, system power is maintained even if the battery is completely depleted or removed. Dynamic power management (DPM) feature is also included that automatically reduces the charge current if the input current

or voltage limit is reached. If the system load continues to increase after reduction of charge current down to zero, the power path management provides the deficit from battery by discharging battery to the system until the system power demand is fulfilled. This is called supplement mode, which prevents the input source from overloading.

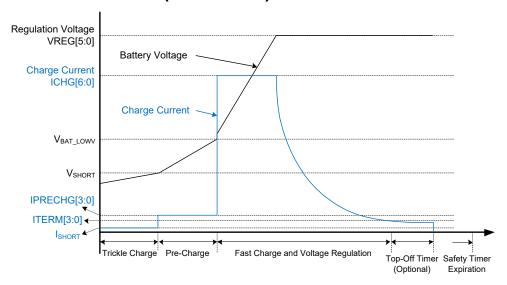

Starting and termination of a charging cycle can be accomplished without software control. The sensed battery voltage is used to decide for starting phase of charging in one of the three phases of charging cycle: pre-conditioning, constant current or constant voltage. When the charge current falls below a preset limit and the battery voltage is above recharge threshold, the charger function will automatically terminate and end the charging cycle. If the voltage of a charged battery falls below the recharge threshold, the charger begins another charging cycle.

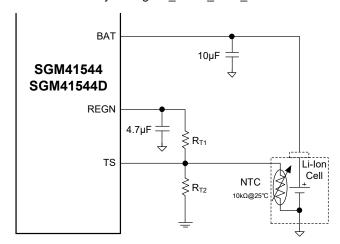

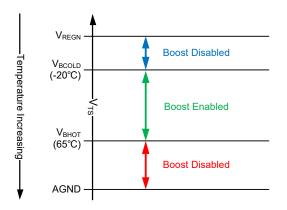

Several safety features are provided in the SGM41544/ SGM41544D such as over-voltage and over-current protections, battery temperature monitoring, charging safety timing, thermal shutdown and input UVLO. TS pin is connected to an NTC thermistor for battery temperature monitoring and protection in both charge and Boost modes according to JEITA profile. This device also features thermal regulation in which the charge current is reduced, if the junction temperature exceeds +120°C.

Charging status is reported by the STAT output and fault/status bits. A negative pulse is sent to the nINT output pin as soon as a fault occurs to notify the host. BATFET reset control is provided by nQON pin to exit ship mode or for a full system reset.

The SGM41544/SGM41544D provide a 7-bit analog-to-digital converter (ADC) for monitoring input current and charge current and input/battery/system/TS voltages.

The SGM41544/SGM41544D are available in a Green TQFN-4×4-24L package.

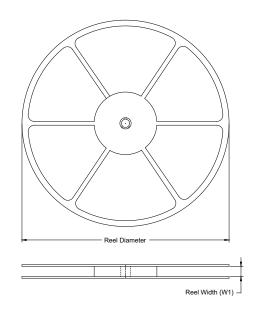

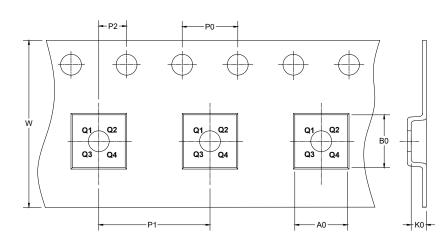

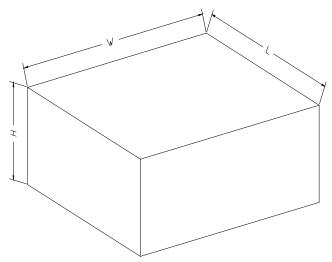

## PACKAGE/ORDERING INFORMATION

| MODEL     | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER  | PACKAGE<br>MARKING          | PACKING<br>OPTION   |

|-----------|------------------------|-----------------------------------|---------------------|-----------------------------|---------------------|

| SGM41544  | TQFN-4×4-24L           | -40°C to +85°C                    | SGM41544YTQF24G/TR  | SGM41544<br>YTQF24<br>XXXXX | Tape and Reel, 3000 |

| SGM41544D | TQFN-4×4-24L           | -40°C to +85°C                    | SGM41544DYTQF24G/TR | SGM0IT<br>YTQF24<br>XXXXX   | Tape and Reel, 3000 |

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### ABSOLUTE MAXIMUM RATINGS

| Voltage Range (with Respect to PGND)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| VBUS (Converter Not Switching)2V to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 22V                                |

| PMID (Converter Not Switching)0.3V to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                    |

| STAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                    |

| DSEL0.3V to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                    |

| BTST0.3V to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                    |

| SW2V to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                    |

| SW (Peak for 10ns Duration)3V to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                    |

| BAT, SYS (Converter Not Switching)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                    |

| SDA, SCL, nINT, OTG, REGN, TS, nCE, nQON0.3V to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                    |

| PSEL, nPG, D+, D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                    |

| BTST to SW0.3V to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |

| ILIM0.3V to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                    |

| Output Sink Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                    |

| nINT, STAT6mA (M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IAX)                               |

| DSEL2mA (M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | IAX)                               |

| Package Thermal Resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ,                                  |

| TQFN-4×4-24L, θ <sub>JA</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                    |

| TQT N-4^4-24L, UJA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | C/W                                |

| TQFN-4×4-24L, 0 <sub>JB</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | C/W                                |

| TQFN-4×4-24L, $\theta_{JB}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | C/W<br>C/W                         |

| TQFN-4×4-24L, θ <sub>JB</sub> 7.7°                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | C/W<br>C/W                         |

| TQFN-4×4-24L, $\theta_{JB}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | C/W<br>C/W<br>C/W                  |

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C/W<br>C/W<br>C/W<br>50°C          |

| $\begin{array}{llll} TQFN-4\times4-24L,\theta_{JB} & & & & & \\ TQFN-4\times4-24L,\theta_{JC(TOP)} & & & & & \\ TQFN-4\times4-24L,\theta_{JC(BOT)} & & & & & \\ Junction Temperature & & & & & \\ Storage Temperature Range & & & & & & \\ Lead Temperature (Soldering, 10s) & & & & \\ ESD Susceptibility & & & & & \\ ESD Susceptibility & & & & & \\ \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | C/W<br>C/W<br>C/W<br>50°C<br>50°C  |

| $\begin{array}{llll} TQFN-4\times4-24L,\theta_{JB} & & & & & \\ TQFN-4\times4-24L,\theta_{JC(TOP)} & & & & \\ TQFN-4\times4-24L,\theta_{JC(BOT)} & & & & \\ Junction Temperature & & & & \\ Storage Temperature Range & & & & & \\ Lead Temperature (Soldering, 10s) & & & & \\ ESD Susceptibility & & & & \\ HBM & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & \\ & & \\ & & \\ & \\ & \\ & .$ | C/W<br>C/W<br>50°C<br>50°C<br>60°C |

| $\begin{array}{llll} TQFN-4\times4-24L,\theta_{JB} & & & & & \\ TQFN-4\times4-24L,\theta_{JC(TOP)} & & & & & \\ TQFN-4\times4-24L,\theta_{JC(BOT)} & & & & & \\ Junction Temperature & & & & & \\ Storage Temperature Range & & & & & & \\ Lead Temperature (Soldering, 10s) & & & & \\ ESD Susceptibility & & & & & \\ ESD Susceptibility & & & & & \\ \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | C/W<br>C/W<br>50°C<br>50°C<br>60°C |

### NOTES:

- 1. For human body model (HBM), all pins comply with ANSI/ESDA/JEDEC JS-001 specifications.

- 2. For charged device model (CDM), all pins comply with ANSI/ESDA/JEDEC JS-002 specifications.

### RECOMMENDED OPERATING CONDITIONS

| Input Voltage Range, V <sub>IN</sub>     | 3.9V to 14V (3)     |

|------------------------------------------|---------------------|

| Input Current (VBUS), I <sub>IN</sub>    |                     |

| Output Current (SW), I <sub>SYS</sub>    | 5A (MAX)            |

| Battery Voltage, V <sub>BAT</sub>        | 4.624V (MAX)        |

| Fast Charging Current, IBAT              | 5A (MAX)            |

| Discharging Current with Internal MOSFET | Γ, I <sub>BAT</sub> |

| Continuous                               | Up to 6A            |

| Peak                                     | 12A (TYP)           |

| Operating Ambient Temperature Range      | 40°C to +85°C       |

#### NOTE:

3. The voltage spikes on either the BTST or SW pins should be less than the absolute maximum rating. Following the layout guidelines is helpful to minimize the switching noise.

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

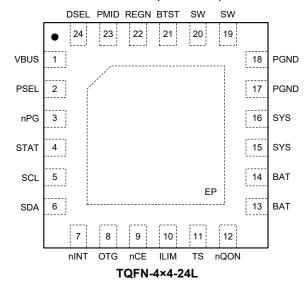

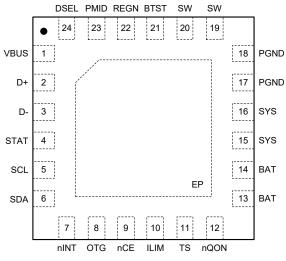

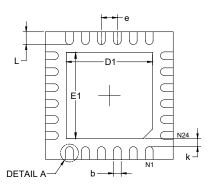

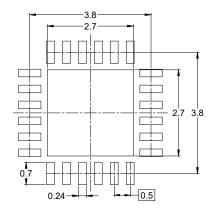

# **PIN CONFIGURATIONS**

### SGM41544 (TOP VIEW)

#### SGM41544D (TOP VIEW)

TQFN-4×4-24L

### PIN DESCRIPTION

| Р            | IN            |      |      |                                                                                                                                                                                                                                                                                                                                                                            |

|--------------|---------------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SGM<br>41544 | SGM<br>41544D | NAME | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                   |

| 1            | 1             | VBUS | Р    | Charger Input $(V_{IN})$ . The internal N-channel reverse blocking MOSFET (RBFET) is connected between VBUS and PMID pins. Place a $1\mu F$ ceramic capacitor from VBUS pin to PGND close to the device.                                                                                                                                                                   |

| 2            |               | PSEL | DI   | Power Source Selection Input. If PSEL is pulled high, the input current limit is set to 500mA (USB 2.0) and if it is pulled low, the limit is set to 2.4A (adaptor). When the I <sup>2</sup> C link to the host is established, the host can program a different input current limit value by writing to the IINDPM[5:0] register. (SGM41544 only)                         |

| _            | 2             | D+   | AIO  | Positive USB Data Line. D+/D- based USB device protocol detection and voltage of this pin can be set by DP_DAC[2:0] register. (SGM41544D only)                                                                                                                                                                                                                             |

| 3            | _             | nPG  | DO   | Open-Drain Active Low Input Power Good Indicator. Use a $10k\Omega$ pull-up to the logic high rail. A low state indicates a good input ( $V_{VBUS\_UVLOZ} < V_{VBUS} < V_{VBUS\_OV}$ , $V_{VBUS}$ is above sleep mode threshold, and $V_{VBUS} > V_{VBUSMIN}$ when $I_{BAD\_SRC} = 30$ mA). (SGM41544 only)                                                                |

| _            | 3             | D-   | AIO  | Negative USB Data Line. D+/D- based USB device protocol detection and voltage of this pin can be set by DM_DAC[2:0] register. (SGM41544D only)                                                                                                                                                                                                                             |

| 4            | 4             | STAT | DO   | Open-Drain Charge Status Output. Use a 10kΩ pull-up to the logic high rail (or an LED + a resistor). The STAT pin acts as follows: During charge: low (LED ON). Charge completed or charger in sleep mode: high (LED OFF). Charge suspended (in response to a fault): 1Hz, 50% duty cycle pulses (LED BLINKS). The function can be disabled via EN_ICHG_MON[1:0] register. |

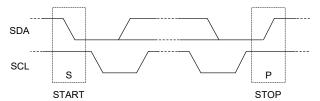

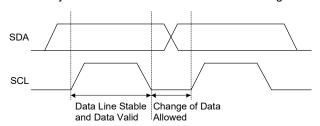

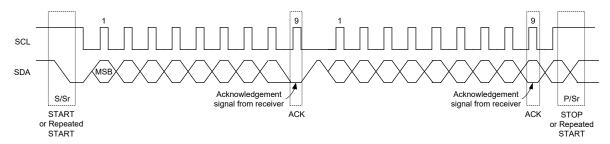

| 5            | 5             | SCL  | DI   | $I^2$ C Clock Signal. Use a 10kΩ pull-up to the logic high rail.                                                                                                                                                                                                                                                                                                           |

| 6            | 6             | SDA  | DIO  | $I^2$ C Data Signal. Use a 10k $\Omega$ pull-up to the logic high rail.                                                                                                                                                                                                                                                                                                    |

| 7            | 7             | nINT | DO   | Open-Drain Interrupt Output Pin. Use a $10k\Omega$ pull-up to the logic high rail. The nINT pin is active low and sends a negative 256 $\mu$ s pulse to inform host about a new charger status update or a fault.                                                                                                                                                          |

| 8            | 8             | OTG  | DI   | Boost Mode Enable Input Pin (Active High). Boost mode is enabled when OTG_CONFIG bit is 1 and OTG pin is pulled high.                                                                                                                                                                                                                                                      |

| 9            | 9             | nCE  | DI   | Charge Enable Input Pin (Active Low). Battery charging is enabled when CHG_CONFIG bit is 1 and nCE pin is pulled low.                                                                                                                                                                                                                                                      |

# **PIN DESCRIPTION (continued)**

| Р            | IN            |                |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------|---------------|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SGM<br>41544 | SGM<br>41544D | NAME           | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10           | 10            | ILIM           | AI   | Input Current Limit. A resistor between ILIM and PGND pins can clamp the input current limit as $I_{INMAX} = K_{ILIM}/R_{ILIM}$ . When EN_ILIM = 1, the lower limit between IINDPM[5:0] registers and ILIM pin resistor setting set the actual input current limit. The ILIM pin can supply higher than 500mA current limit only. If the current limit is not triggered, the ILIM pin voltage indicates the actual input current limit by $I_{IN} = (K_{ILIM} \times V_{ILIM})/(R_{ILIM} \times 0.8V)$ . Change EN_ILIM = 0 can disable both input current limit clamping and input current monitor function from ILIM pin. |

| 11           | 11            | TS             | AI   | Temperature Sense Input Pin. Connect to the battery NTC thermistor that is grounded on the other side. To program operating temperature window, it can be biased by a resistor divider between REGN and PGND. Charge suspends if TS voltage goes out of the programmed range. It is recommended to use a 103AT-2 type thermistor. If NTC or TS pin function is not needed, use a $10k\Omega/10k\Omega$ pair for the resistor divider.                                                                                                                                                                                       |

| 12           | 12            | nQON           | DI   | BATFET On/Off Control Input. Use an internal pull-up to a small voltage for maintaining the default high logic (whenever a source or battery is available). In the ship mode, the BATFET is off. To exit ship mode and turn BATFET on, a logic low pulse with a duration of t <sub>SHIPMODE</sub> (1s TYP) can be applied to nQON. When VBUS source is not connected, a logic low pulse with a duration of t <sub>QON_RST</sub> (10s TYP) resets the system power (SYS) by turning BATFET off for t <sub>BATFET_RST</sub> (340ms TYP) and then goes back to provide a full power reset for system.                          |

| 13, 14       | 13, 14        | BAT            | Р    | Battery Positive Terminal Pin. Use a 10µF capacitor between BAT and PGND pins close to the device. SYS and BAT pins are internally connected by BATFET with current sensing capability.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15, 16       | 15, 16        | SYS            | Р    | Connection Point to Converter Output. SYS is connected to the converter LC filter output that powers the system. BAT to SYS internal current (power from battery to system) is sensed. Connect a 2×10µF capacitor between SYS pin and PGND close to the device.                                                                                                                                                                                                                                                                                                                                                             |

| 17, 18       | 17, 18        | PGND           | Р    | Ground Pin of the Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 19, 20       | 19, 20        | SW             | Р    | Switching Node Output. Connect SW pin to the output inductor. Connect a 47nF bootstrap capacitor from SW pin to BTST pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 21           | 21            | BTST           | Р    | High-side Driver Positive Supply. It is internally connected to the bootstrap diode cathode. Use a 47nF ceramic capacitor from SW pin to BTST pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 22           | 22            | REGN           | Р    | LDO Output that Powers LSFET Driver and Internal Circuits. Internally, the REGN pin is connected to the anode of the bootstrap diode. Place a 4.7µF (10V rating) ceramic capacitor between REGN pin and PGND. It is recommended to place the capacitor close to the REGN pin.                                                                                                                                                                                                                                                                                                                                               |

| 23           | 23            | PMID           | Р    | PMID Pin. PMID is the actual higher voltage port of converter (Buck or Boost) and is connected to the drain of the reverse blocking MOSFET (RBFET) and the drain of HSFET. Connect a $10\mu F$ ceramic capacitor from PMID pin to PGND. It is the proper point for decoupling of high frequency switching currents.                                                                                                                                                                                                                                                                                                         |

| 24           | 24            | DSEL           | DO   | D+/D- Multiplexer Selection Control (Active High). Place a 47nF (6V rating) ceramic capacitor between DSEL and PGND. The pin is normally kept low. For SGM41544D, the pin driven high indicates that the D+/D- detection of the device is in progress, and the D+, D- signals need to be controlled. After the detection is completed, the pin keeps high if DCP or HVDCP is detected, otherwise the pin returns to low.                                                                                                                                                                                                    |

| EP           | EP            | Exposed<br>Pad | Р    | Thermal Pad and Ground Reference. It is the ground reference for the device and also the thermal pad to conduct heat from the device (not suitable for high current return). Tie externally to the PCB ground plane (PGND). Thermal vias under the pad are needed to conduct the heat to the PCB ground planes.                                                                                                                                                                                                                                                                                                             |

NOTE: Al = analog input, AO = analog output, AlO = analog input/output, DI = digital input, DO = digital output, DIO = digital input/output, P = power.

# **ELECTRICAL CHARACTERISTICS**

| PARAME                                               | ETER                                                    | SYMBOL                        | CONDITI                                                                                                                                                     | ONS                                     | MIN   | TYP                     | MAX   | UNITS |

|------------------------------------------------------|---------------------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------|-------------------------|-------|-------|

| Quiescent Current                                    | is                                                      |                               |                                                                                                                                                             |                                         |       |                         |       |       |

|                                                      |                                                         |                               | V <sub>BAT</sub> = 4.2V, V <sub>VBUS</sub> < V <sub>VBUS</sub> leakage between BAT and                                                                      |                                         |       | 0.1                     | 1     |       |

|                                                      | Battery Discharge Current (BATP, BAT, SYS) in Buck Mode |                               |                                                                                                                                                             | BATFET disabled (BATFET_DIS = 1)        |       | 4                       | 6.5   | μΑ    |

|                                                      |                                                         |                               | T <sub>J</sub> < 85°C                                                                                                                                       | BATFET enabled (BATFET_DIS = 0)         |       | 13                      | 20    |       |

| Input Supply Current (VBUS) in Buck Mode when HIZ    |                                                         | I <sub>VBUS_HIZ</sub>         | HIZ mode, no battery,                                                                                                                                       | V <sub>VBUS</sub> = 5V                  |       | 25                      | 35    | μA    |

| Mode is Enabled                                      | do whom the                                             | TVBUS_HIZ                     | battery monitor disabled                                                                                                                                    | V <sub>VBUS</sub> = 12V                 |       | 50                      | 67    | μ/ι   |

|                                                      |                                                         |                               | $V_{VBUS} > V_{VBUS\_UVLOZ}, V_{VBUS}$ converter not switching                                                                                              | > V <sub>BAT</sub> ,                    |       | 2.8                     | 4     |       |

| Input Supply Currer (VBUS) in Buck Mo                |                                                         | I <sub>VBUS</sub>             | V <sub>VBUS</sub> > V <sub>VBUS_UVLOZ</sub> ,<br>V <sub>VBUS</sub> > V <sub>BAT</sub> ,                                                                     | $V_{BAT} = 3.2V$ ,<br>$I_{SYS} = 0A$    |       | 3                       |       | mA    |

|                                                      |                                                         |                               | converter switching                                                                                                                                         | $V_{BAT} = 3.8V,$ $I_{SYS} = 0A$        |       | 3                       |       |       |

| Battery Discharge C                                  | Current                                                 | la a                          | $V_{BAT}$ = 4.2V, Boost mode,<br>$I_{VBUS}$ = 0A,                                                                                                           | PFM_OTG_DIS = 0                         | -     | 3                       | -     | mA    |

| in Boost Mode                                        |                                                         | I <sub>BOOST</sub>            | converter switching                                                                                                                                         | PFM_OTG_DIS = 1                         |       | 15                      |       | IIIA  |

| BAT Pin and VBUS                                     | S Pin Power-Up                                          |                               |                                                                                                                                                             |                                         |       |                         |       |       |

| VBUS Operating Ra                                    | ange                                                    | $V_{VBUS\_OP}$                |                                                                                                                                                             |                                         | 3.9   |                         | 14    | V     |

| VBUS UVLO to Hav<br>(with No Battery)                |                                                         | V <sub>VBUS_UVLOZ</sub>       | V <sub>VBUS</sub> rising                                                                                                                                    |                                         |       | 3.4                     | 3.7   | V     |

| V <sub>VBUS</sub> Minimum (as Conditions) to Turn    |                                                         | $V_{VBUS\_PRESENT}$           | V <sub>VBUS</sub> rising                                                                                                                                    |                                         |       | 3.67                    | 4.1   | V     |

| V <sub>VBUS</sub> Hysteresis (as Conditions) to Turn | s One of the                                            | V <sub>VBUS_PRESENT_HYS</sub> | V <sub>VBUS</sub> falling from above V <sub>VBUS_PRESENT</sub>                                                                                              |                                         |       | 400                     |       | mV    |

| Sleep Mode Falling                                   | Threshold                                               | $V_{SLEEP}$                   | $V_{VBUS}$ - $V_{BAT}$ , $V_{VBUSMIN\_FALL} \le V_{BAT} \le V_{REG}$ , $V_{VBUS}$ falling, $V_{BAT} = 4V$ , $T_J = +25^{\circ}C$                            |                                         | 15    | 60                      | 115   | mV    |

| Sleep Mode Rising                                    | Threshold                                               | V <sub>SLEEPZ</sub>           | $\begin{split} &V_{VBUS} - V_{BAT}, \ V_{VBUSMIN\_FALL} \leq V_{BAT} \leq V_{REG}, \\ &V_{VBUS} \ rising, \ V_{BAT} = 4V, \ T_J = +25^{\circ}C \end{split}$ |                                         | 190   | 240                     | 305   | mV    |

| VBUS                                                 | 6.5V Setting                                            |                               |                                                                                                                                                             | OVP[1:0] = 01                           | 6.38  | 6.5                     | 6.61  |       |

| Over-Voltage                                         | 10.5V Setting                                           | $V_{VBUS\_OV\_RISE}$          | V <sub>VBUS</sub> rising                                                                                                                                    | OVP[1:0] = 10                           | 10.3  | 10.5                    | 10.63 | V     |

| Rising Threshold                                     | 14V Setting                                             |                               |                                                                                                                                                             | OVP[1:0] = 11                           | 14.1  | 14.3                    | 14.5  |       |

| VBUS                                                 | 6.5V Setting                                            |                               |                                                                                                                                                             |                                         |       | 100                     |       |       |

| Over-Voltage                                         | 10.5V Setting                                           | $V_{VBUS\_OV\_HYS}$           |                                                                                                                                                             |                                         |       | 250                     |       | V     |

| Hysteresis                                           | 14V Setting                                             |                               |                                                                                                                                                             |                                         |       | 420                     |       |       |

| BAT Voltage to Hav<br>(No Source on VBU              |                                                         | $V_{BAT\_UVLOZ}$              | V <sub>BAT</sub> rising                                                                                                                                     |                                         | 2.8   |                         |       | V     |

| Battery Depletion F                                  | alling Threshold                                        | $V_{BAT\_DPL\_FALL}$          | V <sub>BAT</sub> falling                                                                                                                                    |                                         | 2.25  | 2.375                   | 2.5   | V     |

| Battery Depletion R                                  | ising Threshold                                         | $V_{BAT\_DPL\_RISE}$          | V <sub>BAT</sub> rising                                                                                                                                     |                                         | 2.43  | 2.53                    | 2.63  | V     |

| Bad Adaptor Detection Threshold                      |                                                         | $V_{VBUS\_MIN}$               | V <sub>VBUS</sub> falling                                                                                                                                   |                                         |       | 3.8                     |       | V     |

| Bad Adaptor Detect<br>Source                         | ion Current                                             | I <sub>BAD_SRC</sub>          | V <sub>VBUS</sub> = 5V, sink current fr                                                                                                                     | om VBUS to PGND                         |       | 30                      |       | mA    |

| Power Path Manag                                     | gement                                                  |                               |                                                                                                                                                             |                                         |       |                         |       |       |

|                                                      |                                                         |                               | I <sub>SYS</sub> = 0A,                                                                                                                                      | V <sub>BAT</sub> > V <sub>SYS_MIN</sub> |       | V <sub>BAT</sub> + 60mV |       |       |

| Typical System Reg                                   | gulation Voltage                                        | $V_{SYS}$                     | BATFET disabled (BATFET_DIS = 1)                                                                                                                            | V <sub>BAT</sub> < V <sub>SYS_MIN</sub> |       | V <sub>SYS_MIN</sub> +  |       | V     |

|                                                      |                                                         | _                             |                                                                                                                                                             |                                         | 160mV |                         |       |       |

# **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                                                               | SYMBOL                     | CONDIT                                                                   | TONS                         | MIN   | TYP   | MAX   | UNITS |

|-------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------|------------------------------|-------|-------|-------|-------|

| Power Path Management                                                   |                            |                                                                          |                              |       |       |       |       |

| Minimum DC System Voltage Output                                        | V <sub>SYS_MIN</sub>       | $V_{BAT} < V_{SYS\_MIN}, I_{SYS} = 0.0$<br>SYS_MIN[2:0] = 101 (3         |                              | 3.6   | 3.65  |       | V     |

| Maximum DC System Voltage Output                                        | V <sub>SYS_MAX</sub>       | V <sub>BAT</sub> = 4.4V, I <sub>SYS</sub> = 0A,<br>SYS_MIN[2:0] = 101 (3 | .5V)                         | 4.41  | 4.46  | 4.51  | V     |

| Top Reverse Blocking MOSFET (RBFET) On-Resistance between VBUS and PMID | R <sub>ON_RBFET</sub>      |                                                                          |                              |       | 21    |       | mΩ    |

| Top Switching MOSFET (HSFET) On-Resistance between PMID and SW          | R <sub>ON_HSFET</sub>      |                                                                          |                              |       | 24    |       | mΩ    |

| Bottom Switching MOSFET (LSFET)<br>On-Resistance between SW and PGND    | R <sub>ON_LSFET</sub>      |                                                                          |                              |       | 25    |       | mΩ    |

| BATFET Forward Voltage in Supplement Mode                               | $V_{\text{FWD}}$           | BAT discharge current                                                    | 10mA                         |       | 25    |       | mV    |

| Battery Charger                                                         |                            | ·                                                                        |                              |       |       |       |       |

| Typical Charge Voltage Range                                            | V <sub>BAT REG RANGE</sub> | VREG_SET = 0                                                             |                              | 3.856 |       | 4.624 | V     |

| Typical Charge Voltage Harige                                           | V BAI_REG_RANGE            | VREG_SET = 1                                                             |                              | 3.504 |       | 4.272 | V     |

| Typical Charge Voltage Step                                             | V <sub>BATREG_STEP</sub>   |                                                                          |                              |       | 16    |       | mV    |

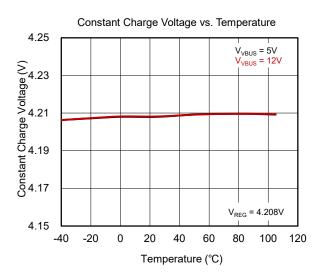

| Charge Voltage Setting                                                  | V <sub>BAT_REG</sub>       | (VREG[5:0] = 01 0110) T                                                  | T <sub>J</sub> = +25°C       | 4.192 | 4.208 | 4.224 | V     |

|                                                                         |                            |                                                                          | $T_J = 0^{\circ}C$ to +65°C  | 4.187 |       | 4.229 |       |

|                                                                         |                            | V BAI — 4.002 V                                                          | T <sub>J</sub> = +25°C       | 4.333 | 4.35  | 4.367 | V     |

|                                                                         |                            |                                                                          | $T_J = 0^{\circ}C$ to +65°C  | 4.329 |       | 4.371 |       |

| Charge Voltage Resolution Accuracy                                      | V <sub>BAT_REG_ACC</sub>   | V <sub>BAT_REG</sub> = 4.208V or                                         | T <sub>J</sub> = +25°C       | -0.4  |       | 0.4   | %     |

| Charge Voltage Nosciation / todatacy                                    | ▼ BAI_REG_ACC              | \/ - 4.252\/                                                             | $T_J = 0^{\circ}C$ to +65°C  | -0.5  |       | 0.5   | 70    |

| Typical Fast Charge Current Regulation Range                            | I <sub>CHG_REG_RANGE</sub> |                                                                          |                              | 0     |       | 5056  | mA    |

| Typical Fast Charge Current Regulation Step                             | I <sub>CHG_REG_STEP</sub>  |                                                                          |                              |       | 64    |       | mA    |

|                                                                         |                            |                                                                          | I <sub>CHG</sub> = 128mA     | 90    | 115   | 140   |       |

|                                                                         |                            | V <sub>BAT</sub> = 3.1V,                                                 | I <sub>CHG</sub> = 256mA     | 205   | 250   | 295   |       |

|                                                                         |                            | T <sub>J</sub> = +25°C                                                   | I <sub>CHG</sub> = 1792mA    | 1740  | 1790  | 1840  |       |

| Fast Charge Current Regulation                                          | ,                          |                                                                          | I <sub>CHG</sub> = 2048mA    | 2000  | 2048  | 2096  | ^     |

| Accuracy                                                                | ICHG_REG_ACC               |                                                                          | I <sub>CHG</sub> = 128mA     | 122   | 136   | 150   | mA    |

|                                                                         |                            | V <sub>BAT</sub> = 3.8V,                                                 | I <sub>CHG</sub> = 256mA     | 250   | 265   | 280   |       |

|                                                                         |                            | T <sub>J</sub> = +25°C                                                   | I <sub>CHG</sub> = 1792mA    | 1745  | 1790  | 1835  |       |

|                                                                         |                            |                                                                          | I <sub>CHG</sub> = 2048mA    | 2005  | 2048  | 2090  |       |

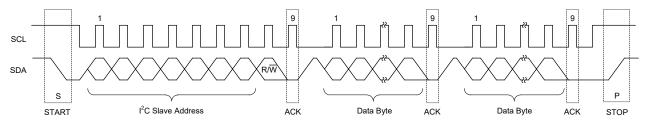

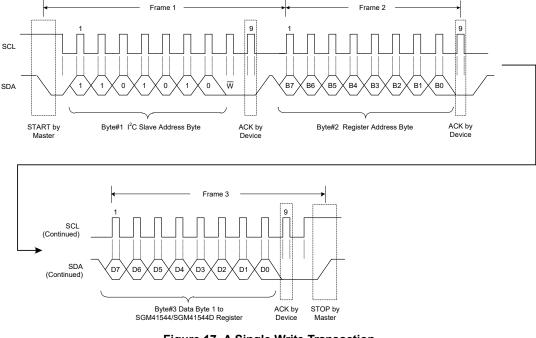

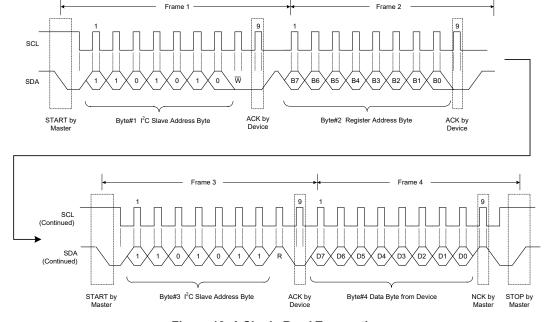

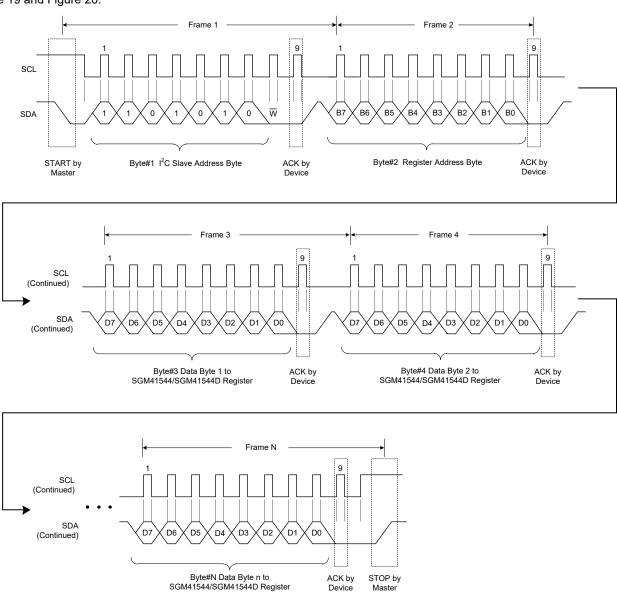

| Battery LOWV Falling Threshold                                          | 1/                         | Fast charge to pre-char                                                  | ge, BATLOWV = 1              | 2.63  | 2.76  | 2.89  | V     |