## SGM6627 650kHz/1.2MHz, 4.2A, 18.5V Boost Converter

#### **GENERAL DESCRIPTION**

SGM6627 is a high-efficient Boost converter with high frequency. The device integrates a  $0.13\Omega$  power switch with 4.2A (TYP) current limit and supports an output voltage up to 18.5V. A pin selectable 650kHz or 1.2MHz switching frequency provides the device with fast transient response. This device also includes the built-in functions of soft-start, under-voltage lockout (UVLO) and thermal shutdown.

The SGM6627 is available in a Green TDFN-3×3-10AL package.

#### **FEATURES**

- 2.5V to 5.5V Input Voltage Range

- Up to 18.5V Output Voltage

- 4.2A (TYP) Current Limit

- 650kHz/1.2MHz Selectable Switching Frequency

- Programmable Soft-Start

- Under-Voltage Lockout (UVLO)

- Thermal Shutdown

- Available in a Green TDFN-3×3-10AL Package

#### **APPLICATIONS**

Body Electronics Infotainment Clusters Telemetry and Calling

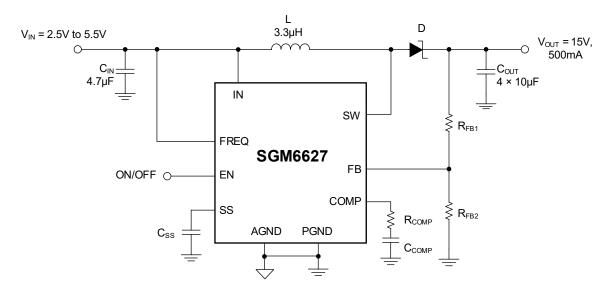

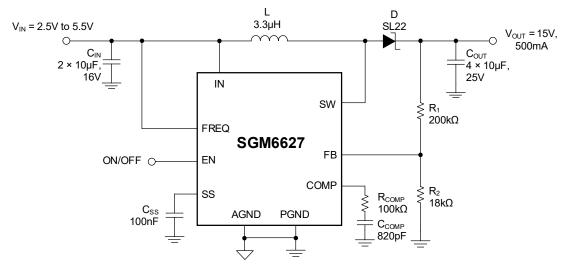

### SIMPLIFIED SCHEMATIC

Figure 1. Simplified Schematic

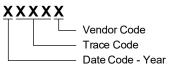

#### PACKAGE/ORDERING INFORMATION

| MODEL   | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING     | PACKING<br>OPTION   |

|---------|------------------------|-----------------------------------|--------------------|------------------------|---------------------|

| SGM6627 | TDFN-3×3-10AL          | -40°C to +125°C                   | SGM6627XTGZ10G/TR  | SGM<br>6627GZ<br>XXXXX | Tape and Reel, 4000 |

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### ABSOLUTE MAXIMUM RATINGS

| Input Voltage Range                  | 0.3V to 6V     |

|--------------------------------------|----------------|

| EN, FB, SS, FREQ, COMP               | 0.3V to 6V     |

| SW                                   | 0.3V to 20V    |

| Package Thermal Resistance           |                |

| TDFN-3×3-10AL, θ <sub>JA</sub>       | 44.4°C/W       |

| TDFN-3×3-10AL, θ <sub>JB</sub>       | 19.3°C/W       |

| TDFN-3×3-10AL, θ <sub>JC (TOP)</sub> | 44.4°C/W       |

| TDFN-3×3-10AL, $\theta_{JC (BOT)}$   | 8.3°C/W        |

| Junction Temperature                 | +150°C         |

| Storage Temperature Range            | 65°C to +150°C |

| Lead Temperature (Soldering, 10s)    | +260°C         |

| ESD Susceptibility (1) (2)           |                |

| HBM                                  | ±3000V         |

| CDM                                  | ±1000V         |

#### NOTES:

- 1. For human body model (HBM), all pins comply with ANSI/ESDA/JEDEC JS-001 specifications.

- 2. For charged device model (CDM), all pins comply with ANSI/ESDA/JEDEC JS-002 specifications.

#### RECOMMENDED OPERATING CONDITIONS

| Input Voltage Range, V <sub>IN</sub>         | 2.5V to 5.5V                   |

|----------------------------------------------|--------------------------------|

| Boost Output Voltage Range, V <sub>OUT</sub> | V <sub>IN</sub> +0.5V to 18.5V |

| Operating Junction Temperature Range         | 40°C to +150°C                 |

#### OVERSTRESS CAUTION

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

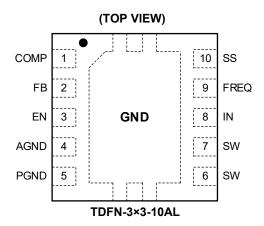

## **PIN CONFIGURATION**

## **PIN DESCRIPTION**

| PIN         | NAME | TYPE | FUNCTION                                                                                                                                                |

|-------------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | COMP | I/O  | Compensation Pin. Connect a capacitor and resistor in series.                                                                                           |

| 2           | FB   | I    | Feedback Input Pin. Feedback input to the error amplifier for regulated output.                                                                         |

| 3           | EN   | I    | Enable Pin of the Boost Regulator. Logic low disables the chip and logic high enables it.                                                               |

| 4           | AGND | G    | Analog Ground.                                                                                                                                          |

| 5           | PGND | G    | Power Ground.                                                                                                                                           |

| 6           | SW   | 1    | Switching Node of the Device.                                                                                                                           |

| 7           | SW   | 1    | Switching Node of the Device.                                                                                                                           |

| 8           | IN   | I    | Supply Power Input Pin.                                                                                                                                 |

| 9           | FREQ | I    | Frequency Selection Pin. When FREQ is connected to GND, the device operates at 650kHz. When FREQ is connected to IN pin, the device operates at 1.2MHz. |

| 10          | SS   | 0    | Soft-Start Control Pin. Connect a capacitor to this pin to set soft-start time. Open = no soft-start.                                                   |

| Exposed Pad | GND  | G    | Ground.                                                                                                                                                 |

NOTE: I = input, O = output, I/O = input/output, G = ground.

## **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 5V, V_{EN} = V_{IN}, V_{OUT} = 15V, T_J = -40^{\circ}C$  to +125°C, all typical values are measured at  $T_J = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                               | SYMBOL               | CONDITIONS                                                                         | MIN                   | TYP    | MAX   | UNITS |

|-----------------------------------------|----------------------|------------------------------------------------------------------------------------|-----------------------|--------|-------|-------|

| Supply                                  |                      |                                                                                    | _                     |        |       |       |

| Input Voltage Range                     | V <sub>IN</sub>      |                                                                                    | 2.5                   |        | 5.5   | V     |

| Operating Quiescent Current into IN Pin | ΙQ                   | Device not switching, V <sub>FB</sub> = 1.3V                                       |                       | 70     | 110   | μΑ    |

| Shutdown Current into IN Pin            | $I_{SD\_IN}$         | EN = GND                                                                           |                       |        | 1     | μΑ    |

| Under-Voltage Lockout                   | $V_{\sf UVLO}$       | V <sub>IN</sub> falling                                                            |                       |        | 2.4   | V     |

| Threshold                               | VUVLO                | V <sub>IN</sub> rising                                                             |                       |        | 2.5   | V     |

| Thermal Shutdown                        | T <sub>SD</sub>      | Temperature rising                                                                 |                       | 153    |       | °C    |

| Thermal Shutdown Hysteresis             | T <sub>SD_HYS</sub>  |                                                                                    |                       | 12     |       | °C    |

| Logic Signals of EN, FREQ               |                      |                                                                                    |                       | •      |       |       |

| High-Level Input Voltage                | V <sub>IH</sub>      | V <sub>IN</sub> = 2.5V to 5.5V                                                     | 1.2                   |        |       | V     |

| Low-Level Input Voltage                 | V <sub>IL</sub>      | V <sub>IN</sub> = 2.5V to 5.5V                                                     |                       |        | 0.4   | V     |

| Input Leakage Current                   | I <sub>IN_LEAK</sub> | EN = FREQ = GND                                                                    |                       |        | 0.1   | μA    |

| Boost Converter                         |                      |                                                                                    |                       | •      |       |       |

| Boost Output Voltage                    | $V_{OUT}$            |                                                                                    | V <sub>IN</sub> + 0.5 |        | 18.5  | V     |

| Feedback Regulation Voltage             | $V_{FB}$             |                                                                                    | 1.226                 | 1.238  | 1.250 | V     |

| Transconductance Error<br>Amplifier     | gmEA                 |                                                                                    |                       | 110    |       | μA/V  |

| Feedback Input Bias Current             | $I_{FB}$             | V <sub>FB</sub> = 1.238V                                                           |                       |        | 0.1   | μΑ    |

| N-Channel MOSFET                        | В                    | $V_{IN} = V_{GS} = 5V$ , $I_{SW} = current limit$                                  |                       | 0.11   | 0.21  | Ω     |

| On-Resistance                           | $R_{DSON}$           | $V_{IN} = V_{GS} = 3V$ , $I_{SW} = current limit$                                  |                       | 0.14   | 0.24  | 12    |

| SW Leakage Current                      | I <sub>SW_LEAK</sub> | EN = GND, V <sub>SW</sub> = 6V                                                     |                       |        | 2     | μΑ    |

| N-Channel MOSFET Current<br>Limit       | I <sub>LIM</sub>     |                                                                                    | 3.3                   | 4.2    | 5.1   | Α     |

| Soft-Start Current                      | I <sub>SS</sub>      | V <sub>SS</sub> = 1.238V                                                           | 9                     | 11     | 13    | μΑ    |

| Switching Fragues 2                     | f                    | FREQ = V <sub>IN</sub> = 5V, V <sub>OUT</sub> = 15V, I <sub>OUT</sub> = 500mA      | 0.9                   | 1.2    | 1.5   | MHz   |

| Switching Frequency                     | $f_{SW}$             | FREQ = GND, V <sub>IN</sub> = 5V, V <sub>OUT</sub> = 15V, I <sub>OUT</sub> = 500mA | 505                   | 650    | 795   | kHz   |

| Line Regulation                         |                      | V <sub>IN</sub> = 2.5V to 5.5V, I <sub>OUT</sub> = 10mA                            |                       | 0.0005 |       | %/V   |

| Load Regulation                         |                      | V <sub>IN</sub> = 5V to 6V, I <sub>OUT</sub> = 1mA to 1A                           |                       | 0.25   |       | %/A   |

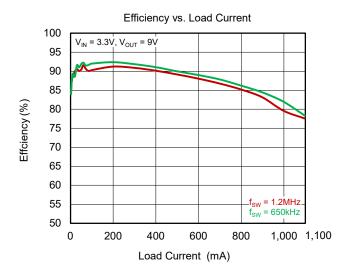

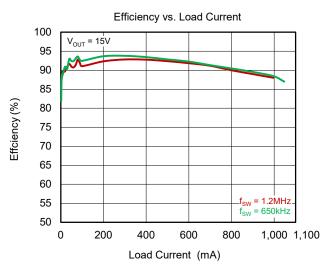

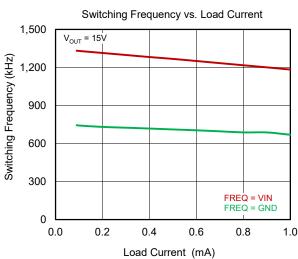

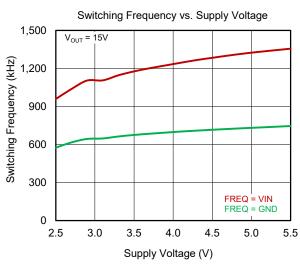

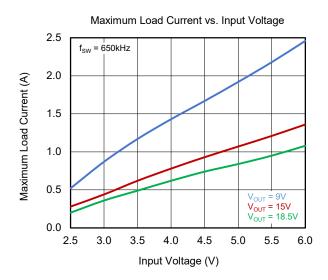

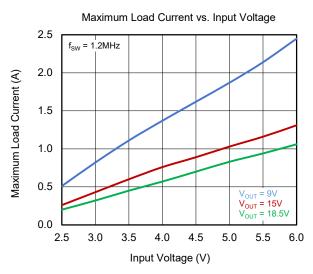

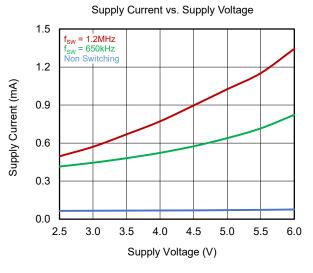

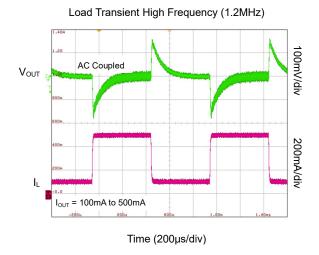

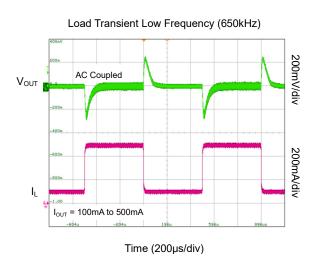

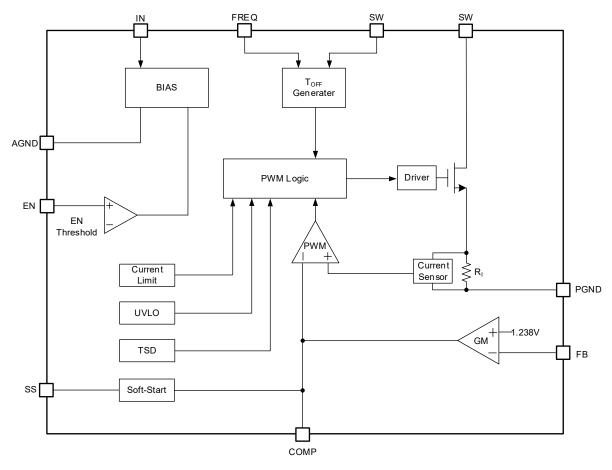

## TYPICAL PERFORMANCE CHARACTERISTICS

$T_A$  = +25°C,  $V_{IN}$  = 5V, unless otherwise noted.

## **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

$T_A$  = +25°C,  $V_{IN}$  = 5V,  $V_{OUT}$  = 15V, unless otherwise noted.

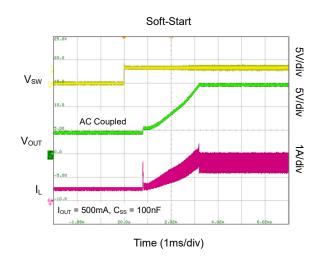

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. Block Diagram

#### **DETAILED DESCRIPTION**

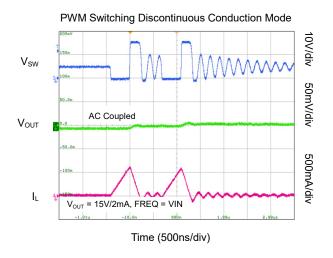

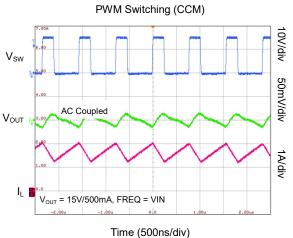

The SGM6627 is a Boost DC/DC converter featuring an integrated low-side MOSFET switch and an adaptive constant off-time control scheme with quasi-constant frequency operation to regulate output voltages up to 18.5V. Designed for wide adaptability, it supports input voltages as low as 2.5V and delivers a peak current limit of 4.2A (TYP). The switching frequency is selectable between 650kHz and 1.2MHz via FREQ pin. Its CFT control architecture ensures enhanced transient response to line and load variations, outperforming conventional control methods in dynamic scenarios.

The device operates in multiple modes to optimize efficiency under varying loads: continuous conduction mode (CCM) under heavy loads for high efficiency, discontinuous conduction mode (DCM) during light loads to minimize losses, and pulse-skip mode when the output load is extremely low to maintain output precision. A built-in soft-start mechanism suppresses inrush current during startup, ensuring reliable power-up sequences. These multi-mode operations, combined with rapid transient recovery, make the SGM6627 suitable for applications demanding fast dynamic performance.

By integrating advanced control strategies and robust protection features, the SGM6627 achieves broader application compatibility compared to traditional converters. Its ability to seamlessly transit between operational modes while maintaining voltage precision and efficiency underscores its versatility in both power-sensitive and high-performance environments.

#### **Soft-Start**

The Boost converter employs an adjustable soft-start mechanism to mitigate inrush current during startup. This is achieved by connecting an external capacitor to the SS pin, which controls the gradual ramp up of the internal current limit. When the EN pin is activated (pulled high), the soft-start capacitor ( $C_{SS}$ ) is pre-charged to 0.6V and then charged with a constant  $10\mu A$  current. During this phase, the COMP voltage follows the SS voltage, linearly adjusting the peak inductor current to ensure a gradual increase in the output voltage. Once the FB voltage reaches 98% of its nominal value, the COMP pin initiates closed-loop regulation, while the SS voltage continues to rise until it stabilizes at the VIN level.

The soft-start duration scales with  $C_{\rm SS}$  capacitance (larger values prolong the ramp time) though 100nF typically suffices for most applications. Upon disabling the EN pin (pulled low),  $C_{\rm SS}$  is actively discharged to

ground, resetting the startup sequence. This design balances controlled current limiting with minimal external component requirements.

#### Frequency Select Pin (FREQ)

The switching frequency of the SGM6627 is user configurable through its FREQ pin, which supports binary selection between two preset values: connecting the FREQ pin directly to VIN sets the operating frequency to 1.2MHz, while grounding the FREQ pin (GND) reduces the frequency to 650kHz.

A higher switching frequency can enhance the load transient response capability. This means the converter can better adapt to sudden changes in the load. However, it will cause a slight decrease in conversion efficiency. Additionally, operating in a high-frequency mode can reduce the output ripple voltage, which helps in providing a more stable output voltage.

#### **Under-Voltage Lockout (UVLO)**

Under-voltage lockout protection (UVLO) monitors the VIN power input. When the voltage is lower than UVLO threshold voltage, the device is shut down. This is a non-latched protection.

#### **Thermal Shutdown**

The internal thermal shutdown protection turns off the device when the junction temperature exceeds +153°C (TYP). The chip will resume operation when the junction temperature drops by at least 12°C (TYP).

#### **Over-Voltage Prevention**

The device incorporates an over-voltage protection mechanism that triggers when the FB pin voltage exceeds its threshold (typically 3% above the 1.238V). Once the OVP is triggered, the device stops switching immediately, preventing further voltage escalation to the output. This mechanism protects the device from potential damage caused by sudden load shedding or other factors from the downstream circuit.

#### **Device Functional Modes**

The converter automatically adjusts its operating modes based on load conditions: it remains in continuous conduction mode (CCM) when the input current exceeds half the inductor ripple current. As the load current decreases, it transits to discontinuous conduction mode (DCM). Under extremely light loads, pulse skipping is activated to regulate the output voltage, ensuring efficient energy management across varying operational demands.

#### APPLICATION INFORMATION

The SGM6627 supports output voltages up to 18.5V with a 4.2A peak current limit, utilizing current-mode control and quasi-fixed frequency for stable operation. Its switching frequency is adjustable between 650kHz and 1.2MHz, with an input range of 2.5V to 5.5V, while

external compensation ensures adaptability and stability. A dedicated soft-start pin controls inrush current during startup, and the subsequent guide outlines a simplified process to configure the IC as a Boost converter for voltage regulation.

Figure 3. f<sub>SW</sub> = 1.2MHz, Application Circuit

#### **Design Requirements**

For this design example, use the parameters shown in Table 1.

**Table 1. Design Parameters**

| PARAMETER           | EXAMPLE VALUE |

|---------------------|---------------|

| Input Voltage       | 2.5V to 5.5V  |

| Output Voltage      | 15V           |

| Output Current      | 500mA         |

| Switching Frequency | 1.2MHz        |

#### **Detailed Design Procedure**

The design procedure begins by confirming the Boost converter's peak output current capability aligns with system requirements. This validation can be performed through provided efficiency curve for preliminary calculations.

Duty cycle (D) is calculated with Equation 1.

$$D = 1 - \frac{V_{IN} \times \eta}{V_{OUT}}$$

(1)

Maximum output current ( $I_{\text{OUT\_MAX}}$ ) is calculated with Equation 2.

$$I_{OUT\_MAX} = \left(I_{LIM\_MIN} - \frac{\Delta I_L}{2}\right) \times (1 - D)$$

(2)

Peak switch current in application ( $I_{SW\_PEAK}$ ) is calculated with Equation 3.

$$I_{SW\_PEAK} = \frac{\Delta I_L}{2} + \frac{I_{OUT}}{1 - D}$$

(3)

The inductor peak-to-peak ripple current  $(\Delta I_L)$  is calculated with Equation 4.

$$\Delta I_{L} = \frac{V_{IN} \times D}{f_{S} \times L}$$

(4)

where,  $V_{\text{IN}}$  is the minimum input voltage.  $V_{\text{OUT}}$  is the output voltage.  $I_{\text{LIM\_MIN}}$  is the converter switch current limit (minimum switch current limit = 3.3A).  $f_{\text{SW}}$  is the converter switching frequency (typically 1.2MHz or 650kHz). L is the selected inductor value.  $\eta$  is the estimated converter efficiency (use the number from the efficiency plots or 90% as an estimation).

## **APPLICATION INFORMATION (continued)**

#### **Inductor Selection**

The SGM6627 is available with a wide range of inductors, prioritizing two key criteria: saturation current and DC resistance. The inductor's saturation current must exceed the calculated peak switch current (Equation 3) with sufficient margin for load spikes, or alternatively match/exceed the 5.1A maximum switch current limit for conservative designs. Lower DC resistance typically enhances efficiency, though core material, type, and high-frequency losses (core losses, skin/proximity effects at 1.2MHz) also significantly impact the performance. Larger inductors generally yield higher efficiency, with variations of 2% to 10% between models. Recommended values are 3µH to 6μH (3.3μH typical) at 1.2MHz, or 6μH to 13μH (6.8μH typical) for 650kHz operation. Engineers must verify inductor selections against their specific application requirements using Table 2 to ensure optimal performance.

It is recommended that the inductor current ripple is below 35% of the average inductor current. Equation 5 can be used to calculate the inductor value (L).

$$L = \left(\frac{V_{IN}}{V_{OUT}}\right)^{2} \times \left(\frac{V_{OUT} - V_{IN}}{I_{OUT} \times f_{S}}\right) \times \left(\frac{\eta}{0.35}\right)$$

(5)

where,  $I_{\text{OUT}}$  is the maximum output current in the application.

#### **Rectifier Diode Selection**

To achieve high efficiency, a Schottky diode is strongly recommended for rectification purposes. The reverse voltage rating of the Schottky should exceed the maximum output voltage of the Boost converter, while its average forward current rating must match the converter's output current ( $I_{OUT}$ ). These parameters ensure reliable operation under both voltage and load conditions.

$$I_{AVG} = I_{OUT} \tag{6}$$

A Schottky diode rated for 2A average forward current is typically adequate for general use. Lower current diodes may be viable if aligned with the output current, provided their power dissipation capacity meets operational requirements. Typically the power dissipation on the diode must be around 500mW. The power dissipation of the Schottky diode is calculated by following equation:

$$P_{D} = I_{AVG} \times V_{FORWARD} \tag{7}$$

Table 3 lists the recommended Schottky diode for most application.

**Table 2. Inductor Selection**

| INDUCTOR VALUE TYPICAL DCR I <sub>SAT</sub> S |                   | SUPPLIER | SIZE (L × W × H mm <sup>3</sup> ) | COMPONENT CODE    |            |  |  |

|-----------------------------------------------|-------------------|----------|-----------------------------------|-------------------|------------|--|--|

| 1.2MHz                                        |                   |          |                                   |                   |            |  |  |

| 4.7µH                                         | 7.9mΩ             | 15.5A    | Wurth Elektronik                  | 12.1 × 11.4 × 9.5 | 7443320470 |  |  |

| 3.3µH                                         | 3.3μH 5.7mΩ 22.4A |          | Wurth Elektronik                  | 12.1 × 11.4 × 9.5 | 7443320330 |  |  |

| 650kHz                                        |                   |          |                                   |                   |            |  |  |

| 6.8µH                                         | 11mΩ              | 12.9A    | Wurth Elektronik                  | 12.1 × 11.4 × 9.5 | 7443320680 |  |  |

**Table 3. Rectifier Diode Selection**

|                  | able of Resulting Bload Golden |                                              |                         |                |  |  |  |  |  |  |

|------------------|--------------------------------|----------------------------------------------|-------------------------|----------------|--|--|--|--|--|--|

| I <sub>AVG</sub> | $V_R$                          | V <sub>R</sub> V <sub>FORWARD</sub> SUPPLIER |                         | COMPONENT CODE |  |  |  |  |  |  |

| 2A               | 20V                            | 0.44V                                        | Vishay Semiconductor    | SL22           |  |  |  |  |  |  |

| 2A               | 20V                            | 0.5V                                         | Fairchild Semiconductor | SS22           |  |  |  |  |  |  |

## **APPLICATION INFORMATION (continued)**

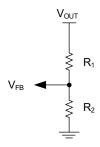

#### **Setting the Output Voltage**

The output voltage is configured via an external resistive divider. To ensure precision and noise immunity, a feedback divider current  $\geq 50\mu A$  is typically recommended. For typical application, an  $18k\Omega$  resistor is used as a bottom resistor.

The resistors are then calculated as shown in Equation  $8 \cdot$

$$R_{2} = \frac{V_{FB}}{70\mu A} \approx 18k\Omega$$

$$R_{1} = R_{2} \times \left(\frac{V_{S}}{V_{FB}} - 1\right)$$

$$V_{FB} = 1.238V$$

(8)

#### **Compensation (COMP)**

The regulator loop compensation can be optimized by modifying the external components connected to the COMP pin, which functions as the output terminal of the internal transconductance error amplifier.

Equation 9 can be used to calculate  $R_{COMP}$  and  $C_{COMP}$ .

$$R_{COMP} = \frac{110 \times V_{IN} \times V_{OUT} \times C_{OUT}}{L \times I_{OUT}}$$

$$C_{COMP} = \frac{V_{OUT} \times C_{OUT}}{7.5 \times I_{OUT} \times R_{COMP}}$$

(9)

where, C<sub>OUT</sub> is the output capacitance.

Make sure that  $R_{COMP}$  < 120k $\Omega$  and  $C_{COMP}$  > 820pF, independent of the results of the above formulas.

Table 4 lists the specialized compensation networks that can improve the load transient response for different application conditions.

Standard values of  $R_{COMP}$  = 16k $\Omega$  and  $C_{COMP}$  = 2.7nF works for the majority of the applications.

Table 4. Recommended Compensation Network Values at High and Low Frequency

| FREQUENCY            | L (µH) | V <sub>OUT</sub> (V) | V <sub>IN</sub> ± 20% (V) | $R_{COMP}(k\Omega)$ | C <sub>COMP</sub> |

|----------------------|--------|----------------------|---------------------------|---------------------|-------------------|

|                      |        | 15                   | 5                         | 100                 | 820pF             |

|                      |        | 15                   | 3.3                       | 91                  | 1.2nF             |

| High (1.2MHz)        | 3.3    | 12                   | 5                         | 68                  | 820pF             |

| 1 ligi1 (1.2lvii 12) | 3.3    | 12                   | 3.3                       | 68                  | 1.2nF             |

|                      |        | 9                    | 5                         | 39                  | 820pF             |

|                      |        | 9                    | 3.3                       | 39                  | 1.2nF             |

|                      | 6.8    | 15                   | 5                         | 51                  | 1.5nF             |

|                      |        | 15                   | 3.3                       | 47                  | 2.7nF             |

| Low (650kHz)         |        | 12                   | 5                         | 33                  | 1.5nF             |

| LOW (030KHZ)         |        |                      | 3.3                       | 33                  | 2.7nF             |

|                      |        | 9                    | 5                         | 18                  | 1.5nF             |

|                      |        |                      | 3.3                       | 18                  | 2.7nF             |

## **APPLICATION INFORMATION (continued)**

#### **Input Capacitor Selection**

For optimal performance, low ESR ceramic capacitors are recommended for effective input voltage filtering. The SGM6627's analog input (IN) requires a 1µF bypass capacitor between IN and GND positioned as close to the IC as practical. Most applications benefit from two parallel 10µF ceramic input capacitors (or a single 22µF ceramic capacitor), with larger values enhancing filtering effect.

#### **Output Capacitor Selection**

For optimal output voltage regulation, low ESR ceramic are recommended. capacitors Α total capacitance of  $40\mu F$  (achieved via 4 ×  $10\mu F$  or 2 × configurations) typically satisfies 22µF typical requirements. Increased capacitance values may enhance transient performance. The DC bias derating effects of the ceramic capacitors should be considered when selecting capacitors. Final component validation remains mandatory to verify compatibility under target operating conditions

To calculate the output voltage ripple, use Equation 10.

$$\Delta V_{C} = \frac{V_{OUT} - V_{IN}}{V_{OUT} \times f_{S}} \times \frac{I_{OUT}}{C_{OUT}}$$

$$\Delta V_{C\_ESR} = I_{L\_PEAK} \times R_{C\_ESR}$$

(10)

where,  $\Delta V_C$  is the output voltage ripple dependent on output capacitance, output current, and switching frequency.  $\Delta V_{C ESR}$  is the output voltage ripple due to output capacitors ESR (equivalent series resistance).  $I_{\text{SW PEAK}}$  is the inductor peak switch current in the application.  $R_{\text{C ESR}}$  is the output capacitors equivalent series resistance (ESR).  $\Delta V_{C\ ESR}$  can be neglected in many cases because ceramic capacitors provide low ESR.

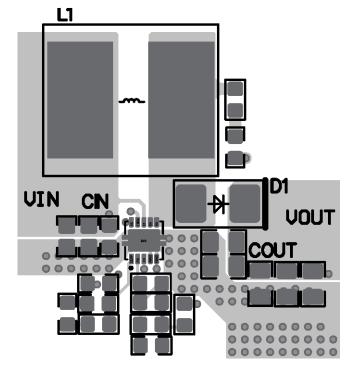

#### **Layout Guidelines**

For most switching power supplies, especially with high frequency and high current, a good layout is required to prevent EMI failure and device damage as well as good stability of the device.

- Use wide and short traces for main power traces.

- Place the input capacitor to the IN and GND pins as close as possible. If possible, choose high capacitance value for C<sub>IN</sub> for a stable input.

- · Since the SW pin carries high current with fast rising and falling edges, all connections to the SW pin should be kept as short and wide as possible.

- The output capacitor (C<sub>OUT</sub>) should be placed close to  $V_{OUT}$ . It is also beneficial to have the ground of  $C_{OUT}$ close to the GND pin since there is large ground return current flowing between them.

- Sensitive signals like FB and COMP must be placed away from SW trace to prevent noise coupling through capacitance. Components should positioned in close proximity to the corresponding pins to cut down on parasitic inductance and capacitance.

Figure 4. PCB Layout

#### **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Original to REV.A (DECEMBER 2025)

Page

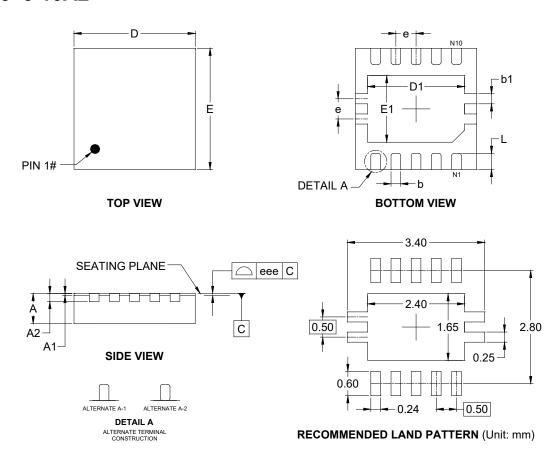

# PACKAGE OUTLINE DIMENSIONS TDFN-3×3-10AL

| Cymhal | Dimensions In Millimeters |                            |       |  |  |  |

|--------|---------------------------|----------------------------|-------|--|--|--|

| Symbol | MIN                       | NOM                        | MAX   |  |  |  |

| А      | 0.700                     | -                          | 0.800 |  |  |  |

| A1     | 0.000                     | -                          | 0.050 |  |  |  |

| A2     |                           | 0.203 REF                  |       |  |  |  |

| b      | 0.180                     | -                          | 0.300 |  |  |  |

| b1     |                           | 0.250 REF                  |       |  |  |  |

| D      | 2.900                     | 2.900 -                    |       |  |  |  |

| Е      | 2.900                     | -                          | 3.100 |  |  |  |

| D1     | 2.300                     | -                          | 2.500 |  |  |  |

| E1     | 1.550                     | 1.550 -                    |       |  |  |  |

| е      |                           | 0.500 BSC<br>0.300 - 0.500 |       |  |  |  |

| L      | 0.300                     |                            |       |  |  |  |

| eee    |                           | 0.080                      |       |  |  |  |

NOTE: This drawing is subject to change without notice.

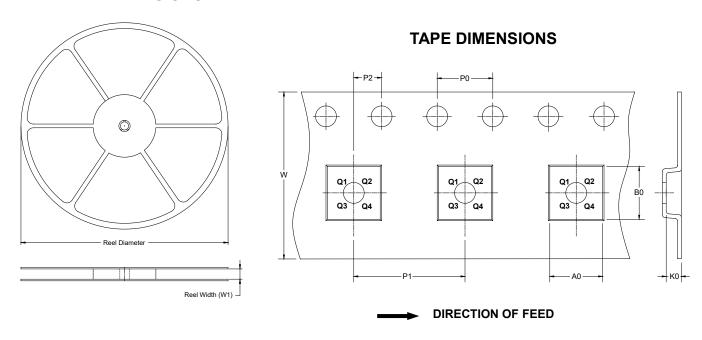

## TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type  | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TDFN-3×3-10AL | 13"              | 12.4                     | 3.30       | 3.30       | 1.10       | 4.0        | 8.0        | 2.0        | 12.0      | Q2               |

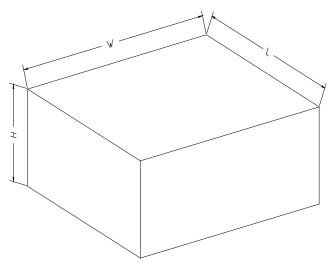

## **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

## **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |        |

|-----------|----------------|---------------|----------------|--------------|--------|

| 13″       | 386            | 280           | 370            | 5            | DD0002 |