## SGM61020S 2A High Efficiency Synchronous Buck Converter

#### GENERAL DESCRIPTION

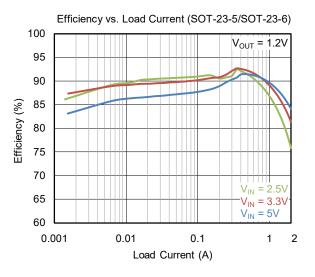

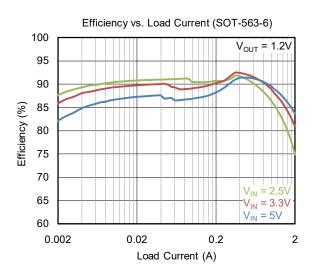

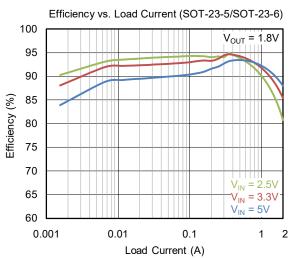

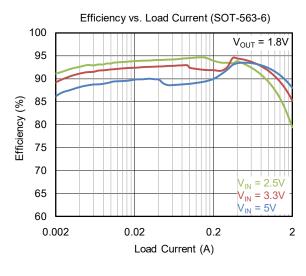

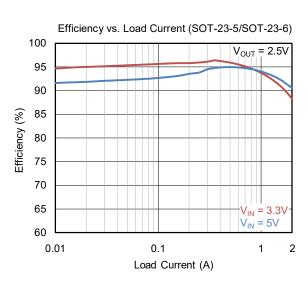

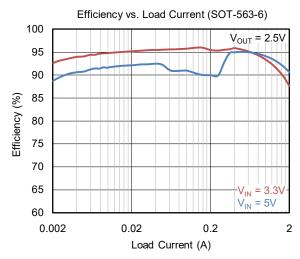

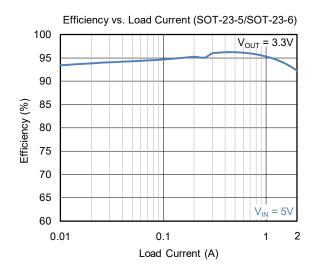

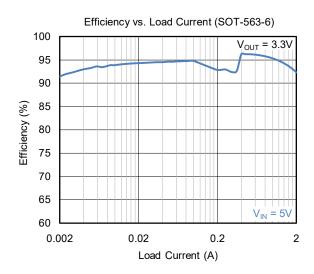

The SGM61020S is a high efficiency synchronous Buck DC/DC converter with 2A output current capability and adjustable output voltage. The input supply voltage is in the range of 2.5V to 5.5V. Using adaptive off-time peak current control, the efficiency of this device is higher than 80% for loads over 1mA and reaches 95% in the moderate load ranges (5V to 3.3V).

This device operates with a quasi-fixed 1.5MHz pulse width modulation (PWM) mode for moderate or heavy loads. But at light loads, pulse skip modulation is used for power-save mode (PSM). The PSM operating quiescent current is very low, typically 44µA, which is well suitable for battery powered applications to prolong battery life. Despite such low quiescent current, the transient response to large load variations is excellent. The device shutdown current is less than 0.5µA.

The SGM61020S provides an adjustable output voltage by an external resistor divider. The device is capable for low dropout operation with 100% duty cycle. Some other features include internal soft-start for limiting startup inrush current, over-current and thermal shutdown protections, enable input and power good output (for SGM61020PS version only).

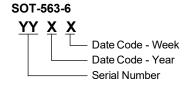

The SGM61020S is available in Green SOT-563-6 and SOT-23-5 packages and the SGM61020PS is available in Green SOT-563-6 and SOT-23-6 packages.

#### **FEATURES**

- 2.5V to 5.5V Input Voltage Range

- Adjustable Output Voltage from 0.6V to V<sub>IN</sub>

- Up to 95% Efficiency

- Low R<sub>DSON</sub> Switches

- SOT-563-6: 83mΩ/48mΩ

- SOT-23-5/SOT-23-6: 99mΩ/51mΩ

- Power-Save Mode for Light Load Efficiency

- 44µA (TYP) Operating Quiescent Current

- 100% Duty Cycle for Low Dropout Operation

- 1.5MHz PWM Switching Frequency

- Power Good Output (SGM61020PS Only)

- Over-Current Protection

- Thermal Shutdown Protection

- Input Under-Voltage Lockout (UVLO) Protection

- -40°C to +125°C Operating Temperature Range

- Small Packaging:

- SGM61020S: Available in Green SOT-563-6 and SOT-23-5 Packages

- SGM61020PS: Available in Green SOT-563-6 and SOT-23-6 Packages

#### **APPLICATIONS**

General Purpose POL Supply Set-Top Box Network Video Camera Wireless Router Hard Disk Driver

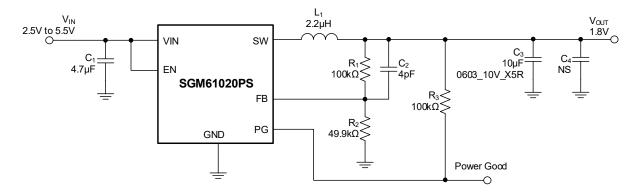

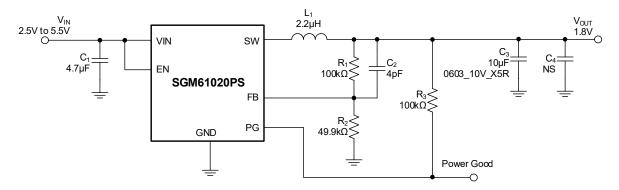

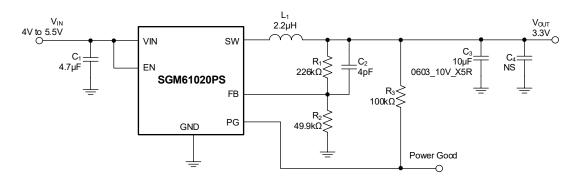

#### TYPICAL APPLICATION

**Figure 1. Typical Application Circuit**

## PACKAGE/ORDERING INFORMATION

| MODEL        | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING | PACKING<br>OPTION   |

|--------------|------------------------|-----------------------------------|--------------------|--------------------|---------------------|

| SGM61020S    | SOT-563-6              | -40°C to +125°C                   | SGM61020SXKB6G/TR  | 03XX               | Tape and Reel, 5000 |

| 3GW010203    | SOT-23-5               | -40°C to +125°C                   | SGM61020SXN5G/TR   | 031XX              | Tape and Reel, 3000 |

| SGM61020PS - | SOT-563-6              | -40°C to +125°C                   | SGM61020PSXKB6G/TR | 02XX               | Tape and Reel, 5000 |

|              | SOT-23-6               | -40°C to +125°C                   | SGM61020PSXN6G/TR  | 0GGXX              | Tape and Reel, 3000 |

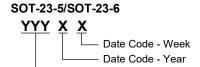

#### MARKING INFORMATION

NOTE: XX = Date Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

Serial Number

| Voltage Range <sup>(1)</sup>      |                                |

|-----------------------------------|--------------------------------|

| VIN, EN, PG                       | 0.3V to 6V                     |

| SW (DC)                           | 0.3V to V <sub>IN</sub> + 0.3V |

| SW (AC, Less than 10ns) (2)       | 2V to 9V                       |

| FB                                | 0.3V to 5.5V                   |

| Package Thermal Resistance        |                                |

| SOT-563-6, θ <sub>JA</sub>        | 135.8°C/W                      |

| SOT-563-6, θ <sub>JB</sub>        | 38°C/W                         |

| SOT-563-6, θ <sub>JC</sub>        | 71.7°C/W                       |

| SOT-23-5, θ <sub>JA</sub>         | 172°C/W                        |

| SOT-23-5, θ <sub>JB</sub>         | 36.9°C/W                       |

| SOT-23-5, θ <sub>JC</sub>         | 61.9°C/W                       |

| SOT-23-6, θ <sub>JA</sub>         | 157°C/W                        |

| SOT-23-6, θ <sub>JB</sub>         | 34.8°C/W                       |

| SOT-23-6, θ <sub>JC</sub>         | 64.3°C/W                       |

| Junction Temperature              | +150°C                         |

| Storage Temperature Range         | 65°C to +150°C                 |

| Lead Temperature (Soldering, 10s) | +260°C                         |

| ESD Susceptibility                |                                |

| HBM                               | 4000V                          |

| CDM                               | 1000V                          |

| NOTES:                            |                                |

#### NOTES:

1. All voltage values are with respect to the ground terminal.

2. While switching.

#### RECOMMENDED OPERATING CONDITIONS

| Output Voltage Range, V <sub>OUT</sub>       | 0.6V to V <sub>IN</sub> |

|----------------------------------------------|-------------------------|

| Output Current Range, IOUT                   | 0A to 2A                |

| Sink Current at PG Pin, I <sub>SINK_PG</sub> | 1mA                     |

| Operating Junction Temperature Range         | 40°C to +125°C          |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

## **PIN CONFIGURATIONS**

## **PIN DESCRIPTION**

|           | PIN      |          | NAME    | I/O | FUNCTION                                                                                                                                                                       |

|-----------|----------|----------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SOT-563-6 | SOT-23-5 | SOT-23-6 | IVAIVIE | 1/0 | FONCTION                                                                                                                                                                       |

| 1         | 5        | 6        | FB      | I   | Feedback Input. Use a resistor divider to feedback the output voltage to this pin and set the voltage.                                                                         |

| 2         | 2        | 2        | GND     | G   | Ground Pin.                                                                                                                                                                    |

| 3         | 4        | 4        | VIN     | Р   | Power Supply Input. Decouple VIN with at least 4.7µF ceramic capacitor to GND, close to the device. (If the input voltage oscillates, the input capacitance can be increased.) |

| 4         | 3        | 3        | SW      | 0   | Switching Node Output Pin. Connect to the filter inductor.                                                                                                                     |

| 5         | 1        | 1        | EN      | l   | Active High Enable Input. Apply a logic low to shut down the device or pull EN up to VIN to enable it. Do not leave EN floating.                                               |

|           |          | _        | NC      |     | No Connection. This pin can be left open or connected to GND.                                                                                                                  |

| 6         | _        | 5        | PG      | 0   | Open-Drain Power Good Output (SGM61020PS Only). Pull it up with a resistor to a positive voltage no more than 5.5V. It can be left open if unused.                             |

NOTE: I = input, O = output, P = power, G = ground.

## **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 5.0V, T_J = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ and typical values are at } T_J = +25^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETER                           | SYMBOL              | COI                                                                | NDITIONS                         | MIN   | TYP                       | MAX   | UNITS |  |

|-------------------------------------|---------------------|--------------------------------------------------------------------|----------------------------------|-------|---------------------------|-------|-------|--|

| Power Supply                        | •                   | •                                                                  |                                  |       |                           |       |       |  |

|                                     |                     | Not switching,                                                     | T <sub>J</sub> = +25°C           |       | 44                        | 60    |       |  |

| Quiescent Current into VIN Pin      | lα                  | $V_{IN} = 2.5V \text{ to } 5.5V$                                   | T <sub>J</sub> = -40°C to +125°C |       |                           | 74    | μΑ    |  |

|                                     |                     | EN = 0V,                                                           | T <sub>J</sub> = +25°C           |       | 0.035                     | 0.5   |       |  |

| Shutdown Current into VIN Pin       | I <sub>SD</sub>     | $V_{IN} = 2.5V \text{ to } 5.5V$                                   | T <sub>J</sub> = -40°C to +125°C |       |                           | 2     | μA    |  |

| Under-Voltage Lockout Threshold     | V <sub>UVLO</sub>   | $V_{IN}$ falling, $T_J = -40$                                      | °C to +125°C                     |       | 2.3                       | 2.4   | V     |  |

| Under-Voltage Lockout Hysteresis    | V <sub>HYS</sub>    |                                                                    |                                  |       | 100                       |       | mV    |  |

| Thormal Chutdour                    | _                   | Junction temperate                                                 | ure rising                       |       | 150                       |       | - °C  |  |

| Thermal Shutdown                    | T <sub>JSD</sub>    | Junction temperate                                                 | ure falling                      |       | 130                       |       |       |  |

| Logic Interface                     |                     |                                                                    |                                  |       |                           |       |       |  |

| High-Level Threshold at EN Pin      | V <sub>IH</sub>     | V <sub>IN</sub> = 2.5V to 5.5V                                     |                                  |       |                           | 1.2   | V     |  |

| Low-Level Threshold at EN Pin       | V <sub>IL</sub>     | V <sub>IN</sub> = 2.5V to 5.5V                                     | 0.4                              |       |                           | V     |       |  |

| Soft Startup Time                   | tss                 | Measure from 0 to                                                  | 95% × V <sub>OUT</sub> (set)     |       | 900                       |       | μs    |  |

| Output                              |                     |                                                                    |                                  |       |                           |       |       |  |

| Foodback Bowletine Valtoria         | V                   | T <sub>J</sub> = +25°C                                             | 0.595                            | 0.600 | 0.605                     | V     |       |  |

| Feedback Regulation Voltage         | V <sub>FB</sub>     | $T_{\rm J} = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}$ |                                  | 0.592 |                           | 0.608 | v     |  |

| High-side FET On-Resistance         |                     | SOT-23-5 and SOT-23-6                                              |                                  |       | 99                        |       |       |  |

| night-side FET Off-Resistance       | - R <sub>DSON</sub> | SOT-563-6                                                          |                                  |       | 83                        |       | — mΩ  |  |

| Low-side FET On-Resistance          | NDSON               | SOT-23-5 and SO                                                    |                                  | 51    |                           |       |       |  |

| Low-side FET Off-Resistance         |                     | SOT-563-6                                                          |                                  |       | 48                        |       |       |  |

| High-side FET Current Limit         | I <sub>LIM</sub>    | SOT-23-5 and SOT-23-6                                              |                                  | 3.1   | 3.5                       | 3.9   | A     |  |

| Tright-side FET Current Limit       | ILIM                | SOT-563-6                                                          |                                  | 2.7   | 3.2                       | 3.7   |       |  |

| Switching Frequency                 | fsw                 | V <sub>OUT</sub> = 2.5V                                            |                                  |       | 1.5                       |       | MHz   |  |

| SGM61020PS Only                     |                     |                                                                    |                                  |       |                           |       |       |  |

| Power Good Threshold                | V                   | $V_{\text{FB}}$ rising, referenced to $V_{\text{FB}}$ nominal      |                                  |       | 95% ×<br>V <sub>REF</sub> |       | V     |  |

| 1 OWEL GOOD THESHOLD                | $V_{PG}$            | V <sub>FB</sub> falling, referenced to V <sub>FB</sub> nominal     |                                  |       | 90% ×<br>V <sub>REF</sub> |       |       |  |

| Power Good Low-Level Output Voltage | V <sub>PG_OL</sub>  | I <sub>SINK</sub> = 1mA                                            |                                  |       | 0.1                       | 0.4   | V     |  |

| Input Leakage Current into PG Pin   | I <sub>PG_LKG</sub> | V <sub>PG</sub> = 5.0V                                             |                                  |       | 0.01                      |       | μΑ    |  |

| Dower Cood Deloy Time               |                     |                                                                    | OT-23-5 and SOT-23-6             |       | 43                        |       | ,     |  |

| Power Good Delay Time               | t <sub>PG_DLY</sub> | V <sub>FB</sub> falling                                            | OT-563-6                         |       | 32                        |       | μs    |  |

## TYPICAL PERFORMANCE CHARACTERISTICS

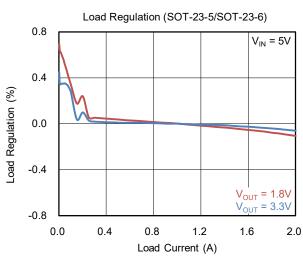

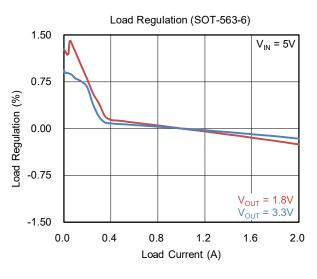

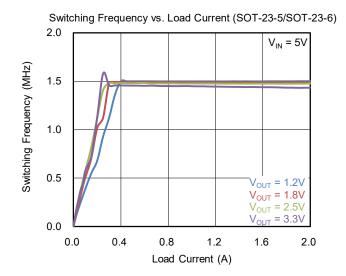

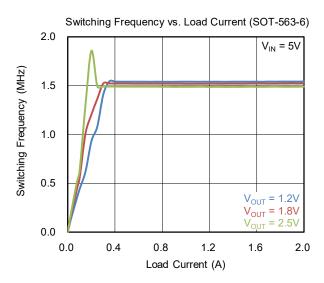

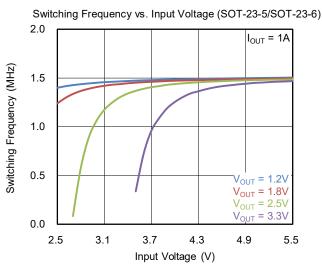

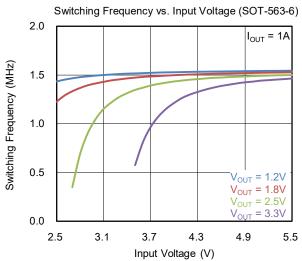

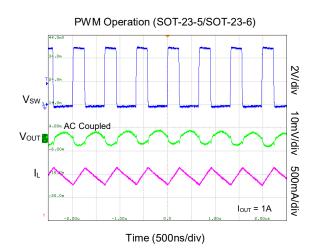

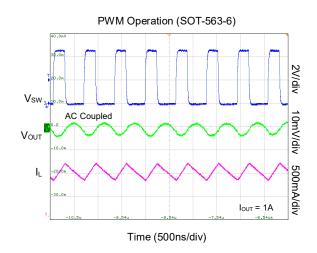

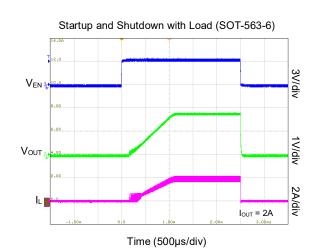

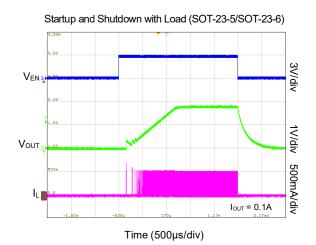

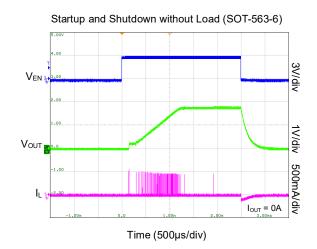

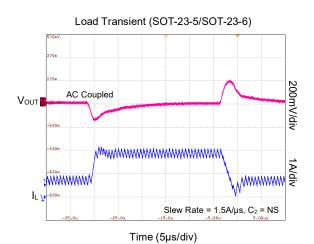

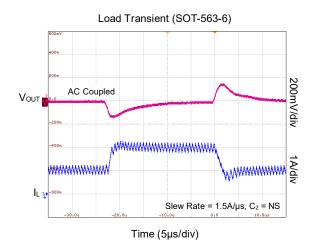

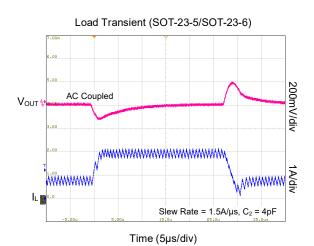

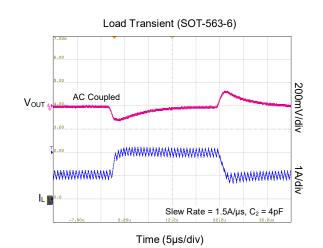

$T_A$  = +25°C,  $V_{IN}$  = 5V,  $V_{OUT}$  = 1.8V,  $L_1$  = 2.2 $\mu$ H,  $C_{OUT}$  = 10 $\mu$ F and DCR = 14 $m\Omega$ , unless otherwise noted.

$T_A$  = +25°C,  $V_{IN}$  = 5V,  $V_{OUT}$  = 1.8V,  $L_1$  = 2.2 $\mu$ H,  $C_{OUT}$  = 10 $\mu$ F and DCR = 14 $m\Omega$ , unless otherwise noted.

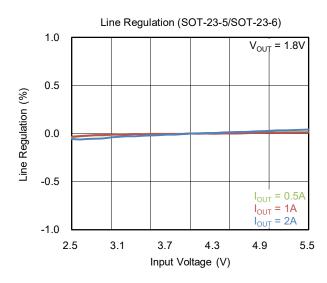

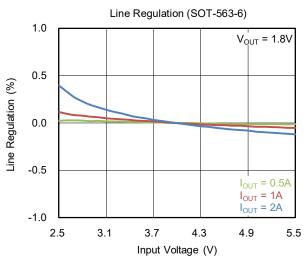

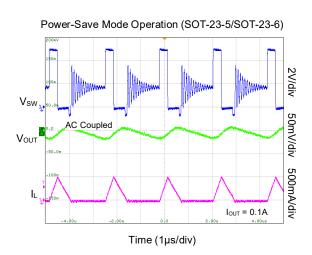

$T_A$  = +25°C,  $V_{IN}$  = 5V,  $V_{OUT}$  = 1.8V,  $L_1$  = 2.2 $\mu$ H and  $C_{OUT}$  = 10 $\mu$ F, unless otherwise noted.

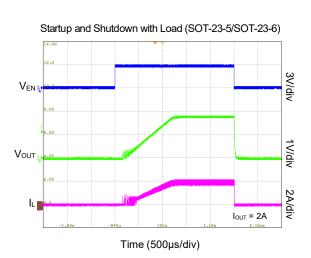

$T_A$  = +25°C,  $V_{IN}$  = 5V,  $V_{OUT}$  = 1.8V,  $L_1$  = 2.2 $\mu$ H and  $C_{OUT}$  = 10 $\mu$ F, unless otherwise noted.

$T_A$  = +25°C,  $V_{IN}$  = 5V,  $V_{OUT}$  = 1.8V,  $L_1$  = 2.2 $\mu$ H and  $C_{OUT}$  = 10 $\mu$ F, unless otherwise noted.

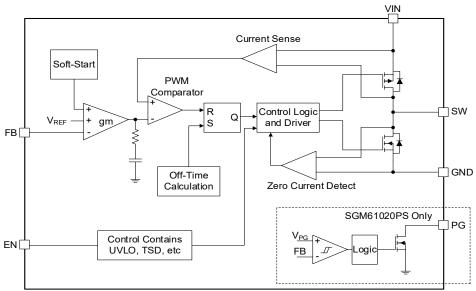

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. SGM61020S/SGM61020PS Block Diagram

#### DETAILED DESCRIPTION

The SGM61020S is a high efficiency Buck switching regulator optimized for handheld battery-powered applications. It operates at a quasi-fixed frequency of 1.5MHz and uses adaptive off-time PWM control for the moderate to heavy load range. This allows using a small inductor and small capacitors for compact designs. At light load condition, this device operates in power-save mode (PSM) to reduce the switching frequency and losses for longer battery life. The PSM quiescent current is typically  $44\mu A$  while the shutdown current is less than  $0.5\mu A$  (MAX).

#### **Under-Voltage Lockout Protection**

When the input voltage is below the UVLO threshold (2.3V, TYP), the device is shut down. If the input voltage rises above the UVLO threshold plus hysteresis, the IC will restart.

#### **Enable Input**

EN is a digital control pin that turns the regulator on and off. Drive EN high to turn on the regulator and drive it low to turn it off. Connect the EN pin directly to a voltage source that cannot be higher than the VIN pin. The EN input should not be left floating.

#### **Soft Startup**

A 900 $\mu$ s internal soft-start circuit is included to prevent input inrush current and voltage drops during startup. This circuit slowly ramps up the error amplifier reference voltage (V<sub>REF</sub> = 0.6V) after exiting the shutdown state or under-voltage lockout (UVLO). Slow increase of the output voltage prevents the excessive inrush current for charging the output capacitors and creates a smooth output voltage rise. The other advantage of a soft-start is avoiding supply voltage drops especially on the high internal impedance sources such as the primary cells and rechargeable batteries.

The device is also capable of starting with a pre-biased output capacitor when it is powering up or enabled. When the device is turning on, a bias on the output may exist due to the other sources connected to the load(s) such as multi-voltage ICs or simply because of residual charges on the output capacitors. For example, when a device with light load is disabled and re-enabled, the output may not drop during the off period and the device must restart under pre-biased output condition. Without the pre-biased capability, the device may not be able to start up properly. The output ramp is automatically initiated with the bias voltage and ramps up to the nominal output value.

## **DETAILED DESCRIPTION (continued)**

#### Power Good Output (SGM61020PS Only)

The PG pin is an open-drain output. PG requires a pull-up resistor (e.g.  $100k\Omega$ ). PG pin is pulled to GND before the output voltage is above 95% of the nominal voltage. After FB voltage reaches 95% of V<sub>REF</sub>, the PG pin is pulled high immediately. When the FB voltage drops below 90% of V<sub>REF</sub>, the PG pin will be pulled low after a 43µs delay. Leave the PG pin unconnected when not used.

Table 1. PG Output Logic

| Device Co            | Logic Status                                      |          |   |  |

|----------------------|---------------------------------------------------|----------|---|--|

| Device Co            | Hi-Z                                              | Low      |   |  |

| Enable               | EN = high, V <sub>FB</sub> ≥ V <sub>PG</sub>      | √        |   |  |

|                      | EN = high, V <sub>FB</sub> ≤ V <sub>PG</sub>      |          | ~ |  |

| Shutdown             | EN = low                                          |          | √ |  |

| Thermal Shutdown     | hermal Shutdown T <sub>A</sub> > T <sub>JSD</sub> |          | ~ |  |

| UVLO                 | VLO 1.4V < V <sub>IN</sub> < V <sub>UVLO</sub>    |          | √ |  |

| Power Supply Removal | V <sub>IN</sub> ≤ 1.4V                            | <b>√</b> |   |  |

#### **Power-Save Mode (PSM)**

At light load condition, the SGM61020S shifts to the PSM mode and operates with pulse skip modulation to reduce the switching frequency and minimize the losses. It also shuts down most of the internal circuits in PSM. In this mode, one or more PWM pulses are sent to charge the output capacitor and then the switches are kept off. The output capacitor voltage gradually drops due to small load current and when it falls below the nominal voltage threshold, the PWM pulses resume. If the load is still low, the output will go slightly higher than normal again and the switches will turn off. In power-save mode, the output voltage is slightly higher than nominal output voltage. This effect can be mitigated by a larger output capacitor.

#### **Low Dropout Operation (100% Duty Cycle)**

When the input voltage reduces, the on-time increases. When the input voltage is lower than the regulation output voltage, the output voltage drops, and the SGM61020S goes into 100% duty cycle mode. The high-side switch is always on, and the output voltage is determined by the load current times the  $R_{\mbox{\scriptsize DSON}}$  composed by the high-side switch and inductor.

#### **Current Limit Protection**

At the beginning of each cycle, the high-side switch is turned on. If the converter is overloaded or a short occurs on the output, the inductor current sensed by the high-side switch exceeds the maximum current limit threshold. Under this condition, the high-side switch is turned off and the on-time is ended to avoid damage. The shortened on-time will result in a reduced output voltage.

Note that the measured peak current limit in the closed-loop and open-loop test conditions is slightly different, mainly due to the current comparator propagation delay.

#### **Thermal Shutdown Protection**

A thermal shutdown function is implemented to prevent damage caused by excessive heat and power dissipation. Once the junction temperature exceeds +150°C, the device is shut down. The device is released from shutdown automatically when the junction temperature decreases by 20°C.

#### APPLICATION INFORMATION

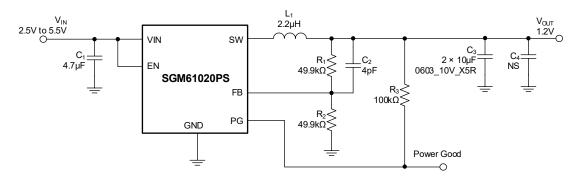

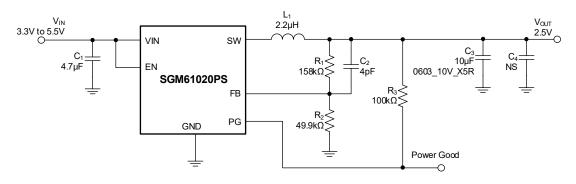

An application circuit schematic of the SGM61020PS with adjustable output is provided in Figure 3.

Figure 3. SGM61020PS Application Example with 1.8V/2.0A Output

#### **Output Voltage Setting**

A resistor divider network ( $R_1$  and  $R_2$  in Figure 3) can be used to set the device output voltage based on the Equation 1. Use a  $49.9k\Omega$  resistor for  $R_2$  to compromise between the quiescent current and the bias error/noise immunity of the FB pin.

$$V_{OUT} = V_{FB} \times (1 + \frac{R_1}{R_2}) = 0.6V \times (1 + \frac{R_1}{R_2})$$

(1)

When  $V_{\text{IN}}$  decreases to near  $V_{\text{OUT}}$  value, the switching frequency is decreased and the duty cycle is increased until it reaches 100%.

A feed-forward capacitor ( $C_2$ ) can be placed in parallel with  $R_1$  to improve the bandwidth and achieve faster transient response and reduce the  $V_{OUT}$  ripple in PSM.

#### **Output Capacitor Design**

For the device, the output capacitance is generally designed to limit the output voltage ripple below the required level.  $C_{\text{OUT}}$  also reduces the voltage transients when fast load changes occur. The inductor ripple current that is absorbed by  $C_{\text{OUT}}$  is determined by L,  $V_{\text{OUT}}$  and  $V_{\text{IN}}$ . The output voltage ripple is determined by the interaction of inductor current ripple with the capacitor impedance including its capacitance ( $C_{\text{OUT}}$ ), ESR and ESL values.

During a load transient, the output capacitor provides or absorbs the extra load current alone that results in a droop or quick rise in its voltage, until the loop can respond, and the inductor average current reaches the new load level. The  $C_{OUT}$  capacitance determines the transient magnitude. Bias Voltage may cause capacitance decreasing significantly if ceramic capacitors are used. The effective deviation of a ceramic capacitor can be as high as -50% to +20% of the nominal value.

Note that high ripple current in the capacitor ESR can cause high temperature due to power dissipation in the capacitor. High operating temperature shortens the capacitor lifetime. Therefore, the maximum allowed ripple current in the capacitor that depends on the ambient temperature must not be exceeded.

Low ESL capacitors can be chosen if ringing in the low megahertz region is seen. Limiting the trace lengths on the PCB or replacing large capacitors with several smaller parallel ones can also help.

To have small output ripple and stable regulation loop, use low-ESR X5R or X7R ceramic capacitors with high ripple current ratings.

The output ripple caused by limited  $C_{\text{OUT}}$  capacitance and its parasitic ESR can be calculated from Equation  $2^{\cdot}$

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{f_{\text{SW}} \times L} \times (1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}) \times (\text{RESR} + \frac{1}{8 \times f_{\text{SW}} \times C_{\text{OUT}}}) \quad \text{(2)}$$

In this example, a  $10\mu F\_10V\_X5R\_0603$  Ceramic capacitor is used.

## **APPLICATION INFORMATION (continued)**

#### **Inductor Design and Selection**

In most cases, a 1µH to 2.2µH inductor works well for the device. Typically, a lower value inductor has a smaller physical size but may result in higher loss due to higher switching frequency required (the lower DCR may compensate for that at heavy loads). For a required ripple ( $\Delta$ IL), the inductor can be chosen based on Equation 3:

$$L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times \Delta I_{L} \times f_{SW}}$$

(3)

Typically, the  $\Delta I_L$  is chosen around 10% to 30% of the maximum load current. For lower output voltage settings, it is recommended to use 1 $\mu$ H inductor to achieve good response and stability.

Inductor manufacturers usually provide thermal current rating (I<sub>RMS</sub>) and saturation current rating (I<sub>SAT</sub>). Choose the I<sub>SAT</sub> above the (I<sub>LOAD,MAX</sub> +  $\Delta$ I<sub>L</sub>/2) × 1.2 to avoid saturation.

The inductor DCR is also an important factor for efficiency and loss consideration. For better efficiency, SGMICRO suggests to choose the DCR of the inductor as small as possible. More generally, choosing the saturation current above high-side limit is enough.

#### Input Capacitor Design

The input capacitor provides the converter pulsating and high frequency input currents, and decouples them from the input line. The  $C_{\rm IN}$  impedance at the switching frequency should be very low and less than the source impedance to filter the switching currents and prevent them from flowing in the input source. The input voltage ripple must be small for proper regulation and stability. The following Equation 4 can be used to calculate  $C_{\rm IN}$  based on the required peak-to-peak input ripple ( $V_{\rm IN}$ ).

$$C_{IN} = \frac{\frac{V_{OUT}}{V_{IN}} \times (1 - \frac{V_{OUT}}{V_{IN}})}{\frac{\Delta V_{IN}}{I_{LOAD}} \times f_{SW}}$$

(4)

The worst case, ripple occurs when the duty cycle is near to 50% ( $V_{OUT}/V_{IN} \approx 0.5$ ). Use Equation 5 to calculate  $C_{IN}$ :

$$C_{IN(MIN)} = \frac{1}{\left(\frac{V_{IN}}{I_{LOAD}}\right) \times 4 \times f_{SW}}$$

(5)

Use at least a 4.7 $\mu$ F low-ESR X5R or X7R ceramic capacitor for C<sub>IN</sub>. A 22 $\mu$ F capacitor works well for most applications but for better filtering, a larger capacitor can be used. Consider the capacitor rated RMS current for the design. The C<sub>IN</sub> RMS current is given by Equation 6:

$$I_{RMS} = I_{LOAD} \times \sqrt{\frac{V_{OUT}}{V_{IN}}} \times (1 - \frac{V_{OUT}}{V_{IN}})$$

(6)

In worst case,  $I_{\text{RMS}}$  is equal to 1/2 of the load DC current:

$$I_{RMS(MAX)} = \frac{1}{2} \times I_{LOAD}$$

(7)

Note that using long test leads for powering the converter on a lab bench can cause stability issues such as excessive ringing in the output during load transients. It is due to the large inductance of such wires that along with the low-ESR ceramic input capacitors create a high-Q network. Moreover, it can cause errors in loop phase and gain measurements. It is not the case in normal applications with short PCB traces feeding the input. However, if in an application the input inductance cannot be reduced, a high-ESR tantalum or aluminum electrolytic capacitor must be used in parallel with the low-ESR ceramic capacitors to stabilize the system by added the damping to the high-Q network.

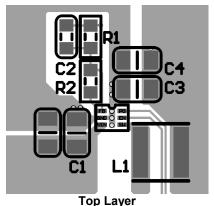

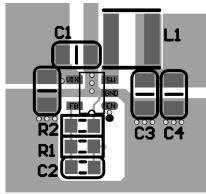

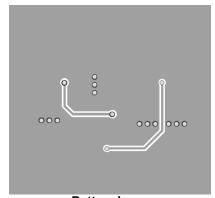

### LAYOUT CONSIDERATIONS

Some important PCB layout design considerations for the SGM61020S are listed below:

- Place the low-ESR input/output capacitors and the inductor as close as possible to the device with short, wide and direct traces on the same layer.

- · Connect the GND terminal of the input and output capacitors together and to the device GND pin and the GND power plane in one point.

- · Keep the FB feedback traces away from noisy elements or traces such as the SW node.

- · Use GND layers under the device, switching traces and inductor for better shielding.

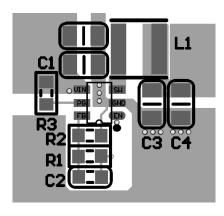

Figure 4. SOT-563-6 PCB Layout

**Bottom Layer**

Top Layer

**Bottom Layer**

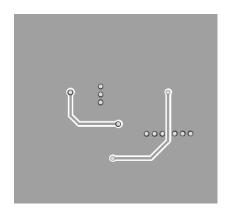

Figure 5. SOT-23-5 PCB Layout

**Top Layer**

**Bottom Layer**

Figure 6. SOT-23-6 PCB Layout

## ADDITIONAL TYPICAL APPLICATION CIRCUITS

Figure 7. 1.2V Output Voltage Application

Figure 8. 2.5V Output Voltage Application

Figure 9. 3.3V Output Voltage Application

### **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| OCTOBER 2024 – REV.A to REV.A.1                 | Page |

|-------------------------------------------------|------|

| Added SOT-563-6 package                         | All  |

|                                                 | _    |

| Changes from Original (NOVEMBER 2023) to REV.A  | Page |

| Changed from Product Preview to Production Data | All  |

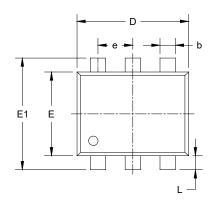

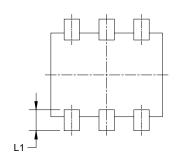

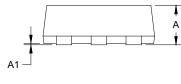

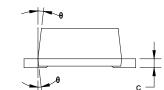

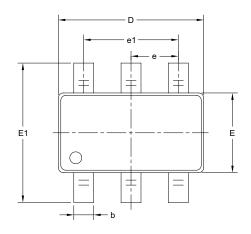

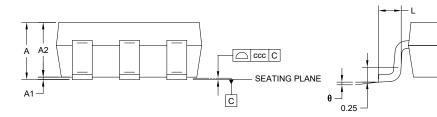

## **PACKAGE OUTLINE DIMENSIONS** SOT-563-6

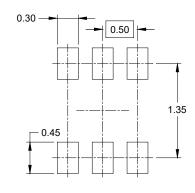

RECOMMENDED LAND PATTERN (Unit: mm)

| Symbol | _     | isions<br>meters | Dimensions<br>In Inches |       |  |

|--------|-------|------------------|-------------------------|-------|--|

|        | MIN   | MAX              | MIN                     | MAX   |  |

| Α      | 0.525 | 0.600            | 0.021                   | 0.024 |  |

| A1     | 0.000 | 0.050            | 0.000                   | 0.002 |  |

| b      | 0.170 | 0.270            | 0.007                   | 0.011 |  |

| С      | 0.090 | 0.180            | 0.004                   | 0.007 |  |

| D      | 1.500 | 1.700            | 0.059                   | 0.067 |  |

| E      | 1.100 | 1.300            | 0.043                   | 0.051 |  |

| E1     | 1.500 | 1.700            | 0.059                   | 0.067 |  |

| е      | 0.450 | 0.550            | 0.018                   | 0.022 |  |

| L      | 0.100 | 0.300            | 0.004                   | 0.012 |  |

| L1     | 0.200 | 0.400            | 0.008                   | 0.016 |  |

| θ      | 9° F  | REF              | 9° F                    | REF   |  |

- Body dimensions do not include mode flash or protrusion.

This drawing is subject to change without notice.

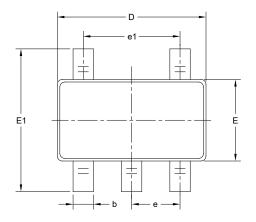

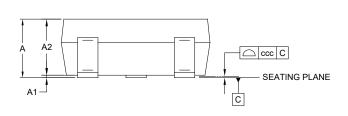

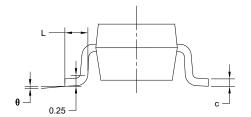

# PACKAGE OUTLINE DIMENSIONS SOT-23-5

RECOMMENDED LAND PATTERN (Unit: mm)

| Cumbal | Dimensions In Millimeters |           |       |  |  |  |  |

|--------|---------------------------|-----------|-------|--|--|--|--|

| Symbol | MIN                       | NOM       | MAX   |  |  |  |  |

| А      | -                         | -         | 1.450 |  |  |  |  |

| A1     | 0.000                     | -         | 0.150 |  |  |  |  |

| A2     | 0.900                     | -         | 1.300 |  |  |  |  |

| b      | 0.300                     | -         | 0.500 |  |  |  |  |

| С      | 0.080                     | -         | 0.220 |  |  |  |  |

| D      | 2.750                     | -         | 3.050 |  |  |  |  |

| E      | 1.450                     | -         | 1.750 |  |  |  |  |

| E1     | 2.600                     | -         | 3.000 |  |  |  |  |

| е      |                           | 0.950 BSC |       |  |  |  |  |

| e1     |                           | 1.900 BSC |       |  |  |  |  |

| L      | 0.300                     | -         | 0.600 |  |  |  |  |

| θ      | 0°                        | -         | 8°    |  |  |  |  |

| ccc    |                           | 0.100     |       |  |  |  |  |

#### NOTES

- 1. This drawing is subject to change without notice.

- 2. The dimensions do not include mold flashes, protrusions or gate burrs.

- 3. Reference JEDEC MO-178.

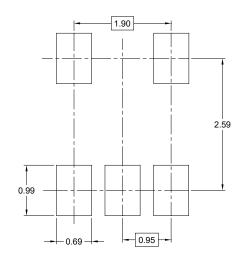

# PACKAGE OUTLINE DIMENSIONS SOT-23-6

RECOMMENDED LAND PATTERN (Unit: mm)

| Symbol | Dimensions In Millimeters |           |       |  |  |  |  |

|--------|---------------------------|-----------|-------|--|--|--|--|

| Symbol | MIN                       | NOM       | MAX   |  |  |  |  |

| Α      | -                         | -         | 1.450 |  |  |  |  |

| A1     | 0.000                     | 0.150     |       |  |  |  |  |

| A2     | 0.900                     | 0.900 -   |       |  |  |  |  |

| b      | 0.300                     | 0.300 -   |       |  |  |  |  |

| С      | 0.080 -                   |           | 0.220 |  |  |  |  |

| D      | 2.750                     | -         | 3.050 |  |  |  |  |

| E      | 1.450 -                   |           | 1.750 |  |  |  |  |

| E1     | 2.600                     | 3.000     |       |  |  |  |  |

| е      |                           | 0.950 BSC |       |  |  |  |  |

| e1     |                           | 1.900 BSC |       |  |  |  |  |

| L      | 0.300                     | 0.300 -   |       |  |  |  |  |

| θ      | 0°                        | -         | 8°    |  |  |  |  |

| ccc    |                           | 0.100     |       |  |  |  |  |

#### **NOTES**

- 1. This drawing is subject to change without notice.

- 2. The dimensions do not include mold flashes, protrusions or gate burrs.

- 3. Reference JEDEC MO-178.

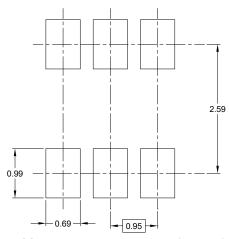

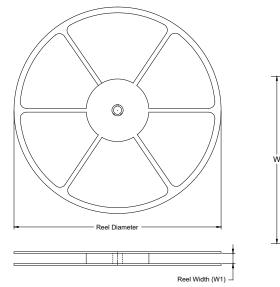

## TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

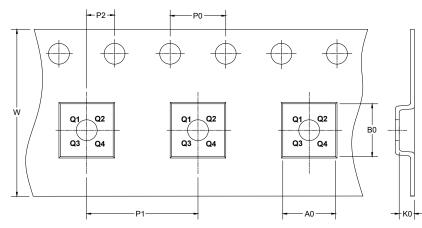

## **TAPE DIMENSIONS**

DIRECTION OF FEED

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| SOT-563-6    | 7"               | 9.5                      | 1.78       | 1.78       | 0.69       | 4.0        | 4.0        | 2.0        | 8.0       | Q3               |

| SOT-23-5     | 7"               | 9.5                      | 3.20       | 3.20       | 1.40       | 4.0        | 4.0        | 2.0        | 8.0       | Q3               |

| SOT-23-6     | 7"               | 9.5                      | 3.23       | 3.17       | 1.37       | 4.0        | 4.0        | 2.0        | 8.0       | Q3               |

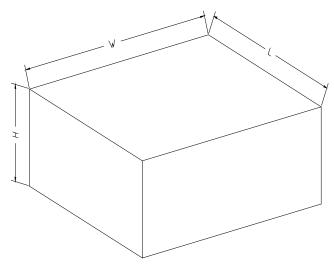

## **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

## **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type   | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |        |

|-------------|----------------|---------------|----------------|--------------|--------|

| 7" (Option) | 368            | 227           | 224            | 8            |        |

| 7"          | 442            | 410           | 224            | 18           | DD0002 |