# SGM41606S I<sup>2</sup>C Controlled, Single-Cell 8A Switched Cap Parallel Battery Charger with Bypass Mode and Dual-Input Selector

### GENERAL DESCRIPTION

The SGM41606S is an efficient 8A switched-capacitor battery charging device with I<sup>2</sup>C control that can operate either in charge-pump voltage divider mode or in bypass mode. It can charge single-cell Li-lon or Li-polymer battery in a wide 3.6V to 12V input voltage range (VBUS) from smart wall adapters or power banks. The switched-capacitor architecture is optimized for 50% duty cycle to cut the input current to one-half of the battery current and reduce the wiring drops, losses and temperature rise in the application.

The SGM41606S is equipped with the capability to facilitate a 5A bypass mode charge, formerly known as battery switch charge, via its built-in MOSFETs. The  $R_{DSON}$  value for the charging path in bypass mode is kept under  $17m\Omega$  (TYP) to accommodate high current operations. This integrated bypass mode ensures that a 5V fast charging adapter can be used to charge a single-cell battery, thereby maintaining backward compatibility.

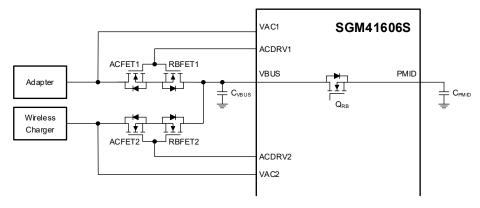

The SGM41606S is designed to support a dual input setup using an integrated multiplexer control and driver for external OVPFETs. Additionally, it also supports single input without OVPFET or with just a single OVPFET.

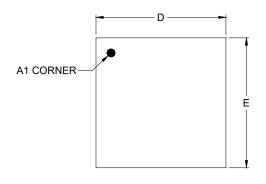

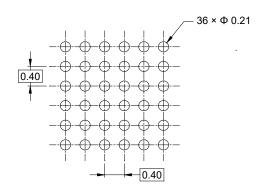

The SGM41606S is available in a Green WLCSP-2.65×2.65-36B-A package.

### **APPLICATIONS**

Smartphone, Tablet

### **FEATURES**

- Efficiency Optimized Switched-Capacitor Architecture

- Up to 8A Output Current

- 3.6V to 12V Input Voltage Range

- 187.5kHz to 1.5MHz Switching Frequency Setting

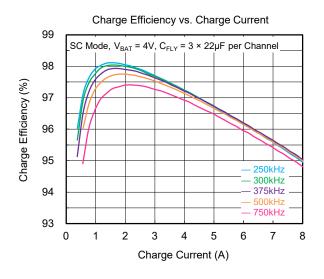

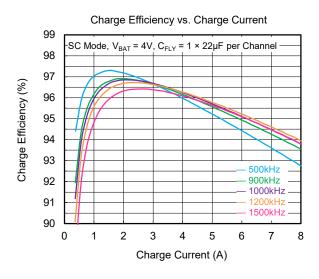

- Above 98% Voltage Divider Mode Efficiency (when V<sub>BAT</sub> = 4V, I<sub>BAT</sub> = 2A)

- Dual-Input Power Mux Controller for Source Selection

- Integrated Programmable Protection Features for Safe Operation

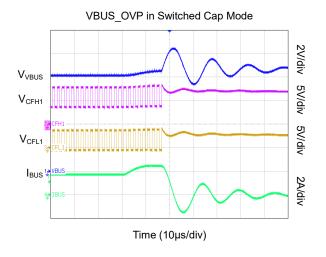

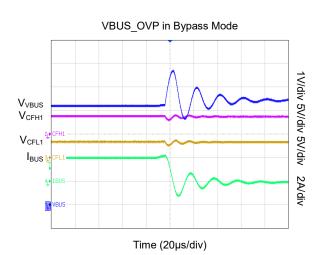

- Input Over-Voltage Protection (VBUS\_OVP)

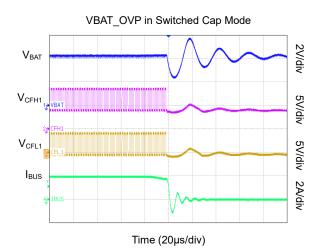

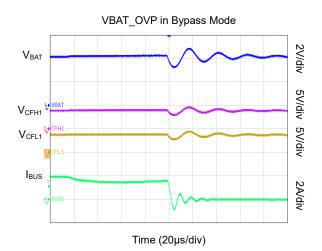

- Battery Over-Voltage Protection (VBAT\_OVP)

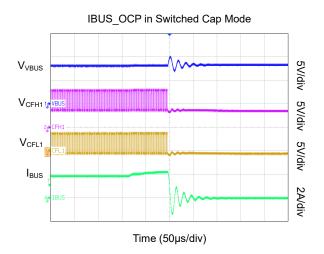

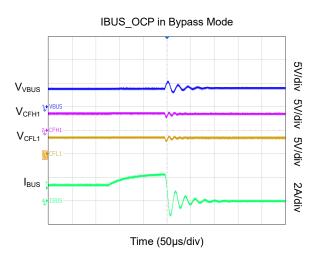

- Input Over-Current Protection (IBUS\_OCP)

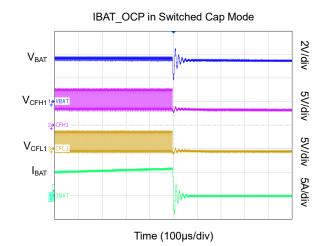

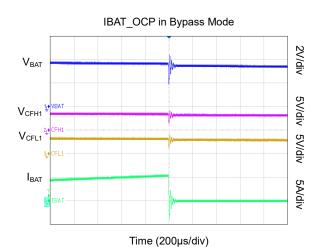

- Battery Over-Current Protection (IBAT\_OCP)

- Input Under-Current Protection (IBUS\_UCP)

- Input Short-Circuit Protection (VBUS\_SCP)

- Output Over-Voltage Protection (VOUT\_OVP)

- Battery and Cable Connector Temperature Monitoring (TSBAT\_FLT and TSBUS\_FLT)

- Die Over-Temperature Protection (TDIE OTP)

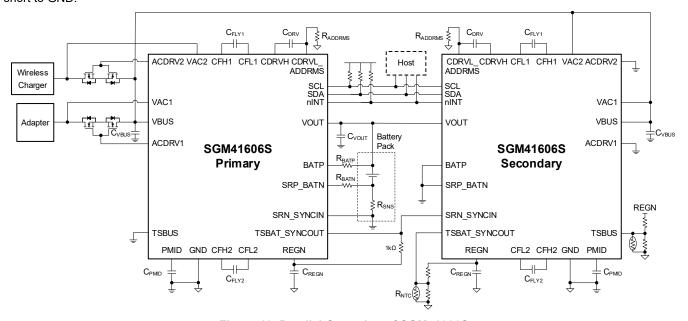

- Up to 13A Charging Current with Synchronized Dual SGM41606S for Parallel Charging

- 10-Channel 16-Bit (Effective) ADC Converter

- VAC1, VAC2, VBUS, IBUS, VOUT, VBAT, IBAT, TSBUS, TSBAT, TDIE for Monitoring

### PACKAGE/ORDERING INFORMATION

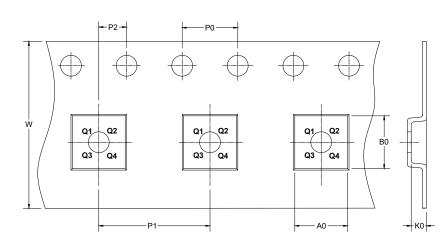

| MODEL     | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING              | PACKING<br>OPTION   |

|-----------|------------------------|-----------------------------------|--------------------|---------------------------------|---------------------|

| SGM41606S | WLCSP-2.65×2.65-36B-A  | -40°C to +85°C                    | SGM41606SYG/TR     | SGM<br>41606S<br>XXXXX<br>XX#XX | Tape and Reel, 3000 |

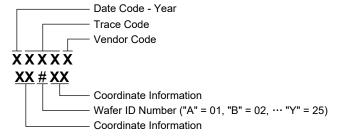

### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code. XX#XX = Coordinate Information and Wafer ID Number.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

### **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range (with Respect to GND) VAC1, VAC2 (Converter not Switching) | 0.3V to 35V    |

|--------------------------------------------------------------------------|----------------|

| VBUS (Converter not Switching)                                           | 0.3V to 22V    |

| PMID (Converter not Switching)                                           | 0.3V to 22V    |

| ACDRV1/ACDRV2 to VBUS                                                    | 22V to 6V      |

| PMID to VBUS                                                             | 0.3V to 6V     |

| CFL1, CFL2                                                               | 0.3V to 6V     |

| CFH1, CFH2 while CFHx - VOUT = 6V (MAX)                                  |                |

|                                                                          | 0.3V to 12V    |

| VOUT                                                                     | 0.3V to 6V     |

| BATP, REGN, nINT, SDA, SCL, CDRVL_ADDI                                   | RMS,           |

| SRN_SYNCIN, TSBAT_SYNCOUT, TSBUS                                         | 0.3V to 6V     |

| CDRVH                                                                    | 0.3V to 22V    |

| SRP_BATN                                                                 | 0.3V to 1.8V   |

| Package Thermal Resistance                                               |                |

| WLCSP-2.65×2.65-36B-A, θ <sub>JA</sub>                                   | 36.4°C/W       |

| WLCSP-2.65×2.65-36B-A, θ <sub>JB</sub>                                   | 4.4°C/W        |

| WLCSP-2.65×2.65-36B-A, θ <sub>JC</sub>                                   | 9.8°C/W        |

| Junction Temperature                                                     | +150°C         |

| Storage Temperature Range6                                               | 65°C to +150°C |

| Lead Temperature (Soldering, 10s)                                        | +260°C         |

| ESD Susceptibility (1) (2)                                               |                |

| HBM                                                                      | ±2000V         |

| CDM                                                                      | ±1500V         |

|                                                                          |                |

#### NOTES:

- 1. For human body model (HBM), all pins comply with ANSI/ESDA/JEDEC JS-001 specifications.

- 2. For charged device model (CDM), all pins comply with ANSI/ESDA/JEDEC JS-002 specifications.

### RECOMMENDED OPERATING CONDITIONS

| 12V (MAX)    |

|--------------|

| 12V (MAX)    |

| 12V (MAX)    |

|              |

| . 5.5V (MAX) |

|              |

| . 5.5V (MAX) |

|              |

| . 5.5V (MAX) |

|              |

| . 5.5V (MAX) |

| 8A (MAX)     |

| °C to +125°C |

|              |

### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

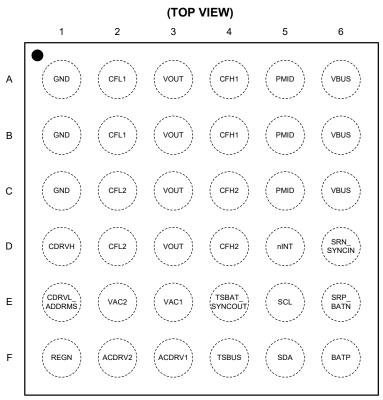

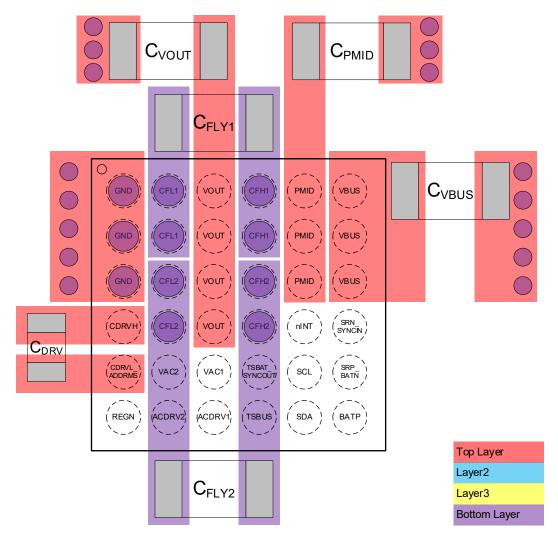

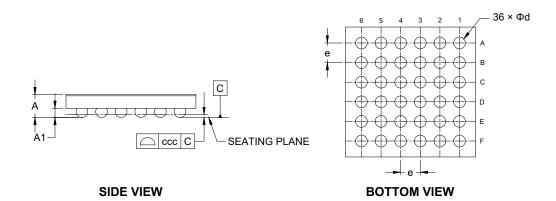

### **PIN CONFIGURATION**

WLCSP-2.65×2.65-36B-A

### **PIN DESCRIPTION**

| PIN               | NAME  | TYPE (1) | FUNCTION                                                                                                                                                                                        |

|-------------------|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, B1, C1        | GND   | Р        | Power Ground Pins.                                                                                                                                                                              |

| A2, B2            | CFL1  | Р        | Channel-1 Flying Capacitor Negative Pins. Connect 2~4 22µF parallel capacitors between CFH1 and CFL1 as close as possible to the device.                                                        |

| A3, B3, C3,<br>D3 | VOUT  | Р        | Device Output Pins. Connect it to the battery pack positive terminal. A 22μF capacitor between VOUT and GND pins is recommended.                                                                |

| A4, B4            | CFH1  | Р        | Channel-1 Flying Capacitor Positive Pins. Connect 2~4 22µF parallel capacitors between CFH1 and CFL1 as close as possible to the device.                                                        |

| A5, B5, C5        | PMID  | Р        | Power Stage Supply Input Pins. Bypass them with at least a 10µF ceramic capacitor to GND.                                                                                                       |

| A6, B6, C6        | VBUS  | Р        | Device Power Input Pins. Use a $1\mu F$ or larger ceramic capacitor between VBUS and GND pins close to the device.                                                                              |

| C2, D2            | CFL2  | Р        | Channel-2 Flying Capacitor Negative Pins. Connect 2~4 22µF parallel capacitors between CFH2 and CFL2 as close as possible to the device.                                                        |

| C4, D4            | CFH2  | Р        | Channel-2 Flying Capacitor Positive Pins. Connect 2~4 22µF parallel capacitors between CFH2 and CFL2 as close as possible to the device.                                                        |

| D1                | CDRVH | AIO      | Charge Pump for Gate Drive. Connect a 0.22µF MLCC capacitor between CDRVH and CDRVL_ADDRMS.                                                                                                     |

| D5                | nINT  | DO       | Open-Drain Interrupt Output Pin. Use a $10k\Omega$ pull-up to the logic high rail. It is normally high but generates a low 256µs pulse when a charge status or fault occurs to inform the host. |

# **PIN DESCRIPTION (continued)**

| PIN | NAME          | TYPE (1)                                                                                                                                                 | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|-----|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| D6  | SRN_SYNCIN    | Al                                                                                                                                                       | Battery Current Sensing Negative Input and SYNCIN for Secondar Configuration. Place a $2m\Omega$ or $5m\Omega$ (R <sub>SNS</sub> ) shunt resistor between SRP_BAT and SRN_SYNCIN pins. Short SRP_BATN and SRN_SYNCIN together to GN if not used. If configured as a secondary IC for parallel charging, this pinctions as SYNCIN, and connect it to TSBAT_SYNCOUT of the primary IC, a well as connect a $1k\Omega$ pull-up resistor from this pin to REGN. |  |  |  |  |  |  |

| E1  | CDRVL_ADDRMS  | AIO                                                                                                                                                      | Charge Pump for Gate Drive. Connect a $0.22\mu F$ MLCC capacitor between CDRVH and CDRVL_ADDRMS. During POR, this pin is also used to assign the $I^2C$ address of the device and the mode of the device as standalone, primary, or secondary.                                                                                                                                                                                                              |  |  |  |  |  |  |

| E2  | VAC2          | Al                                                                                                                                                       | VAC2 Voltage Sense Input Pin. Connect it to VBUS if ACFET2 and RBFET2 are not used.                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| E3  | VAC1          | Al                                                                                                                                                       | VAC1 Voltage Sense Input Pin. Connect it to VBUS if ACFET1 and RBFET1 are not used.                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

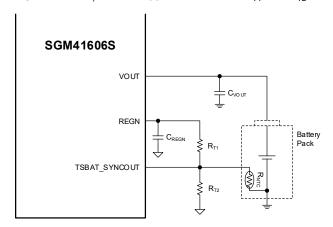

| E4  | TSBAT_SYNCOUT | AI                                                                                                                                                       | Battery Temperature Sense Input and SYNCOUT for Primary Configuration Connect it to the battery NTC thermistor and the external resistor divider that pulled up to REGN. See the TSBAT section for choosing the resister divided values. If configured as a primary IC for parallel charging, this pin functions a SYNCOUT, and is connected to SRN_SYNCIN of the secondary IC.                                                                             |  |  |  |  |  |  |

| E5  | SCL           | DI I <sup>2</sup> C Interface Clock Input Line. The device I <sup>2</sup> C controller block is forced to when receiving 9 clock pulses on the SCL line. |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| E6  | SRP_BATN      | AI                                                                                                                                                       | Battery Voltage Sensing Negative Input or Battery Current Sensing Positive Input. Connect a $100\Omega$ resistor between this pin and negative terminal of the battery pack. Place a $2m\Omega$ or $5m\Omega$ (R <sub>SNS</sub> ) shunt resistor between this pin and SRN_SYNCIN pin. Short this pin and SRN_SYNCIN together if R <sub>SNS</sub> is not used.                                                                                               |  |  |  |  |  |  |

| F1  | REGN          | AO                                                                                                                                                       | Internal 5V LDO Output. Connect a $4.7\mu F$ MLCC capacitor between this pin and GND. In Primary/Secondary mode, connect through $1k\Omega$ resistor to the TSBAT_SYNCOUT pin and SRN_SYNCIN pin. Do not use this pin for any other function.                                                                                                                                                                                                               |  |  |  |  |  |  |

| F2  | ACDRV2        | Р                                                                                                                                                        | External Dual N-MOSFET Gate Control Pin. Connect it to the gate of the external back-to-back N-MOSFET in the port2 charging path, or connect it to ground if the back-to-back N-MOSFET is not used.                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| F3  | ACDRV1        | External Dual N-MOSFET Gate Control Pin. Connect it to the gate of the external                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| F4  | TSBUS         | AI                                                                                                                                                       | BUS Temperature Sense Input. Connect it to the cable connector NTC thermistor and the external resistor divider that is pulled up to REGN. See the TSBUS section for choosing the resister divider values.                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| F5  | SDA           | DIO                                                                                                                                                      | $\rm I^2C$ Interface Data Line. The SDA line is forced to release when the 25ms $\rm I^2C$ timeout fault occurs.                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| F6  | BATP          | Al                                                                                                                                                       | Battery Voltage Sensing Positive Input. Connect a $100\Omega$ resistor between BATP and positive terminal of the battery pack.                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

#### NOTE:

1. P = power, AIO = analog input/output, AI = analog input, DO = digital output, AO = analog output, DIO = digital input/output.

### **ELECTRICAL CHARACTERISTICS**

$(T_J = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ typical values are at } T_J = +25^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETER                                     | SYMBOL                       | CONDITIONS                                                                                                                               | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Supply Currents                               |                              |                                                                                                                                          |      |      |      |       |

| Battery Only Quiescent Current                | I <sub>Q BAT</sub>           | ADC disabled, charge disabled, VBUS, VAC1, VAC2 not present                                                                              |      | 13   | 24   | μA    |

| Battery Only Quiescent Gunont                 | IQ_BAI                       | ADC enabled (slowest mode). charge disabled, VBUS, VAC1, VAC2 not present                                                                |      | 1100 | 1800 | μπ    |

|                                               |                              | ADC disabled, charge disabled, ACDRV disabled, EN_HIZ = 1, V <sub>VAC1</sub> or V <sub>VAC2</sub> = 8V                                   |      | 34   |      |       |

| VAC Quiescent Current                         | $I_{Q\_VAC}$                 | ADC disabled, charge disabled, ACDRV disabled, V <sub>VAC1</sub> or V <sub>VAC2</sub> = 8V ADC disabled, charge disabled, ACDRV enabled, |      | 670  |      | μΑ    |

|                                               |                              | ADC disabled, charge disabled, ACDRV enabled, $V_{VAC1}$ or $V_{VAC2} = 8V$                                                              |      | 950  |      |       |

| VAC UVLO Rising Threshold                     | $V_{AC\_UVLO_R}$             | V <sub>VAC1</sub> or V <sub>VAC2</sub> rising, for active I <sup>2</sup> C                                                               | 3.1  | 3.37 | 3.64 | V     |

| VAC UVLO Falling Threshold                    | $V_{AC\_UVLO\_F}$            | $V_{\text{VAC1}}$ or $V_{\text{VAC2}}$ falling                                                                                           | 2.9  | 3.17 | 3.44 | V     |

| VAC UVLO Hysteresis                           | V <sub>AC_UVLO_HYS</sub>     |                                                                                                                                          |      | 200  |      | mV    |

| VBUS UVLO Rising Threshold                    | V <sub>BUS_UVLO_R</sub>      | V <sub>VBUS</sub> rising, for active I <sup>2</sup> C                                                                                    | 3.05 | 3.35 | 3.6  | V     |

| VBUS UVLO Falling Threshold                   | V <sub>BUS_UVLO_F</sub>      | V <sub>VBUS</sub> falling                                                                                                                | 2.55 | 2.8  | 3.05 | V     |

| VBUS UVLO Hysteresis                          | V <sub>BUS_UVLO_HYS</sub>    |                                                                                                                                          |      | 550  |      | mV    |

| VBUS Present Rising Threshold                 | V <sub>BUS_PRESENT_R</sub>   | V <sub>VBUS</sub> rising to allow user to set CHG_EN = 1                                                                                 | 3.05 | 3.35 | 3.6  | V     |

| VBUS Present Falling Threshold                | V <sub>BUS_PRESENT_F</sub>   | V <sub>VBUS</sub> falling                                                                                                                | 2.85 | 3.15 | 3.4  | V     |

| VBUS Present Hysteresis                       | V <sub>BUS_PRESENT_HYS</sub> |                                                                                                                                          |      | 200  |      | mV    |

| VOUT UVLO Rising Threshold                    | V <sub>OUT_UVLO_R</sub>      | V <sub>VOUT</sub> rising, for active I <sup>2</sup> C                                                                                    | 2.35 | 2.55 | 2.75 | V     |

| VOUT UVLO Falling Threshold                   | V <sub>OUT_UVLO_F</sub>      | V <sub>VOUT</sub> falling                                                                                                                | 2.15 | 2.35 | 2.55 | V     |

| VOUT UVLO Hysteresis                          | V <sub>OUT_UVLO_HYS</sub>    |                                                                                                                                          |      | 200  |      | mV    |

| VOUT Present Rising Threshold                 | V <sub>OUT_PRESENT_R</sub>   | V <sub>VOUT</sub> rising to allow user to set CHG_EN = 1                                                                                 | 2.8  | 3.05 | 3.3  | V     |

| VOUT Present Falling Threshold                | V <sub>OUT_PRESENT_F</sub>   | V <sub>VOUT</sub> falling                                                                                                                | 2.7  | 2.95 | 3.2  | V     |

| VOUT Present Hysteresis                       | V <sub>OUT_PRESENT_HYS</sub> |                                                                                                                                          |      | 100  |      | mV    |

| External OVP Control                          |                              |                                                                                                                                          |      | •    |      |       |

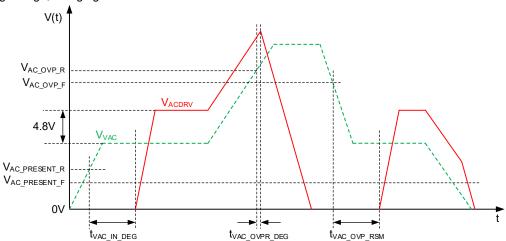

| VAC Present Rising Threshold                  | V <sub>AC_PRESENT_R</sub>    | V <sub>VAC1</sub> or V <sub>VAC2</sub> rising to turn on ACFET- RBFET                                                                    | 3.1  | 3.37 | 3.64 | V     |

| VAC Present Falling Threshold                 | V <sub>AC_PRESENT_F</sub>    | V <sub>VAC1</sub> or V <sub>VAC2</sub> falling                                                                                           | 2.9  | 3.17 | 3.44 | V     |

| VAC Present Hysteresis                        | V <sub>AC_PRESENT_HYS</sub>  |                                                                                                                                          |      | 200  |      | mV    |

| VAC Present Rising Threshold<br>Deglitch Time | t <sub>VAC_IN_DEG</sub>      | Deglitch between $V_{\text{VAC}}$ rising above $V_{\text{AC\_PRESENT\_R}}$ and starting external OVPFET turn-on                          |      | 5    |      | ms    |

| VAC OVP Rising Threshold Range                | $V_{AC\_OVP\_R}$             | V <sub>VAC1</sub> or V <sub>VAC2</sub> rising                                                                                            | 6.5  |      | 18   | V     |

|                                               |                              | $V_{AC1\_OVP\_R}$ or $V_{AC2\_OVP\_R} = 6.5V$                                                                                            |      | 6.5  |      | V     |

| VAC OVP Threshold Accuracy                    | V <sub>AC_OVPR_ACC</sub>     | $V_{AC1\_OVP\_R}$ or $V_{AC2\_OVP\_R} = 10.5V$                                                                                           |      | 10.5 |      |       |

| VAC OVI Trileshold Accuracy                   | V AC_OVPR_ACC                | $V_{AC1\_OVP\_R}$ or $V_{AC2\_OVP\_R} = 12V$                                                                                             |      | 12   |      |       |

|                                               |                              | $V_{AC1\_OVP\_R}$ or $V_{AC2\_OVP\_R} = 18V$                                                                                             |      | 18   |      |       |

| VAC Over-Voltage Hysteresis                   | V <sub>AC_OVP_HYS</sub>      |                                                                                                                                          |      | 3    |      | %     |

| VAC OVP Rising Deglitch Time                  | t <sub>VAC_OVPR_DEG</sub>    | Deglitch between $V_{VAC1}$ or $V_{VAC2}$ rising above $V_{AC\ OVP\ R}$ and triggering the protection action                             |      | 100  |      | ns    |

| VAC OVP Resume Time                           | t <sub>VAC_OVP_RSM</sub>     |                                                                                                                                          |      | 64   |      | μs    |

| VAC Pull-Down Resistance                      | R <sub>PDN_VAC</sub>         | V <sub>VAC1</sub> or V <sub>VAC2</sub> = 10V (Clamp to 35mA)                                                                             |      | 350  |      | Ω     |

| VBUS Pull-Down Resistance                     | R <sub>PDN_VBUS</sub>        | V <sub>VBUS</sub> = 10V                                                                                                                  |      | 6    |      | kΩ    |

| REGN LDO                                      |                              |                                                                                                                                          |      |      |      |       |

| REGN LDO Output Voltage                       | $V_{REGN}$                   | V <sub>VBUS</sub> = 8V, I <sub>REGN</sub> = 20mA                                                                                         |      | 5    |      | V     |

| REGN LDO Current Limit                        | I <sub>REGN</sub>            | V <sub>VBUS</sub> = 8V, V <sub>REGN</sub> = 4.5V                                                                                         | 20   |      |      | mA    |

|                                               |                              |                                                                                                                                          | _    | _    | _    |       |

| PARAMETER                                        | SYMBOL                      |                                                             | CONDITIONS                                                                                          | MIN  | TYP | MAX   | UNITS |

|--------------------------------------------------|-----------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|-----|-------|-------|

| Switched Cap Chargers                            |                             |                                                             |                                                                                                     |      | •   | •     |       |

| VBUS to VOUT Resistance                          | R <sub>DROPOUT</sub>        | Bypass mode                                                 |                                                                                                     |      | 17  |       | mΩ    |

| R <sub>DSON</sub> of Reverse Blocking FET        | R <sub>DS_QRB</sub>         | V <sub>VBUS</sub> = 8V                                      |                                                                                                     |      | 5.3 |       | mΩ    |

| R <sub>DSON</sub> of Q <sub>CH1</sub>            | R <sub>DS_QCH1</sub>        | V <sub>PMID</sub> = 8V                                      |                                                                                                     |      | 20  |       | mΩ    |

| R <sub>DSON</sub> of Q <sub>DH1</sub>            | R <sub>DS_QDH1</sub>        | V <sub>CFLY</sub> = 4V                                      |                                                                                                     |      | 12  |       | mΩ    |

| R <sub>DSON</sub> of Q <sub>CL1</sub>            | R <sub>DS_QCL1</sub>        | V <sub>VOUT</sub> = 4V                                      |                                                                                                     |      | 12  |       | mΩ    |

| R <sub>DSON</sub> of Q <sub>DL1</sub>            | R <sub>DS_QDL1</sub>        | V <sub>CFLY</sub> = 4V                                      |                                                                                                     |      | 12  |       | mΩ    |

| R <sub>DSON</sub> of Q <sub>CH2</sub>            | R <sub>DS_QCH2</sub>        | V <sub>PMID</sub> = 8V                                      |                                                                                                     |      | 20  |       | mΩ    |

| R <sub>DSON</sub> of Q <sub>DH2</sub>            | R <sub>DS_QDH2</sub>        | V <sub>CFLY</sub> = 4V                                      |                                                                                                     |      | 12  |       | mΩ    |

| R <sub>DSON</sub> of Q <sub>CL2</sub>            | R <sub>DS_QCL2</sub>        | V <sub>VOUT</sub> = 4V                                      |                                                                                                     |      | 12  |       | mΩ    |

| R <sub>DSON</sub> of Q <sub>DL2</sub>            | R <sub>DS_QDL2</sub>        | V <sub>CFLY</sub> = 4V                                      |                                                                                                     |      | 12  |       | mΩ    |

| Protection                                       |                             |                                                             |                                                                                                     |      |     |       |       |

| nINT Low Pulse Duration when a Protection Occurs | t <sub>INT</sub>            |                                                             |                                                                                                     |      | 256 |       | μs    |

| VBUS OVP Rising Threshold Range                  | Va:                         | Voltage divider mode                                        | I <sup>2</sup> C programmable, 50mV per step, 8.9V by default                                       | 7    |     | 12.25 | V     |

| VBOS OVP Rising Theshold Range                   | V <sub>BUS_OVP_R</sub>      | Bypass mode                                                 | I <sup>2</sup> C programmable, 25mV per step, 4.45V by default                                      | 3.5  |     | 6.5   | V     |

| VBUS OVP Accuracy                                | V <sub>BUS OVPR ACC</sub>   | $V_{BUS\_OVP\_R} = 4.45V$                                   |                                                                                                     | -2   |     | 2     | %     |

| VB03 CVI Accuracy                                | V BUS_OVPR_ACC              | $V_{BUS\_OVP\_R} = 9V$                                      |                                                                                                     | -1.1 |     | 1.1   | 70    |

| VBUS OVP Rising Deglitch Time                    | t <sub>VBUS_OVPR_DEG</sub>  | and triggering prot                                         |                                                                                                     |      | 1   |       | μs    |

| VBUS OVP Alarm Rising Threshold                  | V <sub>BUSOVP_ALM_R</sub>   | Voltage divider mode                                        | I <sup>2</sup> C programmable, 50mV per step, 8.7V by default                                       | 7    |     | 13.35 | V     |

| Range                                            | ▼ BUSOVP_ALM_R              | Bypass mode                                                 | I <sup>2</sup> C programmable, 25mV per step, 4.35V by default                                      | 3.5  |     | 6.675 | •     |

| VBUS OVP Alarm Hysteresis                        | V <sub>BUSOVP_ALM_HYS</sub> | $V_{BUSOVP\_ALM\_R} = 8V$                                   |                                                                                                     |      | 100 |       | mV    |

| VBUS OVP Alarm Accuracy                          | V <sub>BUSOVP</sub> ALM ACC | V <sub>BUSOVP_ALM_R</sub> = 4V                              |                                                                                                     | -3.2 |     | 3.7   | %     |

| VBGG GVT / Marrin / Modurady                     | V BUSOVP_ALM_ACC            | V <sub>BUSOVP_ALM_R</sub> = 8V                              |                                                                                                     | -2.9 |     | 3.5   | %     |

| IBUS OCP Threshold Range                         | I <sub>BUS_OCP</sub>        | I <sup>2</sup> C programmable default                       | e, 250mA per step, 4.25A by                                                                         | 1    |     | 6.5   | Α     |

| IBUS OCP Threshold Accuracy                      | I <sub>BUS_OCP_ACC</sub>    | I <sub>BUS_OCP</sub> = 3.0A                                 |                                                                                                     | -3.7 |     | 4     | %     |

| IBUS OCP Deglitch Time                           | t <sub>IBUS_OCP_DEG</sub>   | trigger protection a                                        |                                                                                                     |      | 80  |       | μs    |

| IBUS OCP Alarm Threshold Range                   | I <sub>BUSOCP_ALM_R</sub>   | I <sup>2</sup> C programmable default                       | e, 250mA per step, 3.5A by                                                                          | 1    |     | 8.75  | Α     |

| IBUS OCP Alarm Accuracy                          | I <sub>BUSOCP_ALM_ACC</sub> |                                                             | A, initial accuracy, T <sub>J</sub> = +25°C                                                         | -4.4 |     | 3.6   | %     |

|                                                  |                             | I <sub>BUS_UCP_R</sub> = 250mA, BUSUCP = 1                  |                                                                                                     |      | 250 |       |       |

| IBUS UCP Threshold                               | I <sub>BUS UCP</sub>        | I <sub>BUS_UCP_R</sub> = 500mA                              |                                                                                                     |      | 500 |       | mA    |

| inger cer minesheld                              | -BUS_UCP                    | I <sub>BUS_UCP_F</sub> = 125mA                              | A, BUSUCP = 1                                                                                       |      | 125 |       |       |

|                                                  |                             | I <sub>BUS_UCP_F</sub> = 250mA, BUSUCP = 0                  |                                                                                                     |      | 250 |       |       |

| IBUS UCP Deglitch time                           | t <sub>IBUS_UCP_DEG</sub>   | Deglitch between trigger protection 0.01ms by default.      | $I_{\text{BUS}}$ falling below $I_{\text{BUS}\_\text{UCP}}$ and action. $I^2\text{C}$ programmable, | 0.01 |     | 150   | ms    |

| VOUT OVP Rising Threshold Range                  | V <sub>OUT_OVP_R</sub>      | I <sup>2</sup> C programmable, 0.1V per step, 5V by default |                                                                                                     | 4.7  |     | 5     | V     |

| VOUT OVP Threshold Accuracy                      | V <sub>OUT_OVP_ACC</sub>    | V <sub>OUT_OVP_R</sub> = 5V                                 |                                                                                                     | 4.7  | 5   | 5.3   | V     |

| VOUT OVP Rising Deglitch Time                    | t <sub>VOUT_OVP_DEG</sub>   | Deglitch between and triggering prot                        | V <sub>VOUT</sub> rising above V <sub>OUT_OVP_R</sub> section action                                |      | 4   |       | μs    |

| VBAT OVP Rising Threshold Range                  | V <sub>BAT_OVP_R</sub>      |                                                             | 10mV per step, 4.4V by default                                                                      | 3.5  |     | 4.77  | V     |

| VBAT OVP Threshold Accuracy                      | V <sub>BAT_OVP_ACC</sub>    | $V_{BAT\_OVP\_R} = 4.4V$                                    |                                                                                                     | -0.9 |     | 0.9   | %     |

| PARAMETER                              | SYMBOL                      | CONDITIONS                                                                                                                            | MIN  | TYP    | MAX     | UNITS   |  |

|----------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------|--------|---------|---------|--|

| VBAT OVP Alarm Rising Threshold Range  | V <sub>BATOVP_ALM_R</sub>   | I <sup>2</sup> C programmable, 10mV per step, 4.2V by default                                                                         | 3.5  |        | 4.77    | ٧       |  |

| VBAT OVP Alarm Hysteresis              | V <sub>BATOVP_ALM_HYS</sub> |                                                                                                                                       |      | 40     |         | mV      |  |

| VBAT OVP Alarm Accuracy                | V <sub>BATOVP_ALM_ACC</sub> | $V_{BATOVP\_ALM\_R} = 4.4V$                                                                                                           | -1.2 |        | 1.2     | %       |  |

| IBAT OCP Threshold Range               | I <sub>BAT_OCP</sub>        | I <sup>2</sup> C programmable, 7.1A by default, 100mA per<br>step for 2A to 8.5A range, and 300mA per step for<br>8.5A to 11.2A range | 2    |        | 11.2    | Α       |  |

| IBAT OCP Threshold Accuracy            | I <sub>BAT_OCP_ACC</sub>    | $I_{BAT\_OCP} = 8A, R_{SNS} = 2m\Omega$                                                                                               | -2.3 |        | 2.3     | %       |  |

| IBAT OCP Deglitch Time                 | t <sub>IBAT_OCP_DEG</sub>   | Deglitch between I <sub>BAT</sub> rising above I <sub>BAT_OCP</sub> and triggering protection action                                  |      | 640    |         | μs      |  |

| IBAT OCP Alarm Rising Threshold Range  | I <sub>BATOCP_ALM_R</sub>   | $I^2C$ programmable, 100mA per step, 7A by default, $R_{SNS} = 2m\Omega$                                                              | 0    |        | 12.7    | Α       |  |

| IBAT OCP Alarm Threshold Accuracy      | I <sub>BATOCP_ALM_ACC</sub> | $I_{BATOCP\_ALM\_R} = 8A, R_{SNS} = 2m\Omega$                                                                                         | -3   |        | 2.7     | %       |  |

| IBAT UCP Alarm Threshold Range         | I <sub>BATUCP_ALM_F</sub>   | $I^2C$ programmable, 50mA per step, 2A default, $R_{SNS}$ = 2m $\Omega$                                                               | 0    |        | 4.5     | Α       |  |

| IBAT UCP Alarm Threshold Accuracy      | I <sub>BATUCP_ALM_ACC</sub> | $I_{BATUCP\_ALM\_F} = 4.5A, R_{SNS} = 2m\Omega$                                                                                       | -4.9 |        | 3.7     | %       |  |

| VBUS_HI Rising Threshold               | $V_{\text{BUS\_HI\_FALL}}$  | $V_{BUS}/(2 \times V_{VOUT})$ in voltage divider mode, $V_{BUS}/V_{VOUT}$ in bypass mode                                              |      | 1.175  |         |         |  |

| VBUS_HI Falling Threshold              | V <sub>BUS_HI_RISE</sub>    | V <sub>BUS</sub> /(2 × V <sub>VOUT</sub> ) in voltage divider mode,<br>V <sub>BUS</sub> /V <sub>VOUT</sub> in bypass mode             |      | 1.2    |         | \ / \ / |  |

| VBUS_LO Falling Threshold              | V <sub>BUS_LO_FALL</sub>    | V <sub>BUS</sub> /(2 × V <sub>VOUT</sub> ) in voltage divider mode,<br>V <sub>BUS</sub> /V <sub>VOUT</sub> in bypass mode             |      | 1      |         | V/V     |  |

| VBUS_LO Rising Threshold               | V <sub>BUS_LO_RISE</sub>    | V <sub>BUS</sub> /(2 × V <sub>VOUT</sub> ) in voltage divider mode,<br>V <sub>BUS</sub> /V <sub>VOUT</sub> in bypass mode             |      | 1.0125 |         |         |  |

| TSBUS Percentage Fault Threshold Range | TS <sub>BUS_FLT_F</sub>     | l <sup>2</sup> C programmable, 0.19531% per step, 4.10151% by default                                                                 | 0    |        | 49.8041 | %       |  |

| TSBUS Percentage Fault Accuracy        | TS <sub>BUSFLT_ACC</sub>    | TS <sub>BUS_FLT_F</sub> = 20.12%                                                                                                      | 19.4 | 20.12  | 20.8    | %       |  |

| TSBAT Percentage Fault Threshold Range | TS <sub>BAT_FLT_F</sub>     | l <sup>2</sup> C programmable, 0.19531% per step, 4.10151% by default                                                                 | 0    |        | 49.8041 | %       |  |

| TSBAT Percentage Fault Accuracy        | TS <sub>BATFLT_ACC</sub>    | TS <sub>BAT_FLT_F</sub> = 20.12%                                                                                                      | 19.4 | 20.12  | 20.8    | %       |  |

| TDIE OTP Rising Threshold Range        | $T_{\text{DIE\_OTP\_R}}$    | I <sup>2</sup> C programmable, 20°C per step, 140°C by default                                                                        | 80   |        | 140     | °C      |  |

| TDIE OTP Threshold Accuracy            | $T_{DIE\_OTP\_ACC}$         |                                                                                                                                       | -6   |        | 6       | °C      |  |

| TDIE OTP Threshold Hysteresis          | T <sub>DIE_OTP_HYS</sub>    |                                                                                                                                       |      | 30     |         | °C      |  |

| TDIE OTP Alarm Rising Threshold Range  | T <sub>DIEOTP_ALM_R</sub>   | l²C programmable, 0.5°C per step, 125°C by default                                                                                    | 25   |        | 150     | °C      |  |

| TDIE OTP Alarm Threshold Accuracy      | $T_{DIEOTP\_ALM\_ACC}$      |                                                                                                                                       | -6   |        | 6       | °C      |  |

| TDIE OTP Alarm Threshold Hysteresis    | T <sub>DIEOTP_ALM_HYS</sub> |                                                                                                                                       |      | 30     |         | °C      |  |

| ADC Specification                      |                             |                                                                                                                                       |      |        |         |         |  |

|                                        |                             | ADC_SAMPLE[1:0] = 00                                                                                                                  |      | 16     |         |         |  |

| ADC Conversion Time for Each           |                             | ADC_SAMPLE[1:0] = 01                                                                                                                  |      | 8      |         | 1       |  |

| Channel                                | t <sub>ADC_CONV</sub>       | ADC_SAMPLE[1:0] = 10                                                                                                                  |      | 4      |         | ms      |  |

|                                        |                             | ADC_SAMPLE[1:0] = 11                                                                                                                  |      | 2      |         | 1       |  |

|                                        |                             | ADC_SAMPLE[1:0] = 00                                                                                                                  |      | 15     |         |         |  |

| ADC Resolution                         | ADC                         | ADC_SAMPLE[1:0] = 01                                                                                                                  |      | 14     |         | - bit   |  |

|                                        | ADC <sub>RES</sub>          | ADC_SAMPLE[1:0] = 10                                                                                                                  |      | 13     |         |         |  |

|                                        |                             | ADC_SAMPLE[1:0] = 11                                                                                                                  |      | 11     |         | 1       |  |

| ADC IBUS Current Readable in           |                             | Effective Range                                                                                                                       | 0    |        | 7       | Α       |  |

| REG0x25 and REG0x26                    | I <sub>BUS_ADC</sub>        | LSB                                                                                                                                   |      | 1      |         | mA      |  |

| PARAMETER                                        | SYMBOL                    | CONDITIONS                                                                               | MIN  | TYP    | MAX   | UNITS |

|--------------------------------------------------|---------------------------|------------------------------------------------------------------------------------------|------|--------|-------|-------|

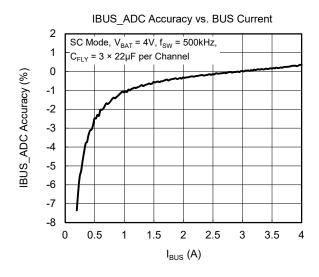

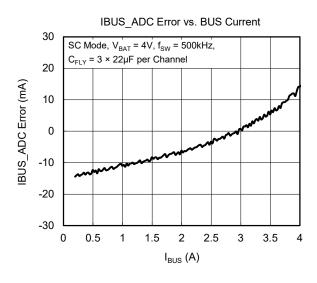

|                                                  |                           | I <sub>BUS</sub> = 2A, ADC_SAMPLE[1:0] = 00,                                             | -4   |        | 3.5   | %     |

| IBUS ADC Accuracy                                | I <sub>BUS_ADC_ACC</sub>  | initial accuracy, T <sub>J</sub> = +25°C                                                 |      |        | 0.0   | 70    |

| _ ,                                              |                           | I <sub>BUS</sub> = 3A, ADC_SAMPLE[1:0] = 00,<br>initial accuracy, T <sub>J</sub> = +25°C | -3.7 |        | 3.7   | %     |

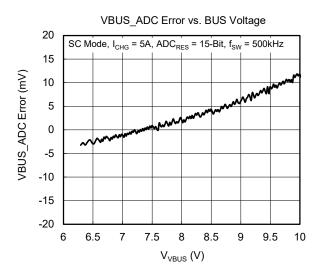

|                                                  |                           | Effective Range                                                                          | 0    |        | 16.39 | V     |

| ADC VBUS Voltage Readable in REG0x27 and REG0x28 | $V_{	t BUS\_ADC}$         |                                                                                          | U    | 4      | 10.39 |       |

| THE GOVE THIS THE GOVE                           |                           | LSB                                                                                      |      | 1      |       | mV    |

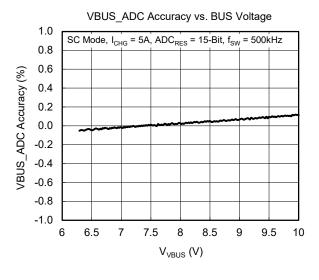

|                                                  |                           | $V_{VBUS} = 4V$ , ADC_SAMPLE[1:0] = 00, initial accuracy, $T_J = +25$ °C                 | -1   |        | 1     | %     |

| VBUS_ADC Accuracy                                | $V_{BUS\_ADC\_ACC}$       | $V_{VBUS} = 8V$ , ADC SAMPLE[1:0] = 00,                                                  |      |        |       |       |

|                                                  |                           | initial accuracy, T <sub>J</sub> = +25°C                                                 | -1   |        | 1     | %     |

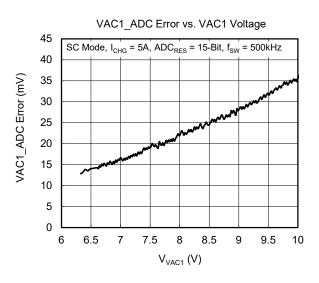

| ADC VAC1 Voltage Readable in                     |                           | Effective Range                                                                          | 0    |        | 14    | V     |

| REG0x29 and REG0x2A                              | $V_{AC1\_ADC}$            | LSB                                                                                      |      | 1      |       | mV    |

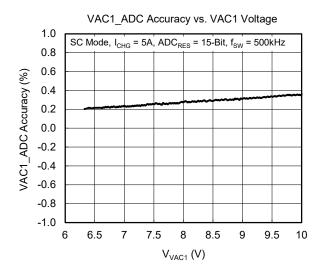

|                                                  |                           | V <sub>VAC1</sub> = 4V, ADC_SAMPLE[1:0] = 00,                                            |      |        |       |       |

| V/4.04_4.D0_4                                    |                           | initial accuracy, T <sub>J</sub> = +25°C                                                 | -1   |        | 1     | %     |

| VAC1_ADC Accuracy                                | V <sub>AC1_ADC_ACC</sub>  | V <sub>VAC1</sub> = 8V, ADC_SAMPLE[1:0] = 00,                                            | -1   |        | 1     | %     |

|                                                  |                           | initial accuracy, T <sub>J</sub> = +25°C                                                 | -1   |        | !     | 70    |

| ADC VAC2 Voltage Readable in                     | M                         | Effective Range                                                                          | 0    |        | 14    | V     |

| REG0x2B and REG0x2C                              | $V_{AC2\_ADC}$            | LSB                                                                                      |      | 1      |       | mV    |

|                                                  |                           | V <sub>VAC2</sub> = 4V, ADC_SAMPLE[1:0] = 00,                                            | 4    |        |       | 0/    |

| VAC2 ADC Accuracy                                | V                         | initial accuracy, T <sub>J</sub> = +25°C                                                 | -1   |        | 1     | %     |

| VAC2_ADC Accuracy                                | V <sub>AC2_ADC_ACC</sub>  | V <sub>VAC2</sub> = 8V, ADC_SAMPLE[1:0] = 00,                                            | -1   |        | 1     | %     |

|                                                  |                           | initial accuracy, T <sub>J</sub> = +25°C                                                 | -'   |        | '     | 70    |

| ADC VOUT Voltage Readable in                     | V <sub>OUT_ADC</sub>      | Effective Range                                                                          | 0    |        | 6     | V     |

| REG0x2D and REG0x2E                              |                           | LSB                                                                                      |      | 1      |       | mV    |

|                                                  |                           | $V_{VOUT} = 4V$ , ADC_SAMPLE[1:0] = 00,                                                  | -1   |        | 1     | %     |

| VOUT ADC Accuracy                                | V <sub>OUT ADC ACC</sub>  | initial accuracy, T <sub>J</sub> = +25°C                                                 | -1   |        | '     | 70    |

| V001_1D07100a1a0y                                | ▼OUT_ADC_ACC              | V <sub>VOUT</sub> = 4.4V, ADC_SAMPLE[1:0] = 00,                                          | -1   |        | 1     | %     |

|                                                  |                           | initial accuracy, T <sub>J</sub> = +25°C                                                 |      |        |       |       |

| ADC VBAT Voltage Readable in                     | $V_{BAT\_ADC}$            | Effective Range                                                                          | 0    |        | 6     | V     |

| REG0x2F and REG0x30                              | B/(1_7/20                 | LSB                                                                                      |      | 1      |       | mV    |

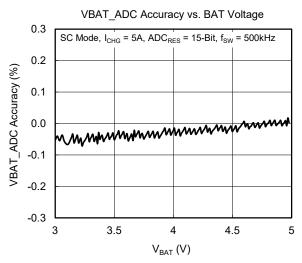

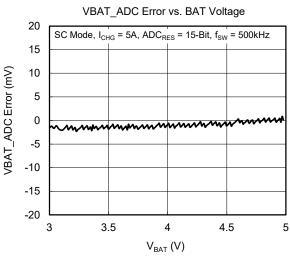

|                                                  |                           | $V_{BAT} = 4V$ , ADC_SAMPLE[1:0] = 00,                                                   | -0.3 |        | 0.3   | %     |

| VBAT_ADC Accuracy                                | V <sub>BAT_ADC_ACC</sub>  | initial accuracy, T <sub>J</sub> = +25°C                                                 |      |        |       |       |

|                                                  |                           | $V_{BAT}$ = 4.4V, ADC_SAMPLE[1:0] = 00, initial accuracy, $T_J$ = +25°C                  | -0.3 |        | 0.3   | %     |

|                                                  |                           |                                                                                          | 0    |        | 10    | ^     |

| ADC IBAT Current Readable in REG0x31 and REG0x32 | I <sub>BAT_ADC</sub>      | Effective Range                                                                          | 0    |        | 12    | Α .   |

| REGUXST AND REGUXSZ                              |                           | LSB                                                                                      |      | 1      |       | mA    |

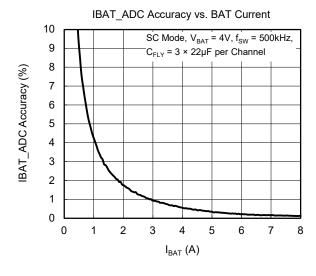

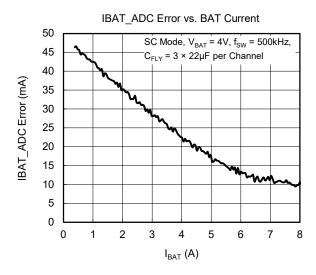

| IBAT ADC Accuracy                                | I <sub>BAT ADC ACC</sub>  | $I_{BAT} = 6A$ , $R_{SNS} = 2m\Omega$ , ADC_SAMPLE[1:0] = 00                             | -1.3 |        | 1.8   | %     |

| ,                                                | PBAT_ADC_ACC              | $I_{BAT} = 8A$ , $R_{SNS} = 2m\Omega$ , ADC_SAMPLE[1:0] = 00                             | -1.4 |        | 1.5   | %     |

| ADC TSBUS Pin Percentage                         | TO                        | Effective Range                                                                          | 0    |        | 50    | %     |

| Readable in REG0x33 and REG0x34                  | TS <sub>BUS_ADC</sub>     | LSB                                                                                      |      | 0.0977 |       | %     |

| TSBUS_ADC Accuracy                               | TS <sub>BUS_ADC_ACC</sub> | TSBUS = 20% of V <sub>REGN</sub> , ADC_SAMPLE[1:0] = 00                                  | 18.6 | 20     | 20.9  | %     |

| ADC TSBAT Pin Percentage                         |                           | Effective Range                                                                          | 0    |        | 50    | %     |

| Readable in REG0x35 and REG0x36                  | TS <sub>BAT_ADC</sub>     | LSB                                                                                      |      | 0.0977 |       | %     |

| TSBAT_ADC Accuracy                               | TS <sub>BAT_ADC_ACC</sub> | TSBAT = 20% of V <sub>REGN</sub> , ADC_SAMPLE[1:0] = 00                                  | 18.6 | 20     | 20.9  | %     |

| ADC DIE Temperature Readable in                  | <b>-</b>                  | Effective Range                                                                          | -40  |        | 150   | °C    |

| REG0x37 and REG0x38                              | $T_{DIE\_ADC}$            | LSB                                                                                      |      | 0.5    |       | °C    |

| PARAMETER                                          | SYMBOL                                      | CONDITIONS        | MIN   | TYP | MAX  | UNITS |  |

|----------------------------------------------------|---------------------------------------------|-------------------|-------|-----|------|-------|--|

| I <sup>2</sup> C Interface (SCL and SDA Pins)      | <sup>2</sup> C Interface (SCL and SDA Pins) |                   |       |     |      |       |  |

| High Level Input Voltage                           | V <sub>IH_I2C</sub>                         | SCL and SDA pins  | 0.825 |     |      | V     |  |

| Low Level Input Voltage                            | $V_{IL\_I2C}$                               | SCL and SDA pins  |       |     | 0.4  | V     |  |

| Low Level Output Voltage                           | $V_{OL\_SDA}$                               | Sink 5mA, SDA pin |       |     | 0.4  | V     |  |

| High-Level Leakage Current                         | I <sub>LKG_I2C</sub>                        | Connected to 1.2V |       |     | 1    | μΑ    |  |

| SCL Clock Frequency                                | f <sub>CLK</sub>                            |                   |       |     | 1000 | kHz   |  |

| Logic Output Pin (nINT, TSBAT_SYN                  | NCOUT)                                      |                   |       |     |      |       |  |

| Low Level Output Voltage, nINT Pin                 | V <sub>OL_INT</sub>                         | Sink 5mA          |       |     | 0.4  | V     |  |

| High-Level Leakage Current, nINT Pin               | I <sub>LKG_nINT</sub>                       | Connected to 1.2V |       |     | 1    | μA    |  |

| Low Level Output Voltage, TSBAT_<br>SYNCOUT Pin    | V <sub>OL_TSBAT_SYNCOUT</sub>               | Sink 5mA          |       |     | 0.4  | V     |  |

| High-Level Leakage Current, TSBAT_<br>SYNCOUT Pin  | I <sub>LKG_TSBAT_SYNCOUT</sub>              | Connected to 1.2V |       |     | 1    | μΑ    |  |

| Logic Input Pin (SRN_SYNCIN)                       |                                             |                   |       |     |      |       |  |

| High Level Input Voltage,<br>SRN_SYNCIN Pin        | V <sub>IH_SRN_SYNCIN</sub>                  |                   | 0.825 |     |      | V     |  |

| Low Level Input Voltage,<br>SRN_SYNCIN Pin         | V <sub>IL_SRN_SYNCIN</sub>                  |                   |       |     | 0.4  | V     |  |

| High-Level Leakage Current, SRN_SYNCIN Pin         | I <sub>LKG_SRN_SYNCIN</sub>                 | Connected to 1.8V |       |     | 1    | μΑ    |  |

| Timing Requirement                                 | Timing Requirement                          |                   |       |     |      |       |  |

| Time between Consecutive Faults for ALM Indication | t <sub>ALM_DEBOUNCE</sub>                   |                   |       | 120 |      | ms    |  |

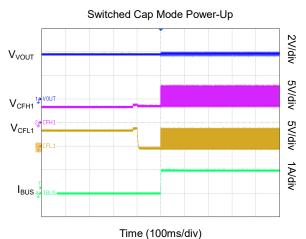

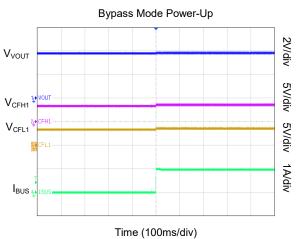

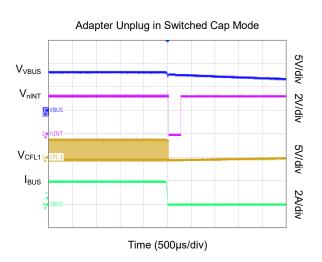

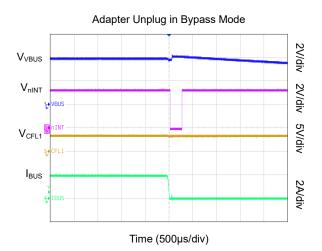

### TYPICAL PERFORMANCE CHARACTERISTICS

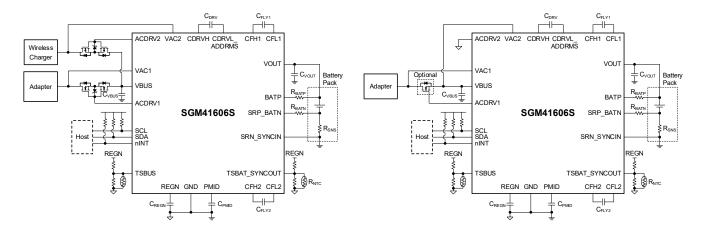

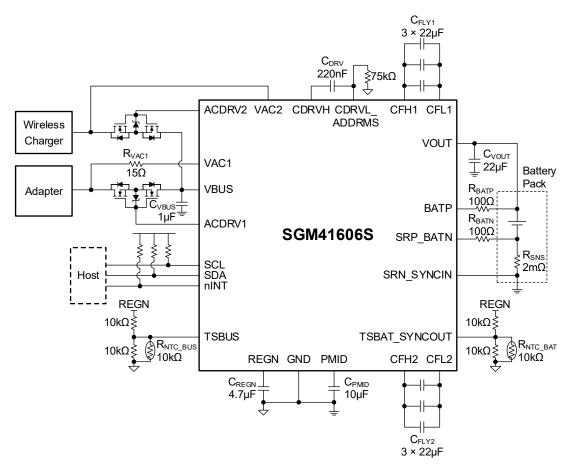

### TYPICAL APPLICATION CIRCUITS

Figure 1. Typical Application Circuit with Dual Input

Figure 2. Typical Application Circuit with Single Input

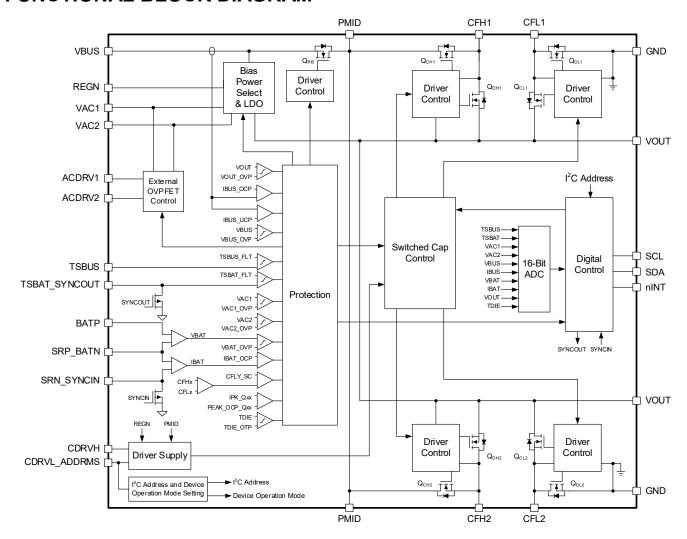

### **FUNCTIONAL BLOCK DIAGRAM**

Figure 3. Functional Block Diagram

### **DETAILED DESCRIPTION**

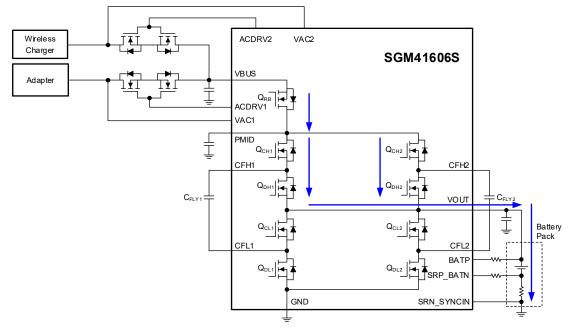

The SGM41606S is an efficient 8A switched-capacitor battery charging device with  $I^2C$  control that can operate either in charge-pump voltage divider mode or in bypass mode. It can charge 1-cell Li-lon or Li-polymer battery in a wide 3.6V to 12V input voltage range (VBUS) from smart wall adapters or wireless charger. The switched-capacitor architecture is optimized for 50% duty cycle to cut the input current to one-half of the battery current and reduce the wiring drops, losses and temperature rise in the application.

A two-channel switched-capacitor topology is used to reduce the required input capacitors, improve efficiency and minimize the output ripple. It supports dual input configuration through integrated MUX control and driver for external OVPFETs. It also allows single input with no external OVPFET or single OVPFET. Moreover, it supports two devices in parallel for higher power systems.

A high speed 16-bit ADC converter is also included to provide bus voltage, bus current, battery voltage, battery current, battery and cable connector temperature, and die temperature information for the charge management host via  $I^2C$  serial interface.

### **Charge-Pump Voltage Divider Mode**

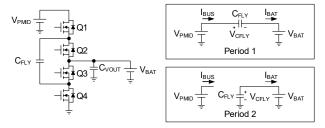

The charge-pump voltage divider mode operates with a fixed 50% duty cycle. Taking one of the two channels in the switched-capacitor as an example, the basic principle of operation is shown in Figure 4. In period 1, Q1 and Q3 are tuned on and  $V_{\text{PMID}}$  charges the  $C_{\text{FLY}}$  and the battery (in series) such that:

$$V_{CFLY} = V_{PMID} - V_{BAT}$$

(1)

In period 2, Q2 and Q4 are turned on and  $C_{\text{FLY}}$  appears in parallel with the battery:

$$V_{CFLY} = V_{BAT}$$

(2)

Ignoring the small fluctuation of the capacitor and battery voltages in period 1 and 2 in steady state operation, Equation 1 and 2 can be combined to calculate capacitor voltage:

$$V_{CFLY} = V_{BAT} = V_{PMID}/2$$

(3)

Ignoring small energy loss in each switching period, the input and output cycle-average powers are equal. Therefore,

$$V_{PMID} \times I_{BUS} = V_{BAT} \times I_{BAT}$$

(4)

or

$$I_{BUS} = I_{BAT}/2 \tag{5}$$

Figure 4. Voltage Divider Charger Operating Principle

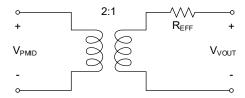

Assuming no charge leakage path and considering  $R_{\text{EFF}}$  as the effective input to output resistance (due to the switch on-resistances and  $C_{\text{FLY}}$  losses), the divider can be modeled as shown in Figure 5. Using this model, the output voltage is half of the input voltage under no load conditions as explained before. The SGM41606S has two channels of such architecture operating at  $f_{\text{SW}}$  frequency with 180° phase difference. Each channel provides  $I_{\text{VOUT}}/2$  at the VOUT node, so:

$$V_{VOUT} = \frac{1}{2}V_{PMID} - \frac{1}{2}R_{EFF} \times I_{VOUT}$$

(6)

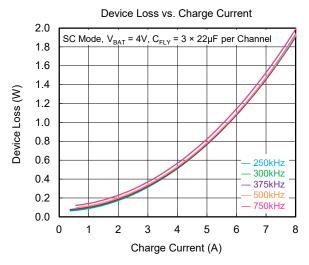

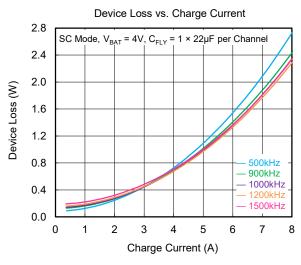

At low switching frequencies the capacitor charge sharing losses are dominant and  $R_{EFF}\approx 1/(4f_{SW}C_{FLY}).$  As frequency increases,  $R_{EFF}$  finally approaches ( $R_{DS\_QCH}$  +  $R_{DS\_QDL}$ +  $R_{DS\_QDL}$ )/2.

Figure 5. Model of Voltage Divider

The two-channel interleaved operation ensures a smooth input current and simplifies the noise filtering. The VOUT ripple can be estimated by first order approximation of  $C_{\text{FLY}}$  voltage drop due to the discharge in the half period, plus the discharge drop during the short dead time.

Selecting high quality  $C_{\text{FLY}}$  capacitors and proper switching frequency are the key factors for a well performing capacitor voltage divider. Switching frequency selection is a trade-off between efficiency and capacitor size. Lower frequency increases efficiency by reducing switching losses but requires larger capacitance to maintain low output ripple and low output impedance ( $R_{\text{EFF}}$ ). An optimum switching frequency can be found for any selected  $C_{\text{FLY}}$  capacitor to minimize losses.

### **Bypass Mode**

The SGM41606S is designed to operate in bypass mode when  $V_{VBUS}$  is close to the  $V_{VOUT}$ . When such valid voltage is present on VBUS, the device can enable bypass mode by setting EN\_BYPASS = 1 and all switches between VBUS and VOUT are fully turned on while the other switches are kept off. When  $V_{VBUS}$  is near  $V_{VOUT}$ , the bypass mode offers the best efficiency and the device is capable of sourcing up to 5A. The bypass mode switched-capacitor charger is showed in Figure 6.

The output voltage is close to the  $V_{VBUS}$  minus a voltage drop caused by the on-resistances of the RBFET plus the two high-side switches of the two channels in parallel:

$$R_{EFF}$$

(Bypass mode)  $\approx R_{DS\_QRB} + (R_{DS\_QCH1} + R_{DS\_QDH1}) \parallel (R_{DS\_QCH2} + R_{DS\_QDH2})$  (7)

where  $R_{DS}$  QXX is the on-resistance of the switch QXX.

### **Charging System**

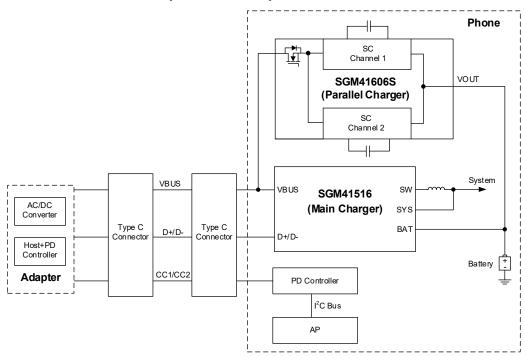

The SGM41606S is a slave charger device and needs a host. The host must set up all protection functions and disable the main charger before enabling the SGM41606S. The host must monitor the nINT interrupts especially during high current charging. It must also communicate with the wall adapter to control the charge current.

Figure 7 shows the block diagram of a charge system using the SGM41606S along with other devices. In this system, the PD controller is used to communicate with adapter by PD protocol. When the smart wall adapter is inserted, the AP unit controls the switching charger (SGM41516) that powers the load system and the switched capacitor charger (SGM41606S) that provides high current charging. The communication between those devices is through I<sup>2</sup>C interface.

Figure 6. SGM41606S Bypass Mode

Figure 7. SGM41606S Charging System Diagram

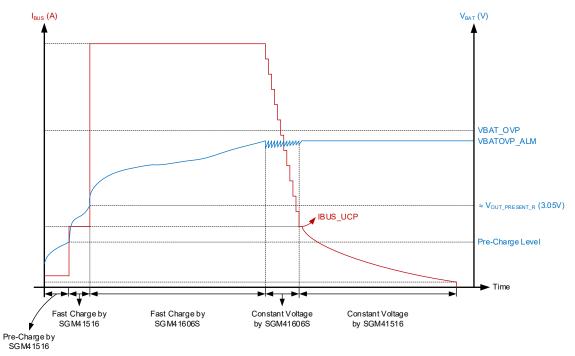

Figure 8. SGM41606S System Charging Profile

A typical charge profile for a high-capacity battery using switching charger and switched capacitor charger together is shown in Figure 8. During the trickle charge and pre-charge, the charging is controlled by the switching charger. Once the battery voltage reaches  $V_{\text{OUT\_PRESENT\_R}}$  (3.05V, TYP), the adapter can negotiate for a higher bus voltage and enable the SGM41606S for charging (bypass or voltage divider mode). Once the battery voltage approaches the  $V_{\text{BATOVP\_ALM}}$  point, the SGM41606S will notify the AP to reduce the IBUS current, and the AP will negotiate with adapter for a lower bus voltage to effectively taper the current until a point where the IBUS current ramps down below  $I_{\text{BUS}}$  UCP.

### **Startup Sequence**

The SGM41606S is powered from the greater of VAC1, VAC2, VBUS or VOUT (VAC1 and VAC2 are used as sense inputs for adapter voltages as well). When  $V_{\text{VOUT}}$  rises above  $V_{\text{OUT}\_\text{UVLO}\_\text{R}}$ , or  $V_{\text{VAC1}}$ ,  $V_{\text{VAC2}}$  or  $V_{\text{VBUS}}$  rises above their respective UVLO rising threshold, the  $I^2C$  interface is ready for communication and all the registers are reset to default values.

The device does not start charging after power-up, because by default the charger is disabled but the ADC can be enabled and the AP can read the system parameters before enabling charge. The charge can be enabled only if  $V_{VBUS} > V_{BUS\_PRESENT\_R}$  and  $V_{VOUT} > V_{OUT\_PRESENT\_R}$ .

# **Device Power-Up from Battery without Input Source**

To reduce the quiescent current and maximize the battery run time when it is the only available source, the REGN LDO and most of the sensing circuits are turned off, except VAC1\_PRESENT, VAC2\_PRESENT, BUS\_PRESENT and VOUT PRESENT functions.

#### **Device Power-Up from Input Source**

When an input source is plugged-in and the conditions of  $V_{VBUS} > V_{BUS\_PRESENT\_R}$  and  $V_{VOUT} > V_{OUT\_PRESENT\_R}$  are valid, the AP must initialize all protections to the desired thresholds before enabling charge. The protection thresholds that need

to be set are VAC1\_OVP, VAC2\_OVP, VBUS\_OVP, IBUS\_OCP, IBUS\_UCP, VOUT\_OVP, VBAT\_OVP, IBAT\_OCP, TSBUS\_FLT, TSBAT\_FLT and TDIE\_OTP. If one of the protection trigger conditions is met, the charger stops switching. It will also be turned off the corresponding external OVPFETs when VAC1\_OVP or VAC2\_OVP or VBUS\_SCP event occurs.

After setting protections, the VBUS voltage is checked to be between VBUS\_ERRLO and VBUS\_ERRHI to allow forward charge mode operation. When the AP configures bypass or voltage divider mode by setting EN\_BYPASS = 1 or 0 and then set CHG\_EN = 1, charging is enabled and current flows into the battery, and CONV\_ACTIVE\_STAT bit is set to 1 to indicate charging is active. Then raising the VBUS voltage will increase the battery charge current. When the converter is on, any command to change the charge mode is ignored. To do so, the charging must be disabled first, and then the charge mode can be changed by I<sup>2</sup>C serial interface.

#### **Device HIZ State**

The HIZ mode is activated when the AP sets EN\_HIZ bit from 0 to 1. When the SGM41606S enters HIZ mode, the charging stops, ADC conversion discontinues, ACDRV and REGN LDO are turned off regardless of the presence of the adapter or absence of any fault conditions. To exit HIZ mode, the AP should set EN HIZ to 0, or the device POR occurs.

#### **REGN Management**

REGN provides the power required for the analog section. When  $V_{VBUS}$  rises above  $V_{BUS\_PRESENT\_R}$ , REGN is powered up and ramps up to 5V (TYP). A 4.7 $\mu$ F or larger capacitor is required on the REGN pin.

When the faults, including VBUS\_OVP, VBAT\_OVP, VOUT\_OVP, IBUS\_OCP, IBAT\_OCP, IBUS\_UCP, VBUS\_SCP, VAC1\_OVP, VAC2\_OVP, TSBUS\_FLT, TSBAT\_FLT and TDIE\_OTP, are triggered, the converter switching stops and CHG\_EN bit is reset to 0, but the REGN LDO remains powered up. Refer to the device protection section for more details.

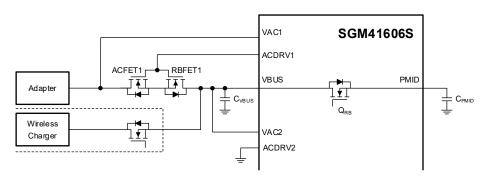

### **Dual Input Power Path Management**

The SGM41606S features two ACDRV pins to drive two sets of back-to-back N-channel MOSFETs, which select and manage the input power from two different input sources (such as wired and wireless input sources). Each set of back-to-back N-channel FETs consists of an input N-channel MOSFET (ACFET) and a reverse-blocking N-channel MOSFET (RBFET). During POR procedure, the internal bias circuit detects whether the ACDRVx pin is shorted to GND to sense whether the ACFET-RBFET are connected, and then updates the ACRB1\_CONFIG\_STAT and ACRB2\_CONFIG\_ STAT bits to indicate the connection status of ACFET-RBFET. If the external back-to-back N-channel FETs are not populated in the schematic, then tie corresponding VAC pin to VBUS and short ACDRVx to GND. The device supports 4 input configurations: single input without any external FET, single input with only one ACFET, dual input with one set of ACFET-RBFET, and dual input with two ACFET-RBFET. Detailed descriptions of the power-up sequences for different applications are provided below.

#### **ACDRV Turn-on Condition**

For most of the 4 configurations, the ACDRV controls the input power path for both SGM41606S and main charger. When one or both input power sources are plugged in (not in OTG mode), the ACDRV can be turned on when all of the following conditions are met:

- 1. The corresponding ACFET-RBFET is populated: VAC is connected to the input power and ACDRV is not short to GND.

- 2.  $V_{\text{VAC}}$  exceeds  $V_{\text{AC\_PRESENT\_R}}$  and not higher than  $V_{\text{AC\_OVP}}$  thresholds.

- 3. DIS\_ACDRV\_BOTH is not set to 1.

- 4. Not in HIZ mode: EN HIZ is not set to 1.

- 5. V<sub>VBUS</sub> is below V<sub>BUS</sub> PRESENT F threshold.

### **Single Input without ACFET-RBFET**

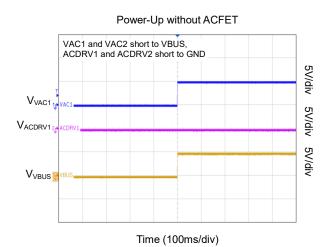

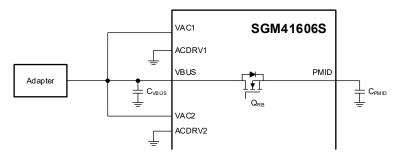

In this configuration, the SGM41606S is not responsible for controlling the external OVPFET. VAC1 and VAC2 are both connected to VBUS directly, while ACDRV1 and ACDRV2 are both shorted to GND. The following table summarizes the related pin connections and the control function of relevant registers, as well as the status bits.

Table 1. Single Input without External OVPFET

| Input Configuration        | Single Input                    |

|----------------------------|---------------------------------|

| External FET Connection    | No external FET                 |

| Input Sense Pin Connection | VAC1 and VAC2 tied to VBUS      |

| ACDRV Pin Connection       | ACDRV1 and ACDRV2 short to GND  |

| ACDRV1_STAT                | 0                               |

| ACDRV2_STAT                | 0                               |

| DIS_ACDRV_BOTH             | 1                               |

| ACRB1_CONFIG_STAT          | 0 = ACFET1-RBFET1 is not placed |

| ACRB2_CONFIG_STAT          | 0 = ACFET2-RBFET2 is not placed |

| EN HIZ                     | No impact on ACDRV              |

Figure 9. Single Input without ACFET-RBFET

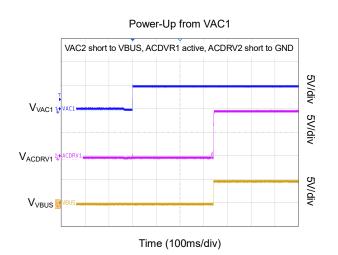

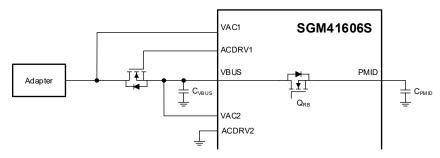

### **Single Input with ACFET1**

In this configuration, only one input N-channel MOSFET for VAC1 (ACFET1) is placed. RBFET1 and ACFET2-RBFET2 are not used. VAC1 and ACDRV1 are connected to the drain and the gate of ACFET1, respectively. VAC2 is tied to VBUS,

and ACDRV2 is shorted to GND. This structure supports single input from VAC1. The following table summarizes the related pin connections and the control function of relevant registers, as well as the status bits.

Table 2. Single Input with Single OVPFET

| Input Configuration        | Single Input                                                                                                                      |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| External FET Connection    | Only ACFET1, no RBFET1 and ACFET2-RBFET2                                                                                          |

| Input Sense Pin Connection | VAC1 tied to the input source, VAC2 short to VBUS                                                                                 |

| ACDRV Pin Connection       | ACDRV1 tied to the gate of ACFET1, ACDRV2 short to GND                                                                            |