# Microprocessor Supervisory Circuit with Watchdog Timer and Manual Reset

#### GENERAL DESCRIPTION

The SGM823S is a complete microprocessor supervisory device which combines reset, watchdog and manual reset functions in a SOT-23-5 package. System reliability is significantly improved by such integration compared to the designs with individual ICs or discrete components. The SGM823S also features an excellent transient immunity to ignore fast  $V_{\rm CC}$  transients.

This device has an active-low push-pull reset output (nRESET) that is activated by a logic low on the manual reset input (nMR), a watchdog expiry event or due to a low  $V_{CC}$  voltage. The nRESET output can still be in the correct logic state even if  $V_{CC}$  is 1V. The SGM823S is offered in four fixed  $V_{CC}$  reset threshold voltages.

The SGM823S is available in a Green SOT-23-5 package. It operates over a junction temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C.

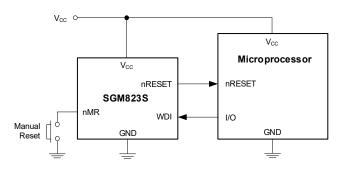

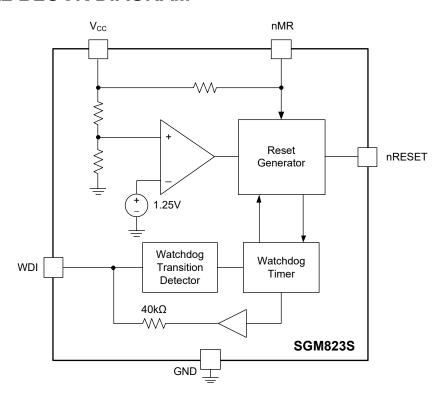

#### TYPICAL APPLICATION

**Figure 1. Typical Application Circuit Example**

#### **FEATURES**

Ultra-Low Supply Current: 0.8µA (TYP)

SGM823S

- Precision Supply-Voltage Monitor

- 4.63V for SGM823S-L

- 3.08V for SGM823S-T

- + 2.93V for SGM823S-S

- 2.63V for SGM823S-R

- Guaranteed nRESET Valid at V<sub>CC</sub> = 1V

- Push-Pull nRESET Output

- Reset Pulse Width: 260ms (TYP)

- Debounced TTL/CMOS-Compatible

- Manual Reset Input

- Watchdog Timer with 2s (TYP) Timeout

- Fully Specified over Temperature

- Power-Supply Transient Immunity

- Without External Components

- -40°C to +125°C Operating Temperature Range

- Available in a Green SOT-23-5 Package

#### **APPLICATIONS**

Computers

Portable Equipment

Automotive Equipment

Intelligent Instruments

Critical µP Power Monitoring

#### PACKAGE/ORDERING INFORMATION

| MODEL     | RESET<br>THRESHOLD<br>(V) | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | MPERATURE ORDERING I |       | PACKING<br>OPTION   |

|-----------|---------------------------|------------------------|-----------------------------------|----------------------|-------|---------------------|

| SGM823S-L | 4.63                      | SOT-23-5               | -40°C to +125°C                   | SGM823S-LXN5G/TR     | 0DRXX | Tape and Reel, 3000 |

| SGM823S-T | 3.08                      | SOT-23-5               | -40°C to +125°C                   | SGM823S-TXN5G/TR     | 0DSXX | Tape and Reel, 3000 |

| SGM823S-S | 2.93                      | SOT-23-5               | -40°C to +125°C                   | SGM823S-SXN5G/TR     | 0DTXX | Tape and Reel, 3000 |

| SGM823S-R | 2.63                      | SOT-23-5               | -40°C to +125°C                   | SGM823S-RXN5G/TR     | 0AKXX | Tape and Reel, 3000 |

#### MARKING INFORMATION

NOTE: XX = Date Code.

YYY X X

Date Code - Week

Date Code - Year

Serial Number

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### ABSOLUTE MAXIMUM RATINGS

| Terminal Voltage (with Respect to GND | ))                             |

|---------------------------------------|--------------------------------|

| V <sub>CC</sub>                       | 0.3V to 6.0V                   |

| All Other Inputs                      | 0.3V to V <sub>CC</sub> + 0.3V |

| Input Current                         |                                |

| V <sub>CC</sub>                       | 32mA                           |

| GND                                   | 32mA                           |

| Output Current                        |                                |

| All Outputs                           | 32mA                           |

| Package Thermal Resistance            |                                |

| SOT-23-5, θ <sub>JA</sub>             | 208°C/W                        |

| SOT-23-5, θ <sub>JB</sub>             | 56.6°C/W                       |

| SOT-23-5, θ <sub>JC</sub>             | 106.1°C/W                      |

| Junction Temperature                  | +150°C                         |

| Storage Temperature Range             | 65°C to +150°C                 |

| Lead Temperature (Soldering, 10s)     | +260°C                         |

| ESD Susceptibility                    |                                |

| HBM                                   | 4000V                          |

| CDM                                   | 1000V                          |

#### RECOMMENDED OPERATING CONDITIONS

Operating Junction Temperature Range ......-40°C to +125°C

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

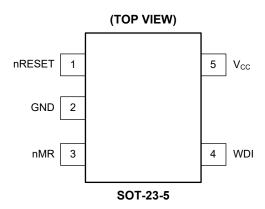

# **PIN CONFIGURATION**

# **PIN DESCRIPTION**

| PIN | NAME   | I/O | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | nRESET | 0   | Active-Low Reset Output Pin. It delivers a 260ms (TYP) low pulse when activated. nRESET remains low if $V_{CC}$ is below the reset threshold or nMR is logic low. It remains low for 260ms after any of the following events: $V_{CC}$ rises above the reset threshold, a watchdog expiry triggers a reset, or the nMR input goes from low to high.                                                                           |

| 2   | GND    | -   | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3   | nMR    | I   | Manual Reset Input Pin. nRESET keeps low when nMR is low. When nMR is high, nRESET becomes high after a 260ms timeout period. It is an active-low reset input with an internal $60k\Omega$ pull-up resistor. nMR can be driven by a CMOS/TTL logic or by a switch shorting to GND. If not used, leave it open or connect it to $V_{CC}$ .                                                                                     |

| 4   | WDI    | ı   | Watchdog Input Pin. If the high or low state of WDI exceeds the watchdog timeout period, the internal watchdog timer is expired and a reset is triggered. The internal watchdog timer is clear while a reset is asserted. The timer is also cleared if the WDI input is changed (on rising or falling edges). The watchdog feature is disabled if the WDI is left open or if it is connected to a three-stated buffer output. |

| 5   | Vcc    | 1   | Supply Voltage Pin.                                                                                                                                                                                                                                                                                                                                                                                                           |

NOTE: I: input; O: output.

### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 4.775V \text{ to } 5.5V \text{ for SGM823S-L}, V_{CC} = 3.175V \text{ to } 5.5V \text{ for SGM823S-T}, V_{CC} = 3.020V \text{ to } 5.5V \text{ for SGM823S-S}, V_{CC} = 2.710V \text{ to } 5.5V \text{ for SGM823S-R}, T_J = -40^{\circ}\text{C}$  to +125°C, typical values are measured at  $T_J = +25^{\circ}\text{C}$ , unless otherwise noted.)

| PARAMETER                                         | SYMBOL              | CONDITIONS                                                               |                                                | MIN                   | TYP  | MAX   | UNITS        |

|---------------------------------------------------|---------------------|--------------------------------------------------------------------------|------------------------------------------------|-----------------------|------|-------|--------------|

| Operating Voltage Range                           | V <sub>CC</sub>     |                                                                          |                                                | 1                     |      | 5.5   | V            |

| Summittee Commont                                 |                     | V <sub>CC</sub> = 3.6V                                                   |                                                |                       | 0.8  | 1.84  |              |

| Supply Current                                    | I <sub>SUPPLY</sub> | V <sub>CC</sub> = 5.5V                                                   |                                                |                       | 0.95 | 2.12  | μΑ           |

| Reset                                             |                     |                                                                          |                                                | •                     |      | •     | •            |

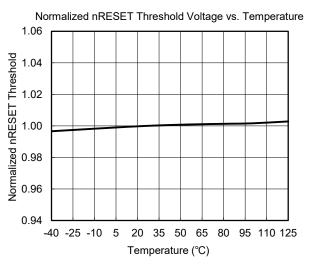

|                                                   |                     | SGM823S-L                                                                | T <sub>J</sub> = +25°C                         | 4.505                 | 4.63 | 4.755 |              |

|                                                   |                     |                                                                          | $T_J = -40^{\circ}C \text{ to } +125^{\circ}C$ | 4.465                 |      | 4.775 |              |

|                                                   |                     | CCM022C T                                                                | T <sub>J</sub> = +25°C                         | 2.995                 | 3.08 | 3.165 |              |

|                                                   | V                   | SGM823S-T                                                                | $T_J = -40^{\circ}C \text{ to } +125^{\circ}C$ | 2.955                 |      | 3.175 | .,           |

| nRESET Threshold                                  | $V_{nRST}$          | 0.0140000.0                                                              | T <sub>J</sub> = +25°C                         | 2.855                 | 2.93 | 3.005 | V            |

|                                                   |                     | SGM823S-S                                                                | $T_J = -40^{\circ}C \text{ to } +125^{\circ}C$ | 2.830                 |      | 3.020 |              |

|                                                   |                     | 0.0140000 B                                                              | T <sub>J</sub> = +25°C                         | 2.560                 | 2.63 | 2.700 | 1            |

|                                                   |                     | SGM823S-R                                                                | $T_J = -40^{\circ}C \text{ to } +125^{\circ}C$ | 2.540                 |      | 2.710 |              |

|                                                   |                     | SGM823S-L                                                                |                                                |                       | 22   |       |              |

| DECETT! I III I                                   | .,                  | SGM823S-T                                                                |                                                |                       | 15   |       | <del>-</del> |

| nRESET Threshold Hysteresis                       | V <sub>HYS</sub>    | SGM823S-S                                                                |                                                |                       | 14   |       | - mV<br>-    |

|                                                   |                     | SGM823S-R                                                                |                                                | 12                    |      |       |              |

| nRESET Pulse Width                                | t <sub>RP</sub>     |                                                                          |                                                | 140                   | 260  | 400   | ms           |

|                                                   | V <sub>OH</sub>     | V <sub>CC</sub> ≥ 3.15V, I <sub>SOURCE</sub> = 500µA, reset not asserted |                                                | 0.7 × V <sub>CC</sub> |      |       | V            |

| nRESET High-Level Output Voltage                  |                     | V <sub>CC</sub> ≥ 4.75V, I <sub>SOU</sub>                                | 0.7 × V <sub>CC</sub>                          |                       |      |       |              |

|                                                   | V <sub>OL</sub>     | V <sub>CC</sub> ≥ 1.0V, I <sub>SINK</sub>                                |                                                |                       | 0.3  |       |              |

| DECET Land Out of Valteria                        |                     | V <sub>CC</sub> ≥ 1.2V, I <sub>SINK</sub>                                |                                                |                       | 0.3  | - V   |              |

| nRESET Low-Level Output Voltage                   |                     | V <sub>CC</sub> ≥ 2.55V, I <sub>SIN</sub>                                |                                                |                       | 0.3  |       |              |

|                                                   |                     | V <sub>CC</sub> ≥ 4.25V, I <sub>SIN</sub>                                |                                                |                       | 0.4  |       |              |

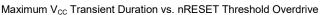

| V <sub>CC</sub> to Reset Delay                    | t <sub>RD</sub>     | $V_{nRST} - V_{CC} = 500 \text{mV}, T_{J} = +25^{\circ}\text{C}$         |                                                |                       | 12   |       | μs           |

| Watchdog                                          |                     | 1                                                                        |                                                | l .                   |      | l     |              |

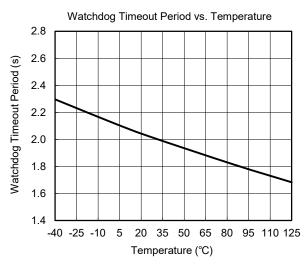

| Watchdog Timeout Period                           | t <sub>WD</sub>     |                                                                          |                                                | 1.10                  | 2    | 3.46  | s            |

| WDI Pulse Width                                   | t <sub>WP</sub>     | $V_{IL} = 0V$ , $V_{IH} = V_0$                                           | cc                                             | 90                    |      |       | ns           |

| WDI Low-Level Input Voltage                       | $V_{IL_{WDI}}$      | $V_{nRST\_MAX} < V_{CC}$                                                 | < 5V                                           |                       |      | 0.8   | V            |

| WDI High-Level Input Voltage                      | V <sub>IH_WDI</sub> | V <sub>nRST_MAX</sub> < V <sub>CC</sub>                                  | < 5V                                           | 0.7 × V <sub>CC</sub> |      |       | V            |

|                                                   |                     | WDI = V <sub>CC</sub>                                                    |                                                |                       | 0.01 | 0.5   |              |

| WDI Input Current WDI = 0V                        |                     |                                                                          | -0.5                                           | -0.01                 |      | μA    |              |

| Manuel Reset                                      |                     | 1                                                                        |                                                |                       |      | I.    |              |

| nMR Low-Level Input Voltage                       | $V_{IL\_nMR}$       |                                                                          |                                                |                       |      | 0.8   | V            |

| nMR High-Level Input Voltage                      | V <sub>IH_nMR</sub> |                                                                          |                                                | 2                     |      |       | V            |

| nMR Pulse Width                                   | t <sub>MR</sub>     |                                                                          |                                                | 320                   |      |       | ns           |

| nMR Noise Immunity<br>(Pulse Width with No Reset) |                     |                                                                          |                                                |                       | 190  |       | ns           |

| •                                                 | t <sub>MD</sub>     |                                                                          |                                                |                       |      | 470   | ns           |

| nMR to nRESET Out Delay                           | MID                 |                                                                          |                                                |                       |      |       |              |

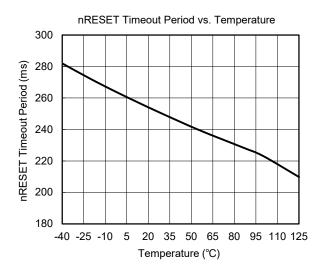

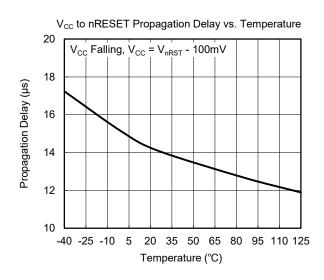

### TYPICAL PERFORMANCE CHARACTERISTICS

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. Block Diagram

### **DETAILED DESCRIPTION**

#### nRESET Output

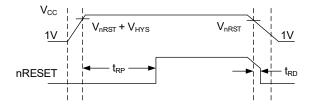

The reset input of a microprocessor ( $\mu P$ ) initiates it to a known state. The SGM823S supervisory circuit asserts a reset to the supervised  $\mu P$  to prevent the code-execution errors that may occur due to power-up, power-down, brownout conditions or other transients. The nRESET output is still in the correct logic state even if  $V_{CC}$  is lower than 1V. During power-up, when  $V_{CC}$  exceeds the rising threshold voltage ( $V_{nRST} + V_{HYS}$ ), an internal timer keeps nRESET in low state for the reset timeout period ( $t_{RP}$ ) before nRESET returns to the high state (Figure 3).

If  $V_{CC}$  drops below the falling threshold voltage ( $V_{nRST}$ ) (a brownout condition occurs), a reset is asserted and nRESET goes low. In general, nRESET remains low for the  $t_{RP}$  (260ms, TYP) period every time after the last event. So, if during the low period of nRESET,  $V_{CC}$  goes up and dips below  $V_{nRST}$  again, the internal timer will restart for a new  $t_{RP}$  period. The nRESET output can source and sink current.

Figure 3. nRESET Timing Diagram

#### **Manual Reset Input**

Many µP-based products need manual-reset capability to let the operator or an external logic reset the µP. For the SGM823S, applying a logic low to the nMR input, asserts a reset (nRESET = low). nRESET remains low while nMR is low, and will stay low for the  $t_{RP}$  (260ms, TYP) period after nMR returns to high state. The nMR input is internally pulled up by a  $60k\Omega$  resistor and can be left floating if not used. It can be driven by a CMOS/TTL logic or by a switch shorting to GND. A normally open momentary switch connected between nMR and GND pins can be used as a manual reset. Switch debouncing is not needed. However, if long cables are used to drive the nMR input or if the environment is noisy, connect a 0.1µF capacitor between nMR and GND to immune the additional noise.

#### Watchdog Input

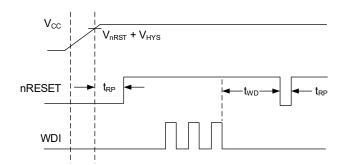

The internal watchdog circuit monitors the  $\mu P$ 's activity by checking the WDI input. If the  $\mu P$  does not toggle the WDI within the watchdog  $t_{WD}$  (2s, TYP) period, nRESET will send a low pulse to reset the  $\mu P$ . So, the code should be written such that successive toggles on WDI occur in periods not longer than the lowest  $t_{WD}$  time to reset the internal watchdog timer and prevent  $\mu P$  reset when the code is running normally. The watchdog timer is cleared by either toggling WDI or by a pulse with a duration as short as 90ns. While the reset is asserted and nRESET is low, the watchdog timer is cleared and timer does not count. It starts counting when the reset is released and nRESET goes high (Figure 4).

To disable the watchdog function, leave the WDI pin open. If WDI is driven by a 3-state buffer, set it to the Hi-Z state. In this case the buffer leakage current should not exceed 10µA. The maximum capacitance seen on the WDI pin should be less than 200pF to assure that watchdog remains disabled. The watchdog input is internally oscillating when it is left open to clear the watchdog timer and prevent it from generating a reset. It is driven low during the first 7/8 of the watchdog timeout period and driven high in the last 1/8 of that. For example if WDI input is open and the watchdog timeout is 2s, the watchdog timer will automatically clear every 1.75s and reset will not occur.

Figure 4. Watchdog Timing Relationship

#### APPLICATION INFORMATION

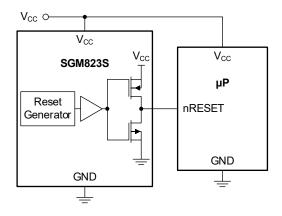

# Using SGM823S with Microprocessors with Bidirectional Reset Pins

Some microprocessors can internally force their reset pins low to assert a reset (bidirectional reset pins). The low pull-up current of the SGM823S allows using of them along with the microprocessors with bidirectional resets like the 68HC11. The microprocessor can force nRESET low when nRESET is pulled high by the SGM823S with no issues (Figure 5).

Figure 5. Interfacing to µP with Bidirectional Resets

#### **Negative-Going Vcc Transient Immunity**

The SGM823S has the ability to immune short time and negative  $V_{\text{CC}}$  transients or even glitches. It does not need to shut down the entire system. Resets are applied to the microprocessor during power-up, power-down and brownout conditions and not when an insignificant  $V_{\text{CC}}$  transient occurs.

A 0.1 $\mu F$  ceramic capacitor is recommended between the  $V_{CC}$  and GND pin to reduce the input supply noise.

#### **Watchdog Input Current**

The WDI input is internally driven by a buffer and series resistor from an internal counter chain stage of the watchdog. Therefore, when WDI is open, the watchdog timer is automatically cleared before timeout (by an internal low-high-low pulse).

To get the minimum WDI input current (minimum power loss), keep WDI low for the majority of the timeout period and send a high pulse at the first 7/8 of the timeout period for clearing the watchdog timer.

#### **Watchdog Software Considerations**

To have a more effective watchdog in software monitoring, rather than generating pulses by a code segment, set and reset the WDI input at different points of the program code. For example, set it in the main program and reset it in a periodic timing interrupt. For example if WDI is toggled within an unwanted infinite loop, it will continuously reset watchdog as a normal condition and the processor is not reset.

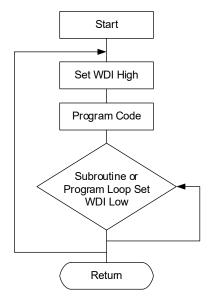

An example of a watchdog flow is shown in Figure 6. The WDI is set high at the start of the program, and is set low at the start of every subroutine or loop, then is set high again when the program returns to the start. If the processor hangs in any subroutine, the WDI toggling will not occur and the watchdog will reset the processor and correct the situation.

The nRESET output may also be connected to an interrupt input of the  $\mu P$  for a corrective action if preferred.

Note that such watchdog control schemes may not be optimal if the total power consumption is critical as discussed in the watchdog input current section.

Figure 6. Watchdog Flow Diagram

# Microprocessor Supervisory Circuit with Watchdog Timer and Manual Reset

# **SGM823S**

# **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| JULY 2025 – REV.A.1 to REV.A.2                      | Page |

|-----------------------------------------------------|------|

| Updated Package/Ordering Information section        |      |

| Changed Electrical Characteristics section          | 4    |

| Updated Typical Performance Characteristics section | 5, 6 |

|                                                     |      |

| OCTOBER 2023 – REV.A to REV.A.1                     | Page |

| Updated Package/Ordering Information section        | 2    |

| Changed Electrical Characteristics section          | 4, 5 |

| Changes from Original (AUGUST 2023) to REV.A        | Page |

| Changed from product preview to production data     | All  |

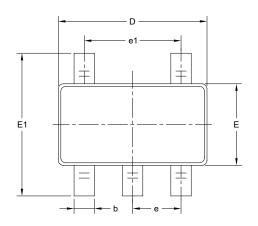

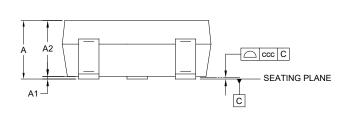

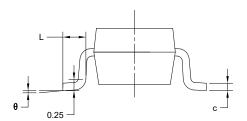

# PACKAGE OUTLINE DIMENSIONS SOT-23-5

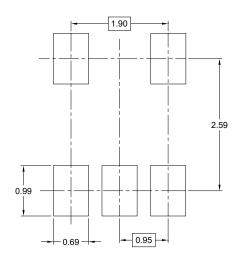

RECOMMENDED LAND PATTERN (Unit: mm)

| Cymphal | Dimensions In Millimeters |            |       |  |  |  |  |

|---------|---------------------------|------------|-------|--|--|--|--|

| Symbol  | MIN                       | MOD        | MAX   |  |  |  |  |

| Α       | -                         |            |       |  |  |  |  |

| A1      | 0.000                     | -          | 0.150 |  |  |  |  |

| A2      | 0.900                     | -          | 1.300 |  |  |  |  |

| b       | 0.300                     | 0.300 -    |       |  |  |  |  |

| С       | 0.080 -                   |            | 0.220 |  |  |  |  |

| D       | 2.750                     | -          | 3.050 |  |  |  |  |

| Е       | 1.450                     | 1.450 -    |       |  |  |  |  |

| E1      | 2.600                     | 2.600 - 3. |       |  |  |  |  |

| е       | 0.950 BSC                 |            |       |  |  |  |  |

| e1      | 1.900 BSC                 |            |       |  |  |  |  |

| L       | 0.300                     | -          | 0.600 |  |  |  |  |

| θ       | 0°                        | -          | 8°    |  |  |  |  |

| ccc     | 0.100                     |            |       |  |  |  |  |

#### NOTES:

- 1. This drawing is subject to change without notice.

- 2. The dimensions do not include mold flashes, protrusions or gate burrs.

- 3. Reference JEDEC MO-178.

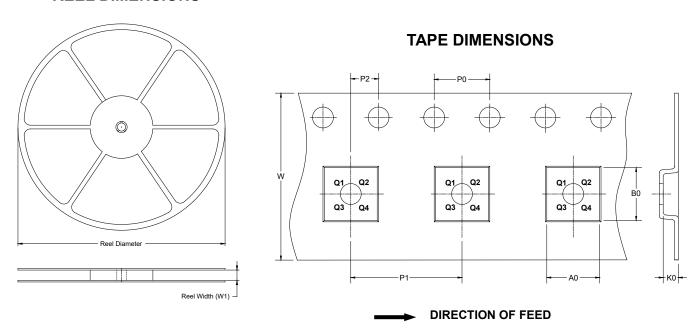

# TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| SOT-23-5     | 7"               | 9.5                      | 3.20       | 3.20       | 1.40       | 4.0        | 4.0        | 2.0        | 8.0       | Q3               |

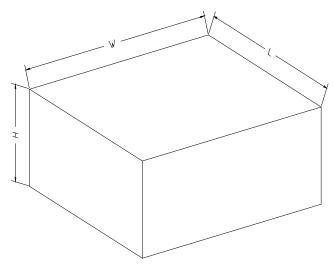

#### **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type   | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |

|-------------|----------------|---------------|----------------|--------------|

| 7" (Option) | 368            | 227           | 224            | 8            |

| 7"          | 442            | 410           | 224            | 18           |